时钟偏斜(clock skew)

时钟偏斜(偏移)是因为布线长度和负载不同,导致同一时钟上升沿到不同触发器的时间不同。这一时间差,即为时钟偏移。

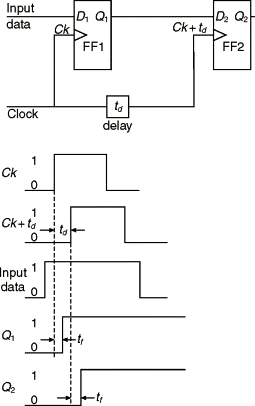

时钟偏斜可能导致时序违例(本文直接粘贴了参考博客中的示意图)

可以看出,同一时钟上升沿,到达D1和D2的时间不同。

如果时钟倾斜变大,可能导致保持时间不满足,导致保持时间违例;(数据传输时间不变,本来满足STA分析,不会出现问题。但是时钟倾斜变大,当前时钟上升沿来临变晚,导致保持时间不在满足)

如果时钟倾斜变小,可能导致建立时间不满足,即建立时间违例。(数据传输时间不变,本来满足STA分析,不会出现问题。但是时钟倾斜变小,下一时钟上升沿来临变早,导致建立时间不在满足)

时钟抖动(clock Jitter)

时钟抖动是指同一时钟,相邻周期间时间不一致的现象。这一误差来源于时钟自身(如:晶振、PLL电路的偏差),与噪声、干扰以及电源变化有关。(抖动还可能出现在同一周期间,表现为占空比的改变,称为半周期抖动),综上:可以认为时钟抖动是时钟信号本身在传输过程中的一些偶然和不定的变化之总和。

时钟抖动可能导致时序违例。

可以看出,时钟抖动可能导致时钟上升沿比期望值来的更早或更晚。

更早可能导致建立时间不满足,导致建立时间违例;更晚可能导致保持时间不满足,导致保持时间违例。

信号完整性

信号完整性对时序产生影响:

- 串扰会影响微带线传播延迟;

- 反射会造成数据信号在逻辑门限附近波动,从而影响最大/最小飞行时间;

- 时钟走线的干扰会造成一定的时钟偏移。

有些误差或不确定因素是仿真中无法预见的,设计者只有通过周密的思考和实际经验的积累来逐步提高系统设计的水平。

参考

数字电路时钟问题――Jitter与Skew区别