НёЬьИјДѓЯРДјРДЛљгкFPGAЕФ UART ПижЦЦїЩшМЦЃЈVHDLЃЉЃЈжаЃЉЃЌгЩгкЦЊЗљНЯГЄЃЌЗжШ§ЦЊЁЃНёЬьДјРДЕкЖўЦЊЃЌжаЦЊЃЌRS-232 ДЎПкЭЈаХМђНщЁЃЛАВЛЖрЫЕЃЌЩЯЛѕЁЃ

жЎЧАгаЙигк Veriliog HDL ЪЕЯжЕФ UART ПижЦЦїЩшМЦЃЌетРяЗХЩЯГЌСДНгЃЌНіЙЉИїЮЛДѓЯРВЮПМЁЃ

FPGAСуЛљДЁбЇЯАЃКUARTавщЧ§ЖЏЩшМЦ

дДТыЯЕСаЃКЛљгкFPGAЕФДЎПкUARTЩшМЦЃЈИНдДЙЄГЬЃЉ

ЕМЖС

вьВНДЎааЭЈаХЪЧжИUARTЃЈUniversal Asynchronous Receiver/TransmitterЃЉЃЌЭЈгУвьВННгЪе/ЗЂЫЭЁЃUARTЪЧвЛИіВЂааЪфШыГЩЮЊДЎааЪфГіЕФаОЦЌЃЌЭЈГЃМЏГЩдкжїАхЩЯЁЃUARTАќКЌTTLЕчЦНЕФДЎПкКЭRS232ЕчЦНЕФДЎПкЁЃRS232вВГЦБъзМДЎПкЃЌвВЪЧзюГЃгУЕФвЛжжДЎааЭЈбЖНгПкЁЃRS-232-C БъзМЖдСНИіЗНУцзїСЫЙцЖЈЃЌМДаХКХЕчЦНБъзМКЭПижЦаХКХЯпЕФЖЈвхЁЃRS-232ЃC ВЩгУИКТпМЙцЖЈТпМЕчЦНЃЌаХКХЕчЦНгыЭЈГЃЕФTTLЕчЦНвВВЛМцШнЃЌRS-232-C НЋ-5VЁЋ-15V ЙцЖЈЮЊЁА1ЁБЃЌ+5VЁЋ+15V ЙцЖЈЮЊЁА0ЁБЁЃ

вЛАуЧщПіЯТЭтЩшВЛФмжБНгКЭжїЛњжБНгЯрСЌЃЌЫќУЧжЎМфЕФаХЯЂНЛЛЛжївЊДцдквдЯТЮЪЬтЃК

? ЫйЖШВЛЦЅХф ЭЈГЃЧщПіЯТЭтЩшЕФЙЄзїЫйЖШЛсБШжїЛњТ§аэЖрЃЌЖјЧвЭтЩшжЎМфЕФЫйЖШВювьвВБШНЯДѓЁЃ

? Ъ§ОнИёЪНВЛЦЅХф ВЛЭЌЕФЭтЩшдкНјаааХЯЂДцДЂКЭДІРэЪБЕФЪ§ОнЕЅдЊПЩФмВЛЭЌЃЌР§ШчзюЛљБОЕФЪ§ОнИёЪНПЩвдЗжЮЊВЂааЪ§ОнКЭДЎааЪ§ОнЁЃ

? аХЯЂРраЭВЛЦЅХф ВЛЭЌЕФЭтЩшПЩФмВЩгУВЛЭЌРраЭЕФаХКХЃЌгааЉЪЧФЃФтаХКХЃЌгааЉЪЧЪ§зжаХКХЃЌвђДЫЫљВЩгУЕФДІРэЗНЪНвВВЛЭЌЁЃ

ЮЊСЫНтОіЭтЩшКЭжїЛњжЎМфаХЯЂНЛЛЛЕФЮЪЬтЃЌОЭашвЊЩшМЦвЛИіаХЯЂНЛЛЛЕФжаМфЛЗНкЁЊЁЊНгПкЁЃБОЦЊНЋЪзЯШЖдНгПкММЪѕНјааМђвЊЕФНщЩмЃЌШЛКѓвдНгПкжазюГЃгУЕФ UART ПижЦЦїЮЊР§ЃЌЯъЯИНщЩмгУ FPGA ЪЕЯж UART ПижЦЦїЕФЗНЗЈЁЃ

ЕкЖўЦЊФкШнеЊвЊЃКБОЦЊНщЩмRS-232 ДЎПкЭЈаХМђНщ ЃЌАќРЈДЎПкЭЈаХИХЪіавщ ЁЂRS-232 ЭЈаХЪБађКЭ UARTвдМАДЎПкЭЈаХЪЕЯжЗНАИЕШЯрЙиФкШнЁЃ

ЖўЁЂRS-232 ДЎПкЭЈаХМђНщ

2.1 ДЎПкЭЈаХИХЪі

дкЪ§ОнЭЈаХЁЂМЦЫуЛњЭјТчвдМАЗжВМЪНЙЄвЕПижЦЯЕЭГжаЃЌОГЃВЩгУДЎааЭЈаХРДНЛЛЛЪ§ОнКЭаХЯЂЁЃ1969 ФъЃЌУРЙњЕчзгЙЄвЕаЛсЃЈEIAЃЉНЋ RS-232CЃЈМђГЦ RS-232ЃЉЖЈЮЊДЎааЭЈаХНгПкЕФЕчЦјБъзМЃЌИУБъзМЖЈвхСЫЪ§ОнжеЖЫЩшБИЃЈDTEЃЉКЭЪ§ОнЭЈаХЩшБИЃЈDCEЃЉМфАДЮЛДЎааДЋЪфЕФНгПкаХЯЂЃЌКЯРэАВХХСЫНгПкЕФЕчЦјаХКХКЭЛњаЕвЊЧѓЃЌЪЪКЯгкЪ§ОнДЋЪфЫйТЪдк 0~20000bit/s ЗЖЮЇФкЕФЭЈаХЁЃRS-232 зїЮЊвЛжжБъзМНгПкЃЌВЛНіБЛФкжУгкУПвЛЬЈМЦЫуЛњжаЃЌЭЌЪБвВБЛФкжУгкИїжжЭтЩшжаЁЃ

RS-232 ОпгавдЯТМИИігХЕуЃК

? ЪЙгУЙуЗКЃЌМИКѕУПвЛЬЈ PC ЖМЛсгавЛИіЛђепЖрИі RS-232 НгПкЃЛ

? СЌНгОрРыПЩДяЕН 15mЃЛ

? ЪЕЯжМђЕЅЃЌRS-232 гУгкЫЋЯђСЌНгЃЌжЛашвЊ 3 ЬѕЕМЯпЁЃ

Г§СЫ RS-232 БъзМЃЌУРЙњЕчзгЙЄвЕаЛсЃЈEIAЃЉЛЙжЦЖЈСЫ RS-422 гы RS-485 БъзМЁЃRS-422гЩ RS-232 ЗЂеЙЖјРДЃЌЫќЪЧЮЊУжВЙ RS-232 жЎВЛзуЖјЬсГіЕФЁЃRS-422 ЖЈвхСЫвЛжжЦНКтЭЈаХНгПкЃЌНЋДЋЪфЫйТЪЬсИпЕН 10Mbit/sЃЌДЋЪфОрРыбгГЄЕН 4000 гЂГпЃЈЫйТЪЕЭгк 100kbit/s ЪБЃЉЃЌВЂдЪаэдквЛЬѕЦНКтзмЯпЩЯСЌНгзюЖр 10 ИіНгЪеЦїЁЃ

RS-422 ЪЧвЛжжЕЅЛњЗЂЫЭЁЂЖрЛњНгЪеЕФЕЅЯђЁЂЦНКтДЋЪфЙцЗЖЃЌБЛУќУћЮЊ TIA/EIA-422-A БъзМЁЃЮЊРЉеЙгІгУЗЖЮЇЃЌEIA гжгк 1983 Фъдк RS-422 ЛљДЁЩЯжЦЖЈСЫ RS-485 БъзМЃЌдіМгСЫЖрЕуЁЂЫЋЯђЭЈаХФмСІЃЌМДдЪаэЖрИіЗЂЫЭЦїСЌНгЕНЭЌвЛЬѕзмЯпЩЯЃЌЭЌЪБдіМгСЫЗЂЫЭЦїЕФЧ§ЖЏФмСІКЭГхЭЛБЃЛЄЬиадЃЌРЉеЙСЫзмЯпЙВФЃЗЖЮЇЃЌУќУћЮЊ TIA/EIA-485-AБъзМЁЃ

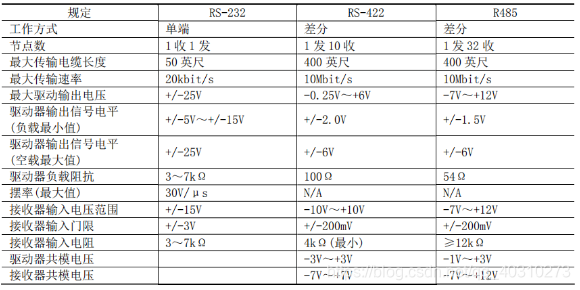

гЩгк EIA ЬсГіЕФНЈвщБъзМЖМЪЧвдЁАRSЁБзїЮЊЧАзКЃЌЫљвддкЭЈаХЙЄвЕСьгђЃЌШдШЛЯАЙпНЋЩЯЪіБъзМвд RS зїЧАзКГЦЮНЁЃRS-232ЁЂRS-422 гы RS-485 ЕФЕчЦјВЮЪ§ШчБэ 2 ЫљЪОЁЃ

Бэ 2 RS-232ЁЂRS-422 гы RS-485 ЕФЕчЦјВЮЪ§Бэ

ЫфШЛ RS-232ЁЂRS-422 гы RS-485 БъзМЖдНгПкЕФЕчЦјЬиадзіГіСЫЙцЖЈЃЌЕЋЪЧУЛгаЙцЖЈСЌНгВхМўЁЂЕчРТЛђавщЃЌЫљвддкДЫЛљДЁЩЯгУЛЇПЩвдНЈСЂздМКЕФИпВуЭЈаХавщЁЃRS-232 ЕШавщдкЪгЦЕДЋЪфжаБЛЙуЗКгІгУЃЌаэЖрГЇМвЖМНЈСЂСЫвЛЬзИпВуЭЈаХавщЃЌЛђЙЋПЊЛђГЇМвЖРМвЪЙгУЁЃШчТМЯёЛњЩЬМвжаЕФ Sony гыЫЩЯТЖдТМЯёЛњЕФ RS-422 ПижЦавщЪЧгаВювьЕФЃЌЪгЦЕЗўЮёЦїЩЯЕФПижЦавщдђИќЖрСЫЃЌШч LouthЁЂOdetis авщЪЧЙЋПЊЕФЃЌЖј ProLINK дђЪЧЛљгк Profile ЩЯЕФЁЃ

ФПЧАЃЌRS-232 ЪЧ PC ЛњгыЭЈаХЙЄвЕжагІгУзюЙуЗКЕФвЛжжДЎааНгПкЃЌБОЦЊКѓСНЦЊОЭЯъЯИНщЩмвЛЯТ RS-232 авщЕФФкШнКЭЪЙгУ FPGA ПЊЗЂ RS-232 НгПкЕФЗНЗЈЁЃ

2.2 RS-232 авщ

БъзМЕФ RS-232 НгПкга 25 ИљаХКХЯпЃЌЦфжага 4 ИљЪ§ОнЯпЁЂ11 ИљПижЦЯпЁЂ3 ИљЖЈЪБЯпКЭ 7ИљБИгУЯпЁЃЭЈГЃЧщПіЯТЃЌЪЙгУ 25 ИљаХКХЯпжаЕФ 9 ИљОЭПЩвдЪЕЯж RS-232 ЭЈаХЁЃ

1ЃЉDSR аХКХЯп

DSRЃЈData Set ReadyЃЉвтЫМЮЊЪ§ОнзАжУОЭаїЃЌЕБЦфзДЬЌЮЊгааЇЪБЃЌБэУї Modem ДІгкПЩвдЪЙгУЕФзДЬЌЁЃ

зЂвтЃКModem ЪЧ Modulator/DEModulator ЕФЫѕаДЃЌжаЮФУћГЦЪЧЕїжЦНтЕїЦїЁЃModem ЪЧвЛжждкЗЂЫЭЖЫЭЈЙ§ЕїжЦНЋЪ§зжаХКХзЊЛЛЮЊФЃФтаХКХЃЌЖјдкНгЪеЖЫЭЈЙ§НтЕїдйНЋФЃФтаХКХзЊЛЛЮЊЪ§зжаХКХЕФЩшБИЁЃ

2ЃЉDTR аХКХЯп

DTRЃЈData Terminal ReadyЃЉвтЫМЮЊЪ§ОнжеЖЫОЭаїЃЌЕБЦфзДЬЌЮЊгааЇЪБЃЌБэУїЪ§ОнжеЖЫПЩвдЪЙгУЁЃ

3ЃЉRTS аХКХЯп

RTSЃЈRequest To SendЃЉвтЫМЮЊЧыЧѓЗЂЫЭЃЌМДЕБжеЖЫашвЊЗЂЫЭЪ§ОнЪБЃЌЪЙИУаХКХгааЇЃЌЯђModem ЧыЧѓЗЂЫЭЁЃЫќгУгкПижЦ Modem ЪЧЗёНјШыЗЂЫЭзДЬЌЁЃ

4ЃЉCTS аХКХЯп

CTSЃЈClear To SendЃЉвтЫМЮЊдЪаэЗЂЫЭЃЌетИіаХКХЪЧЖд RTS аХКХЕФЯьгІЁЃЕБ Modem вбОзМБИКУНгЪежеЖЫЗЂЫЭЙ§РДЕФЪ§ОнЪБЃЌЪЙИУаХКХгааЇЃЌЭЈжЊжеЖЫПЊЪМЗЂЫЭЪ§ОнЁЃ

5ЃЉDCD аХКХЯп

DCDЃЈData Carrier DetectionЃЉвтЫМЮЊЪ§ОндиВЈМьГіЃЌЕБДЫаХКХЮЊгааЇЪББэЪО Modem вбОНгЭЈСЫЭЈаХСДТЗЃЌМДБОЕи Modem ЪеЕНСЫЭЈаХСДТЗСэвЛЖЫЕФдЖГЬ Modem ЫЭРДЕФдиВЈаХКХЃЌжеЖЫПЩвдзМБИНгЪеЪ§ОнЁЃ

6ЃЉRI аХКХЯп

RIЃЈRingingЃЉвтЫМЮЊеёСхжИЪОЃЌЕББОЕи Modem ЪеЕННЛЛЛЬЈЗЂЫЭЕФеёСхКєНааХКХЪБЃЌЪЙИУаХКХгааЇЃЌЭЈжЊжеЖЫвбБЛКєНаЁЃ

7ЃЉTxD аХКХЯп

TxDЃЈTransmitted DataЃЉвтЫМЪЧЗЂЫЭЪ§ОнЃЌжеЖЫЭЈЙ§ДЫаХКХЯпНЋЪ§ОнЗЂЫЭИј ModemЁЃ

8ЃЉRxD аХКХЯп

RxDЃЈReceived DataЃЉвтЫМЪЧНгЪеЪ§ОнЃЌжеЖЫЭЈЙ§ДЫаХКХЯпДг Modem НгЪеЪ§ОнЁЃ

9ЃЉЕиЯп

ЕиЯпгаСНИљЃЌЗжБ№ЪЧаХКХЕи SGЃЈSignal GroundЃЉКЭБЃЛЄЕи PEЃЈProtection GroundЃЉЃЌаХКХЕиЪЧЫљгааХКХЕФВЮПМЕчЦНЃЌБЃЛЄЕигУгкСЌНгЩшБИЭтПЧЛђепЕиБэЁЃ

ГЃМћЕФ RS-232 ДЎааПкСЌНгЦїжївЊгаСНжжЃЌвЛжжЪЧ 25 еыЕФ DB-25ЃЌСэвЛжжЪЧ 9 еыЕФ DB-9ЃЌЦфЪОвтЭМШчЭМ 1 ЫљЪОЁЃ

ЭМ 1 RS-232 ДЎааПкСЌНгЦїЪОвтЭМ

Цфжа DB-9 жївЊгУгкЩЯЪіЕФ 9 ИљаХКХЯпСЌНгЕФЗНЗЈЃЌDB-25 ПЩвдСЌНгЫљга RS-232 БъзМЖЈвхЕФаХКХЯпЁЃDB-25 вВПЩгУЯё DB-9 ФЧбљЪЙгУЃЌЕЋЪЧЫќУЧЕФеыКХгыаХКХжЎМфЕФЯпСЌНгЙиЯЕЪЧВЛвЛбљЕФЃЌШчБэ 3 ЫљЪОЁЃ

Бэ 3 DB-25ЁЂDB-9 еыКХаХКХЯпСЌНгЖдгІБэ

зюЮЊМђЕЅЧвГЃгУЕФ RS-232 СЌНгЗНЗЈЪЧШ§ЯпСЌНгЗЈЃЌМДЕиЁЂНгЪеЪ§ОнКЭЗЂЫЭЪ§ОнШ§НХЯрСЌЁЃЖдгкЩЯЪіЕФ DB-25 СЌНгЦїКЭ DB-9 СЌНгЦїЃЌШ§ЯпСЌНгЗЈЕФддђШчБэ 4 ЫљЪОЁЃ

Бэ 4 DB-25ЁЂDB-9 Ш§ЯпСЌНгЗЈ

дкЕчЦјЬиадЗНУцЃЌБъзМ RS-232 НгПкгаШчЯТЙцЖЈЃК

? ЖдгкЪ§ОнДЋЪфЯп RxD КЭ TxDЃЌТпМЁА1ЁБЖдгІЕФЕчЦНЪЧ-15VЁЋ-3VЃЌТпМЁА0ЁБЖдгІЕФЕчЦНЪЧ+3V~+15VЁЃ

? Ждгк RTSЁЂCTSЁЂDSRЁЂDTRЁЂDCD ЕШаХКХЯпЃЌаХКХгааЇЪБЖдгІаХКХЯпЩЯЮЊе§ЕчбЙ+3VЁЋ+15VЃЌЗДжЎдђЪЧИКЕчбЙ-15VЁЋ-3VЁЃ

гЩгк RS-232 ЕчЦјЬиЖЈЙцЖЈЕФЕчЦНВЛЗћКЯЭЈГЃЕчТЗжаЫљЪЙгУЕФ TTL Лђеп CMOS ЕчЦНЃЌЫљвддкНгШыЕчТЗжЎЧАашвЊЖдЦфНјаазЊЛЛЁЃRS-232 ДЎПкЕчЦНЕФзЊЛЛвЛАуЪЧЪЙгУзЈУХЕФаОЦЌЪЕЯжЕФЃЌЦфжаЮЊзюГЃгУЕФОЭЪЧУРаХЃЈMAXIMЃЉЙЋЫОЕФ MAX232ЁЃ

MAX232 ПЩвдНЋДЎПкЩшБИашвЊЗЂЫЭЕФ TTL/CMOSТпМЕчЦНзЊЛЛЮЊ RS-232 ТпМЕчЦНЃЌЭЌЪБвВПЩвдНЋвЊНгЪеЕФ RS-232 ТпМЕчЦНзЊЛЛЮЊ TTL/CMOSЕчЦНЃЌЭМ 2 ЫљЪООЭЪЧ MAX232 аОЦЌЕФЖЅВуЭМЁЃMAX232 ПЩЬсЙЉ DIP/SO/TSSOP 3 жжЗтзАЃЌПЩвдТњзуВЛЭЌЕФЩшМЦашЧѓЁЃ

ЭМ 2 MAX232 аОЦЌЕФЖЅВуЭМ

MAX232 ЕФЕфаЭСЌНгЗНЗЈШчЭМ 3 ЫљЪОЃЌЦфжага 5 Иі 0.1ІЬ ЕФШЅёюЕчШнЃЛ11 ЙмНХКЭ 10 ЙмНХЪЧ TTL/CMOS ЕчЦНЪфШыЃЌЖдгІ 14 ЙмНХКЭ 7 ЙмНХЕФ RS-232 ЕчЦНЪфГіЃЌЫќУЧвЛАуНгЕН RS-232 ЕФRxD ЩЯЃЛ12 ЙмНХКЭ 9 ЙмНХЪЧ TTL/CMOS ЕчЦНЪфГіЃЌЖдгІ 13 ЙмНХКЭ 8 ЙмНХЕФ RS-232 ЕчЦНЪфШыЃЌЫќУЧвЛАуНгЕН RS-232 ЕФ TxD ЩЯЁЃ

ЭМ 3 MAX232 ЕфаЭСЌНгЪОвтЭМ

2.3 RS-232 ЭЈаХЪБађКЭ UART

дкДЎааЭЈаХжаЃЌгУЁАВЈЬиТЪЁБРДУшЪіЪ§ОнЕФДЋЪфЫйТЪЁЃЫљЮНВЈЬиТЪЃЌМДУПУыжгДЋЫЭЕФЖўНјжЦЮЛЪ§ЃЌЦфЕЅЮЛЮЊ bit/sЃЈbits per secondЃЉЃЌЫќЪЧКтСПДЋЪфДЎааЪ§ОнЫйЖШПьТ§ЕФживЊжИБъЁЃгаЪБвВгУЁАЮЛжмЦкЁБРДБэЪОДЋЪфЫйТЪЃЌЮЛжмЦкЪЧВЈЬиТЪЕФЕЙЪ§ЁЃЙњМЪЩЯЙцЖЈСЫвЛИіБъзМВЈЬиТЪЯЕСаЃК110bit/sЁЂ300bit/sЁЂ600bit/sЁЂ1200bit/sЁЂ1800bit/sЁЂ2400bit/sЁЂ4800bit/sЁЂ9600bit/sЁЂ14.4kbit/sЁЂ19.2kbit/sЁЂ28.8kbit/sЁЂ33.6kbit/sЁЂ56kbit/sЁЃШч 9600bit/sЃЌЦфвтвхЪЧУПУыДЋЫЭ 9600 ЮЛЪ§ОнЃЌАќКЌзжЗћЮЛКЭЦфЫћБиаыЕФЮЛЃЌШчЦцХМаЃбщЮЛЁЂЦ№ЪМЮЛЁЂЭЃжЙЮЛЁЃ

ДѓЖрЪ§ДЎааНгПкЕчТЗЕФНгЪеВЈЬиТЪКЭЗЂЫЭВЈЬиТЪЖМПЩвдЩшжУЃЌЕЋНгЪеЗНЕФНгЪеВЈЬиТЪБиаыгыЗЂЫЭЗНЕФЗЂЫЭВЈЬиТЪЯрЭЌЁЃЭЈаХЯпЩЯЫљДЋЪфЕФзжЗћЪ§ОнЃЈДњТыЃЉЪЧж№ЮЛДЋЫЭЕФЃЌ1 ИізжЗћгЩШєИЩЮЛзщГЩЃЌвђДЫУПУыжгЫљДЋЪфЕФзжЗћЪ§ЃЈзжЗћЫйТЪЃЉКЭВЈЬиТЪЪЧСНжжИХФюЁЃдкДЎааЭЈаХжаЫљЫЕЕФДЋЪфЫйТЪЪЧжИВЈЬиТЪЃЌЖјВЛЪЧжИзжЗћЫйТЪЃЌМйШчдквьВНДЎааЭЈаХжаЃЌДЋЫЭвЛИізжЗћЃЌАќРЈ12 ЮЛЃЈЦфжагавЛИіЦ№ЪМЮЛЃЌ8 ИіЪ§ОнЮЛЃЌ2 ИіЭЃжЙЮЛЃЉЃЌЦфДЋЪфЫйТЪЪЧ 1200bit/sЃЌУПУыЫљФмДЋЫЭЕФзжЗћЪ§ЪЧ 1200/(1+8+1+2)=100 ИіЁЃ

дкДЎааЭЈаХжаЃЌГ§СЫПЩвдЩшжУВЈЬиТЪЭтЃЌЦфЫћЕФШчзжЗћЪ§ОнЕФЮЛЪ§ЁЂЦцХМаЃбщЮЛЁЂЭЃжЙЮЛвВПЩвдБЛЩшжУЁЃЦфжаЃЌзжЗћЪ§ОнЕФЮЛЪ§ПЩвдБЛЩшжУЮЊ 5~8 ЮЛЃЛЦцХМаЃбщЮЛПЩвдШЅГ§ЃЌвВПЩвдЩшжУЮЊЦцаЃбщЛђепХМаЃбщЃЛЭЃжЙЮЛПЩвдЩшжУЮЊ 1 ЮЛЁЂ1.5 ЮЛЛђеп 2 ЮЛЁЃ

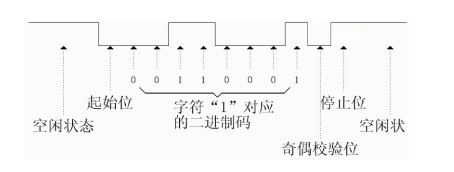

ЯТУцНщЩмвЛЯТДЎааЭЈаХЕФЪБађЁЃДЎаазмЯпдкПеЯаЪБКђБЃГжТпМЁА1ЁБзДЬЌЃЈМДДЎааСЌНгЯпЩЯЕФЕчЦНЮЊ-3V~-15VЃЉЃЌЕБашвЊДЋЫЭвЛИізжЗћЪБЃЌЪзЯШЛсЗЂЫЭвЛИіТпМЮЊЁА0ЁБЕФЦ№ЪМЮЛЃЌБэЪОПЊЪМЗЂЫЭЪ§ОнЃЛжЎКѓЃЌОЭж№ИіЗЂЫЭЪ§ОнЮЛЁЂЦцХМаЃбщЮЛКЭЭЃжЙЮЛЃЈТпМЮЊЁА1ЁБЃЉЁЃР§ШчЃЌЭЈЙ§RS-232 ДЎааЭЈаХЗЂЫЭвЛИізжЗћЁА1ЁБЃЈЖўНјжЦЮЊ 01100001ЃЉЃЌЩшжУЮЊ 8 ЮЛЪ§ОнЮЛЃЌ1 ЮЛЦцХМаЃбщЮЛЃЌ1 ЮЛЭЃжЙЮЛЃЌдђЗЂЫЭЪБађЭМШчЭМ 4 ЫљЪОЁЃ

ЭМ 4 RS-232 ДЎааПкЭЈаХЪБађЭМ

ЖдгквЛИіЩшБИЕФДІРэЦїРДЫЕЃЌвЊНгЪеКЭЗЂЫЭДЎааЭЈаХЕФЪ§ОнЃЌЛЙашвЊвЛИіЦїМўНЋДЎааЕФЪ§ОнзЊЛЛЮЊВЂааЪ§ОнвдБугкДІРэЦїНјааДІРэЃЌетИіЦїМўОЭЪЧ UARTЁЃUARTЃЈUniversal AsynchronousReceiver/TransmitterЃЉШЋГЦЪЧЭЈгУвьВНЪеЗЂЦїЃЌЦфЙІФмЪЧИЈжњДІРэЦїгыДЎааЩшБИжЎМфЕФЭЈаХЁЃ

зїЮЊ RS-232 ЭЈаХНгПкЕФвЛИіживЊВПЗжЃЌUART ОпгавдЯТЙІФмЃК

? НЋгЩМЦЫуЛњФкВПДЋЫЭЙ§РДЕФВЂааЪ§ОнзЊЛЛЮЊгУгкЪфГіЕФДЎааЪ§ОнСїЃЛ

? НЋМЦЫуЛњЭтВПДЋЕнРДЕФДЎааЪ§ОнзЊЛЛЮЊзжНкЃЌЙЉМЦЫуЛњФкВПЪЙгУВЂааЪ§ОнЕФЦїМўЪЙгУЃЛ? дкЪфГіЕФДЎааЪ§ОнСїжаМгШыЦцХМаЃбщЮЛЃЌВЂЖдДгЭтВПНгЪеЕФЪ§ОнСїНјааЦцХМаЃбщЃЛ

? дкЪфГіЪ§ОнСїжаМгШыЦєЭЃБъМЧЃЌВЂДгНгЪеЪ§ОнСїжаЩОГ§ЦєЭЃБъМЧЃЛ

? ЬсЙЉКЭДІРэЦїжЎМфЕФЭЈаХаХКХЃЌПЩвдДІРэДІРэЦїКЭДЎааЭЈаХЩшБИжЎМфЕФЭЌВНЙмРэЮЪЬтЁЃ

ЫцзХДІРэЦїЙІФмдНРДдНЧПЃЌФПЧАДѓВПЗжДІРэЦїжаЖММЏГЩСЫ UARTЃЌгУЛЇЕФЙЄзїНіНіЪЧИљОнашвЊЖдЦфНјааХфжУМДПЩЁЃ

2.4 ДЎПкЭЈаХЪЕЯжЗНАИ

ЪЕЯжДЎПкЭЈаХжївЊашвЊЭъГЩСНВПЗжЙЄзїЃК

ЃЈ1ЃЉНЋДЎПкЕчЦНзЊЛЛЮЊЩшБИЕчТЗАхЕФЙЄзїЕчЦНЃЌМДЪЕЯж RS-232 ЕчЦНКЭ TTL/CMOS ЕчЦНЕФзЊЛЛЃЛ

ЃЈ2ЃЉНгЪеВЂЧваЃбщДЎааЕФЪ§ОнЃЌНЋЪ§ОнБфГЩВЂааЕФВЂЬсЙЉИјДІРэЦїДІРэЁЃ

ЧАУцвбОНщЩмСЫЪЕЯж RS-232 ЕчЦНКЭ TTL/CMOS ЕчЦНзЊЛЛПЩвдгУНгПкаОЦЌЪЕЯжЃЌЪЕЯжЪ§ОнЕФДЎааЕНВЂаазЊЛЏгУЕФЪЧ UARTЃЌЫќУЧЪЧЪЕЯжДЎааЭЈаХБиВЛПЩЩйЕФСНИіВПЗжЁЃЫфШЛФПЧАДѓВПЗжДІРэЦїаОЦЌжаЖММЏГЩСЫ UARTЃЌЕЋЪЧвЛАу FPGA аОЦЌШДУЛгаетИіЬиЕуЃЌЫљвдЪЙгУ FPGA зїЮЊДІРэЦїПЩвдгаСНИібЁдёЃЌЕквЛИібЁдёЪЧЪЙгУ UART аОЦЌНјааДЎВЂзЊЛЛЃЌЕкЖўИібЁдёЪЧдк FPGA ФкВПЪЕЯж UART ЙІФмЁЃ

ЪЙгУ UART аОЦЌНјааДЎВЂзЊЛЛЕФгХЕуЪЧЩшМЦМђЕЅЃЌЕЋЪЧШДЛсЪЙЩшМЦЕФГЩБОдіМгВЂЧвдіМгЕчТЗАхЕФУцЛ§ЁЃбЁдёдк FPGA ЦЌЩЯЪЕЯж UART ФмЙЛНкЪЁГЩБОЃЌЕЋЪЧЛсеМгУвЛВПЗж FPGAЕФзЪдДЃЌШчЙћгавЛЖЈИЛгрЕФ FPGA зЪдДЃЌетЪЧвЛИіВЛДэЕФбЁдёЁЃБОЦЊЯТУцЕФФкШнНЋЯъЯИНщЩмЪЙгУ FPGA ЪЕЯж UART ЕФЫМТЗКЭВНжшЁЃ

БОЦЊЕНДЫНсЪјЃЌЯТвЛЦЊДјРДЛљгкFPGAЕФ UART ПижЦЦїЩшМЦЃЈVHDLЃЉЃЈЯТЃЉЃЌЪЙгУ FPGA ЪЕЯж UARTЃЌАќРЈUART ЪЕЯждРэЁЂUART ЙЄзїСїГЬЁЂаХКХМрВтЦїФЃПщЕФЪЕЯжЁЂВЈЬиТЪЗЂЩњЦїФЃПщЕФЪЕЯжЁЂвЦЮЛМФДцЦїФЃПщЕФЪЕЯжЁЂЦцХМаЃбщЦїФЃПщЕФЪЕЯжЁЂзмЯпбЁдёЦїФЃПщЕФЪЕЯжЁЂМЦЪ§ЦїФЃПщЕФЪЕЯжЁЂUART ФкКЫФЃПщЕФЪЕЯжЁЂUART ЖЅВуФЃПщЕФЪЕЯж ЁЂВтЪдЦНЬЈЕФБраДКЭЗТецЕШЯрЙиФкШнЁЃ

END

КѓајЛсГжајИќаТЃЌДјРДVivadoЁЂ ISEЁЂQuartus II ЁЂcandenceЕШАВзАЯрЙиЩшМЦНЬГЬЃЌбЇЯАзЪдДЁЂЯюФПзЪдДЁЂКУЮФЭЦМіЕШЃЌЯЃЭћДѓЯРГжајЙизЂЁЃ

ДѓЯРУЧЃЌНКўйМДѓЃЌМЬајДГЕДЃЌдИвЛЧаАВКУЃЌгадЕдйМћЃЁ

ОЋВЪЭЦМі

FPGAЙЋПЊПЮПЮМўМЏКЯ

VHDLгяЗЈбЇЯАБЪМЧЃКвЛЮФеЦЮеVHDLгяЗЈ

FPGAжЎЭЈаХЫуЗЈЙЄГЬЪІУцЪдЬт3

FPGAЙЄГЬЪІОЭвЕАрЃЌ9дТЗнПЊПЮЃЁ