理论部分

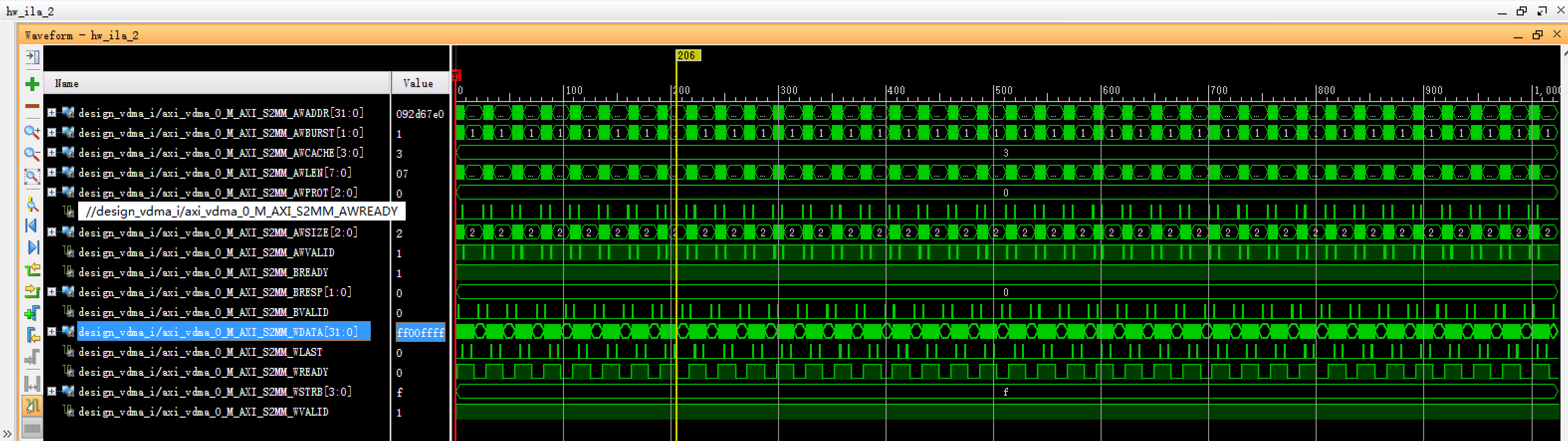

VDMA可以把AXI4-Stream 类型的视频流通过S2MM,写入到DDR3中,反之也可以通过MM2S读入到VDMA接口的外设中。通过内嵌FPGA逻辑分析仪进行观察数据。

本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:Vivado Design Suite 2015.2

硬件系统工程

新建一个zedboard工程

建好工程后,再新建一个Block Design

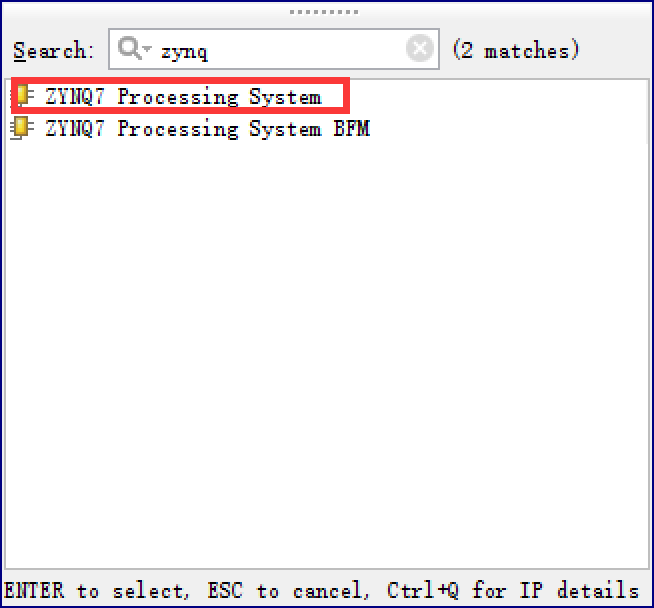

点击ADD IP,添加ZYNQ PS

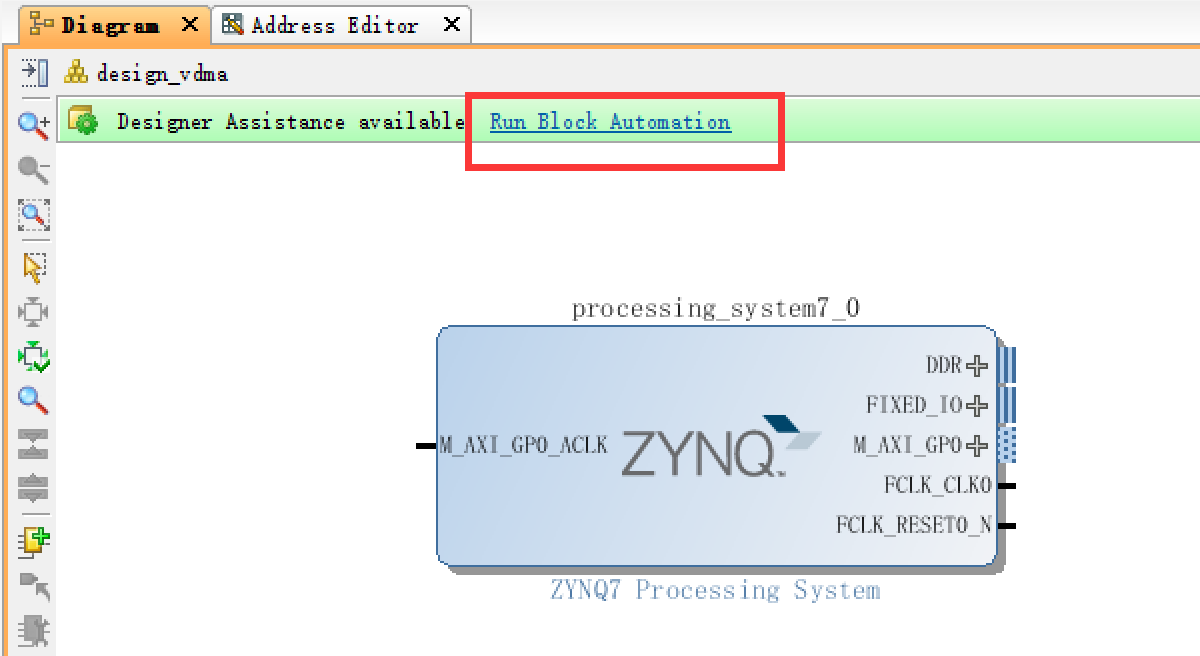

点击Run Block Automation,在弹出的对话框点击OK

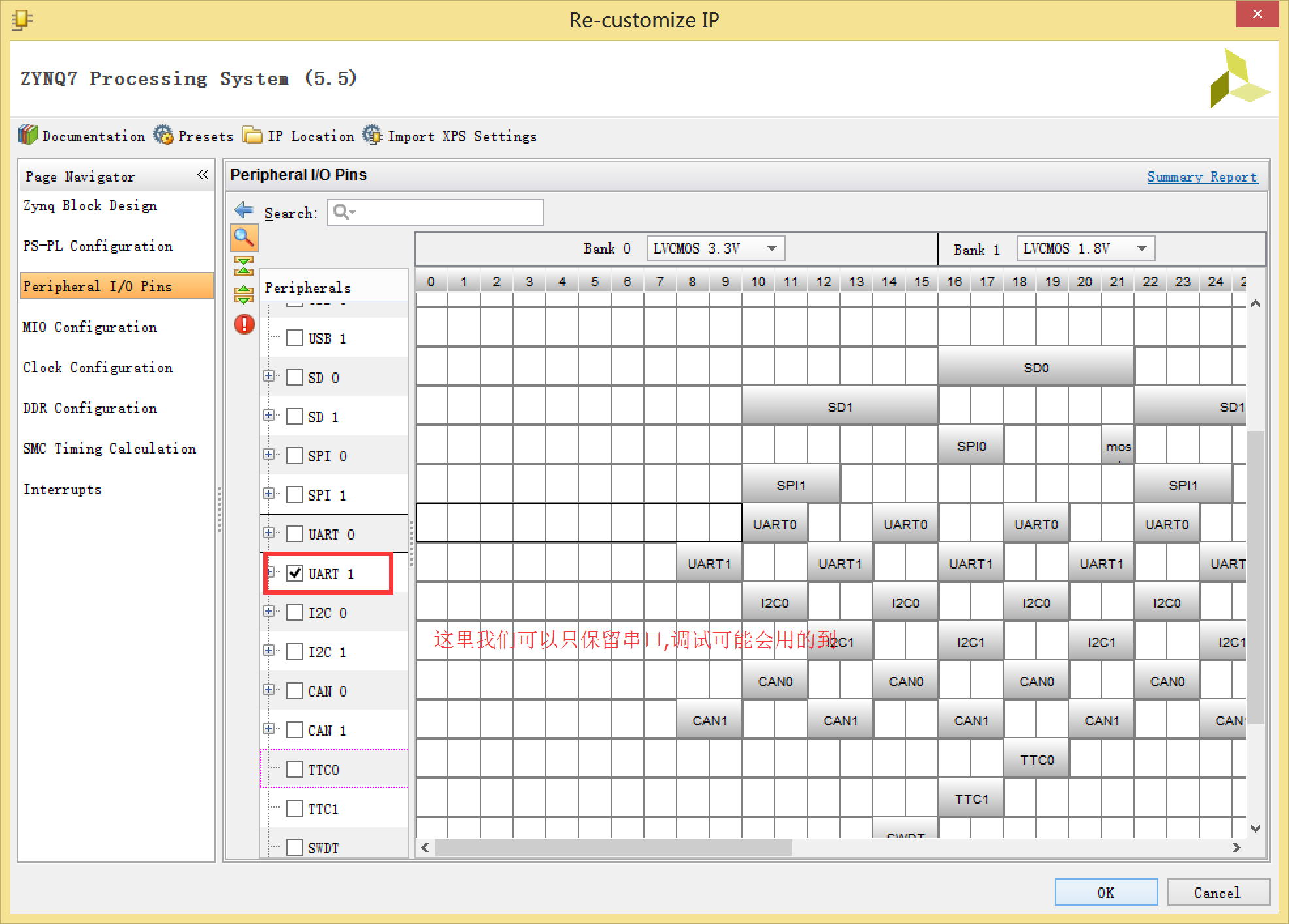

双击ZYNQ图标,去掉不用的外设

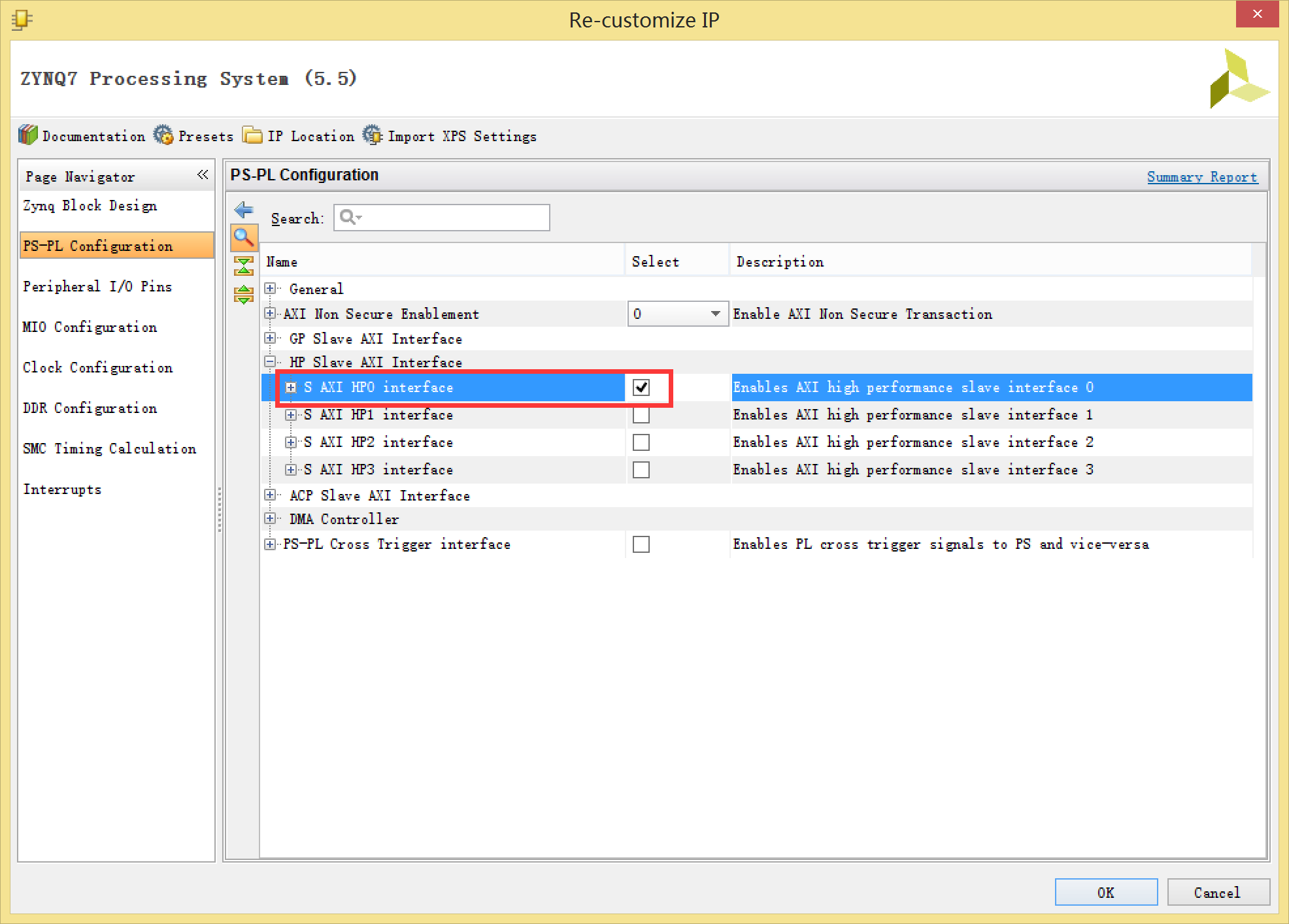

使能一个HP接口,PL和PS通过VDMA传输数据做准备

设置好后,点击OK

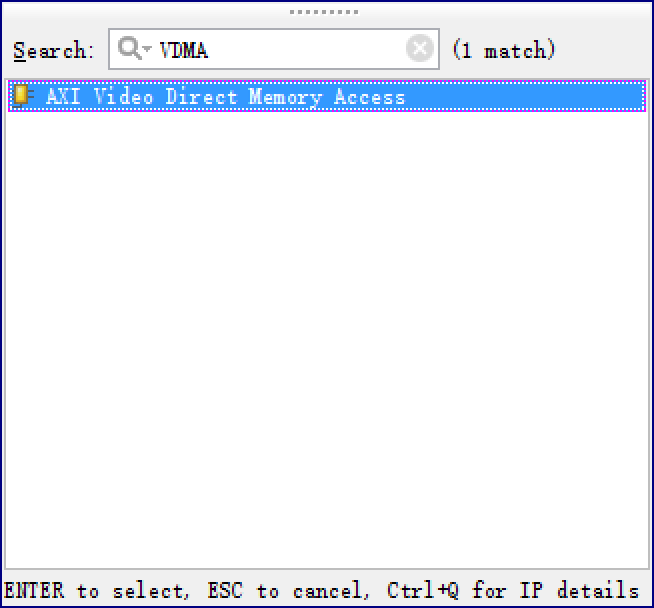

添加VDMA IP Core

点击Run Connection Automation

在弹出的对话框的左上角选择All…,点击OK

再次点击Run Connection Automation

在弹出的对话框的左上角选择All…,点击OK,然后重新生成布局

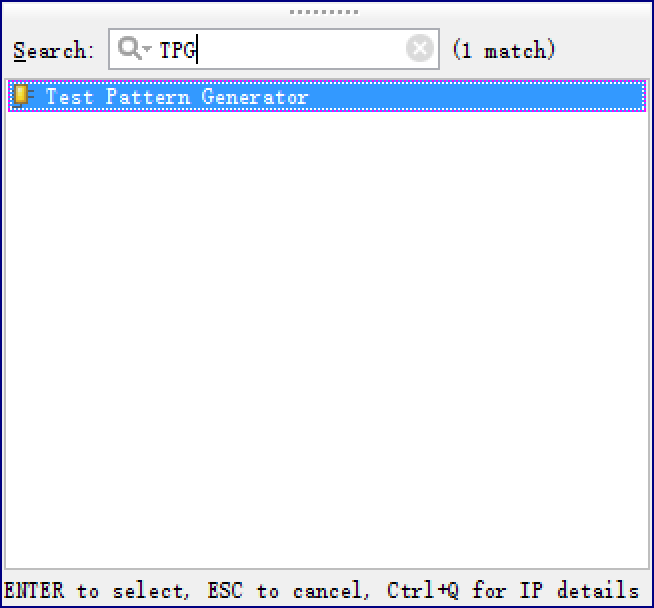

添加TPG IP Core

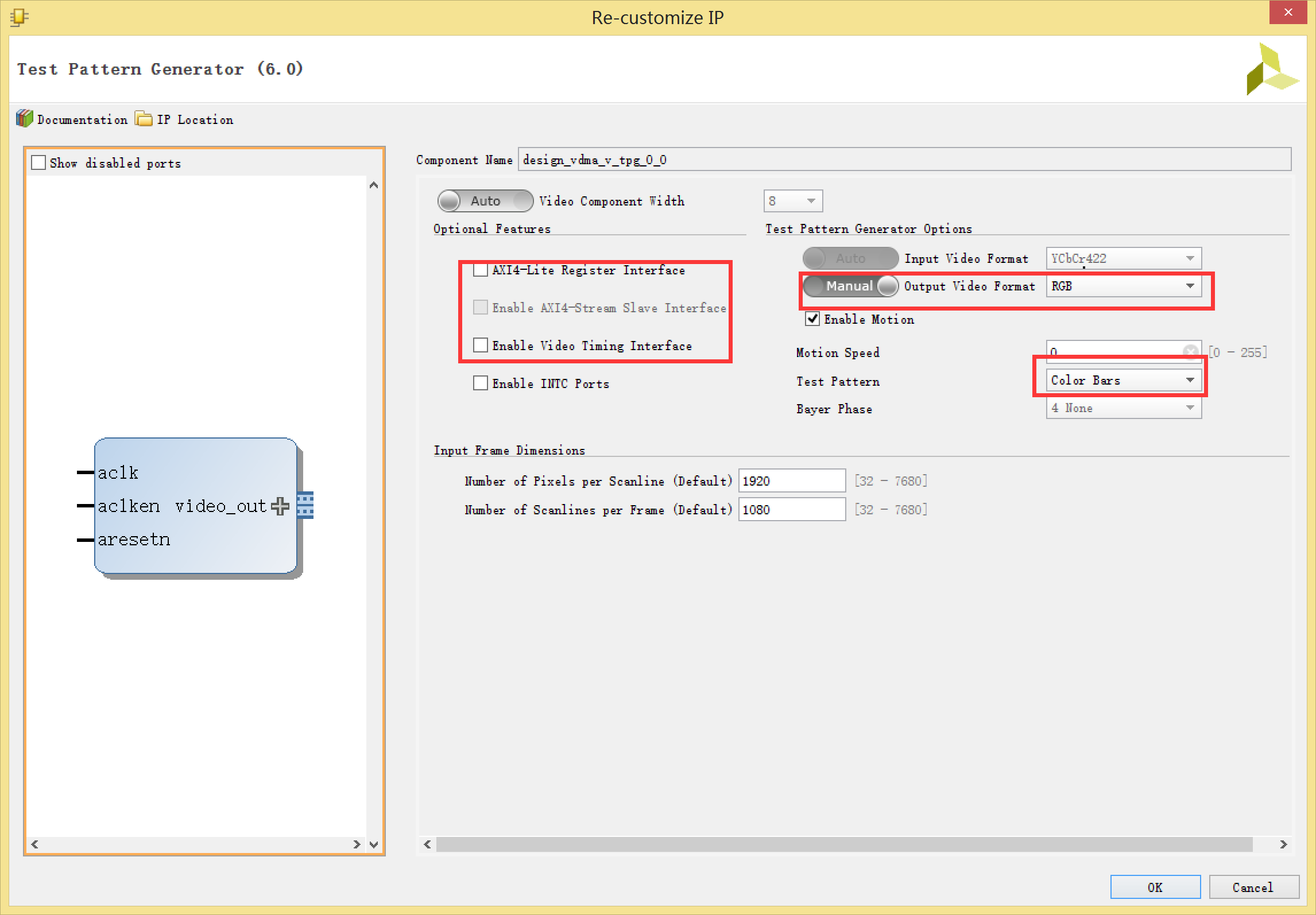

双击刚刚生成的TPG图标,作如下设置

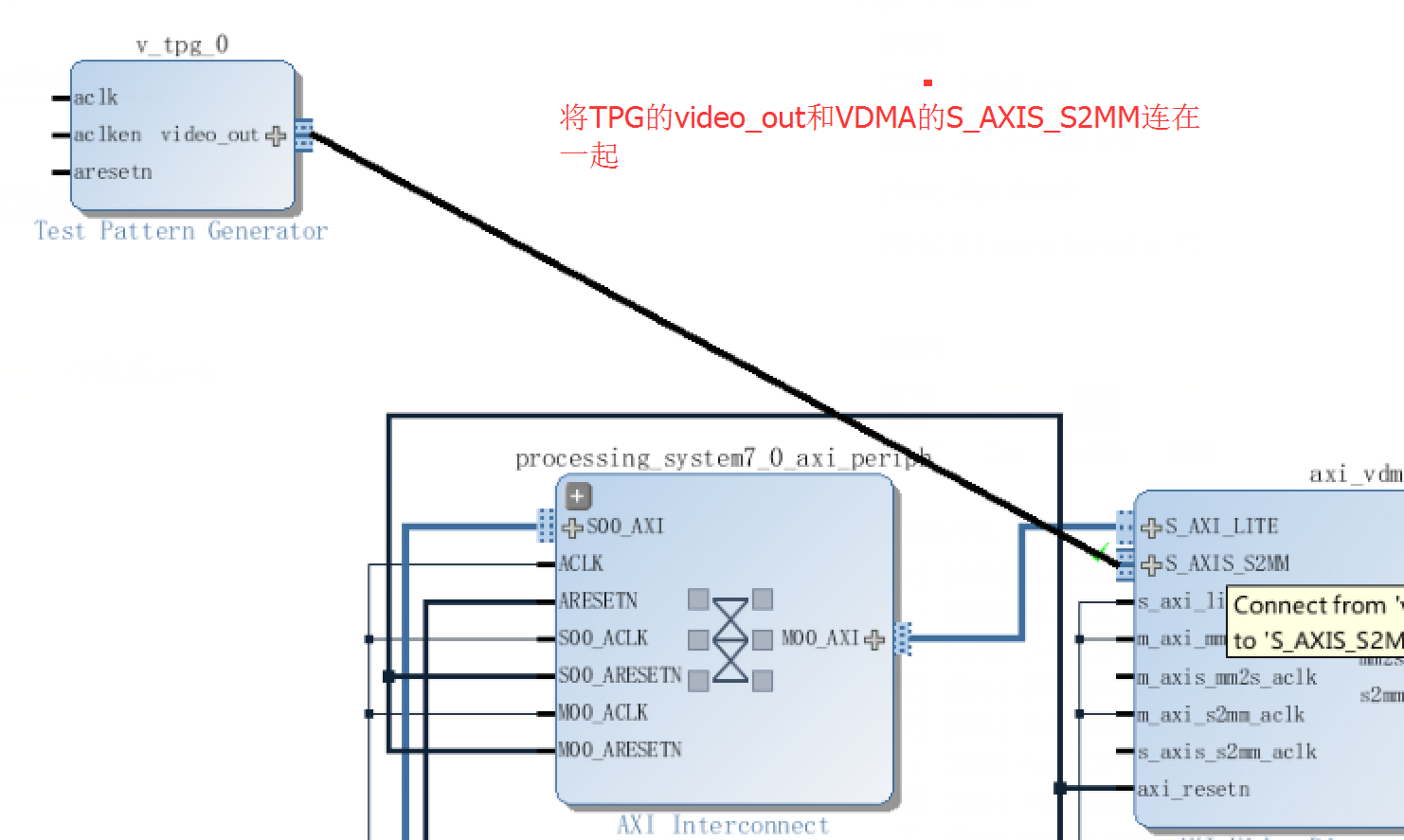

按照如图所示连接

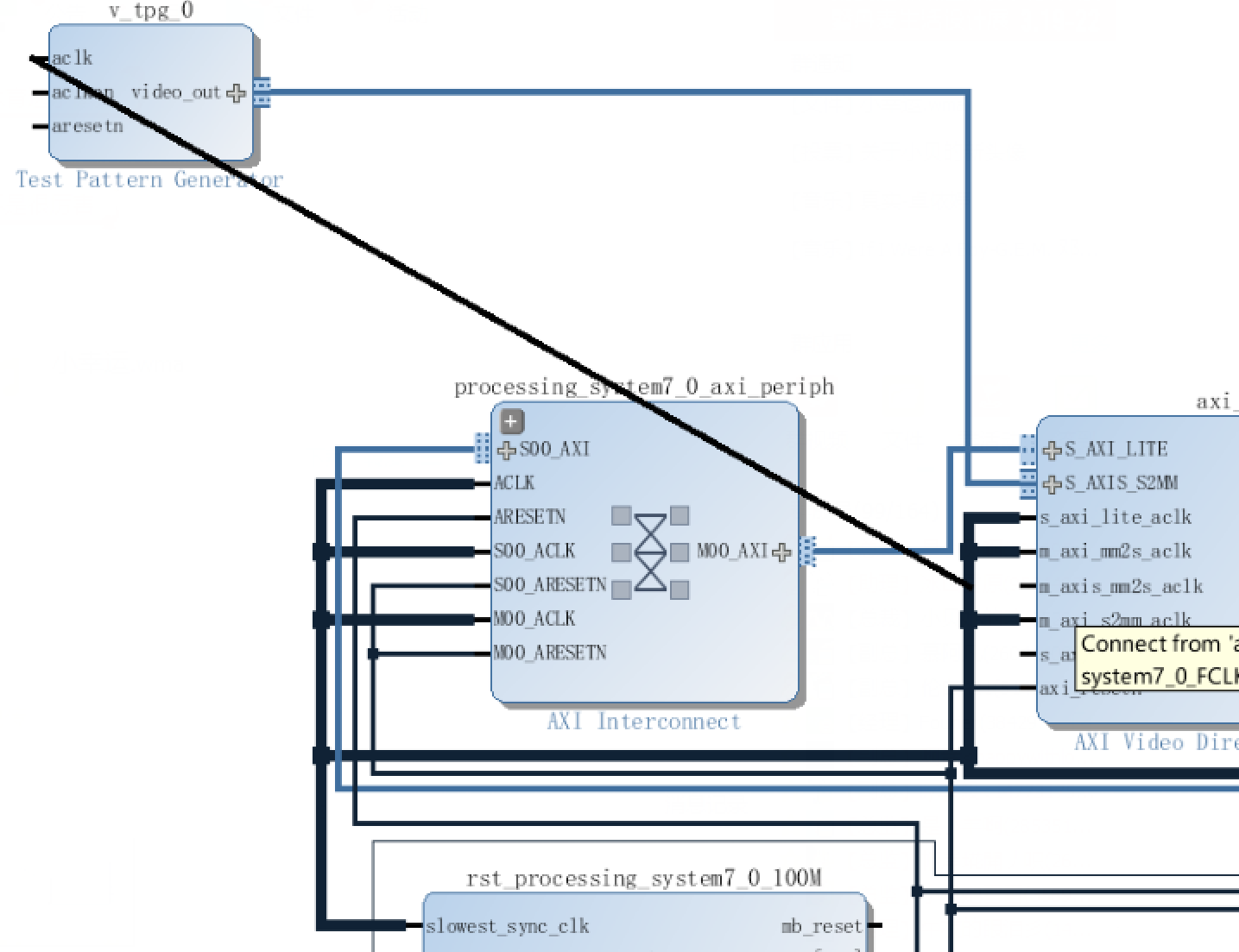

按照如图所示连接时钟线

同上把VDMA的m_axis_mm2s_aclk以及s_axis_s2mm_aclk和上述时钟线连在一起

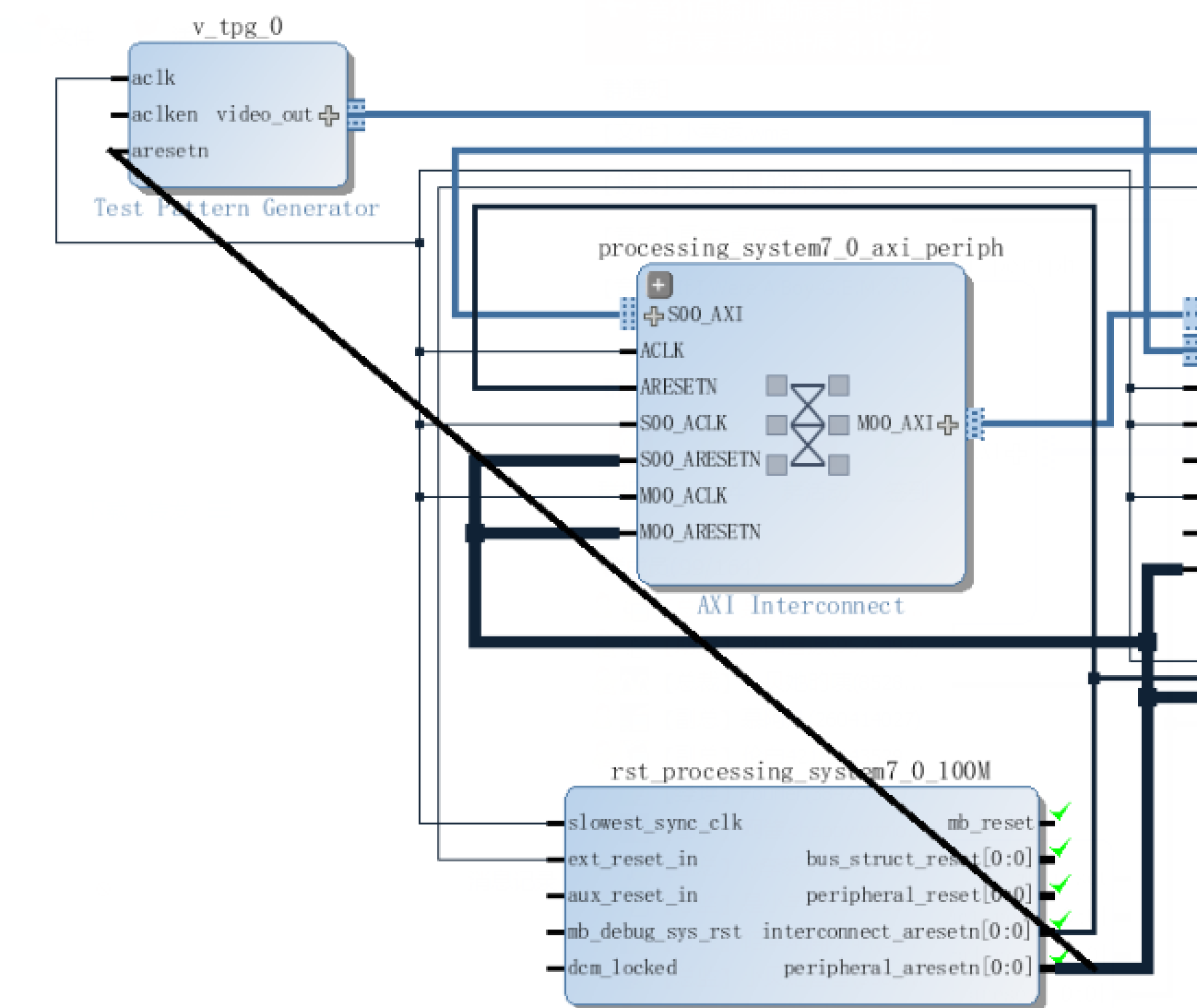

把TPG的aresrtn按照如图所示连接

重新生成布局后,如图所示(右击可以查看高清大图)

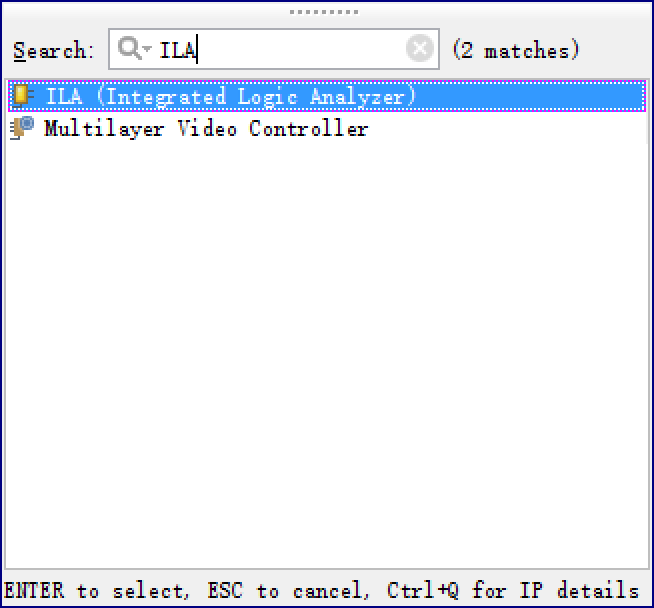

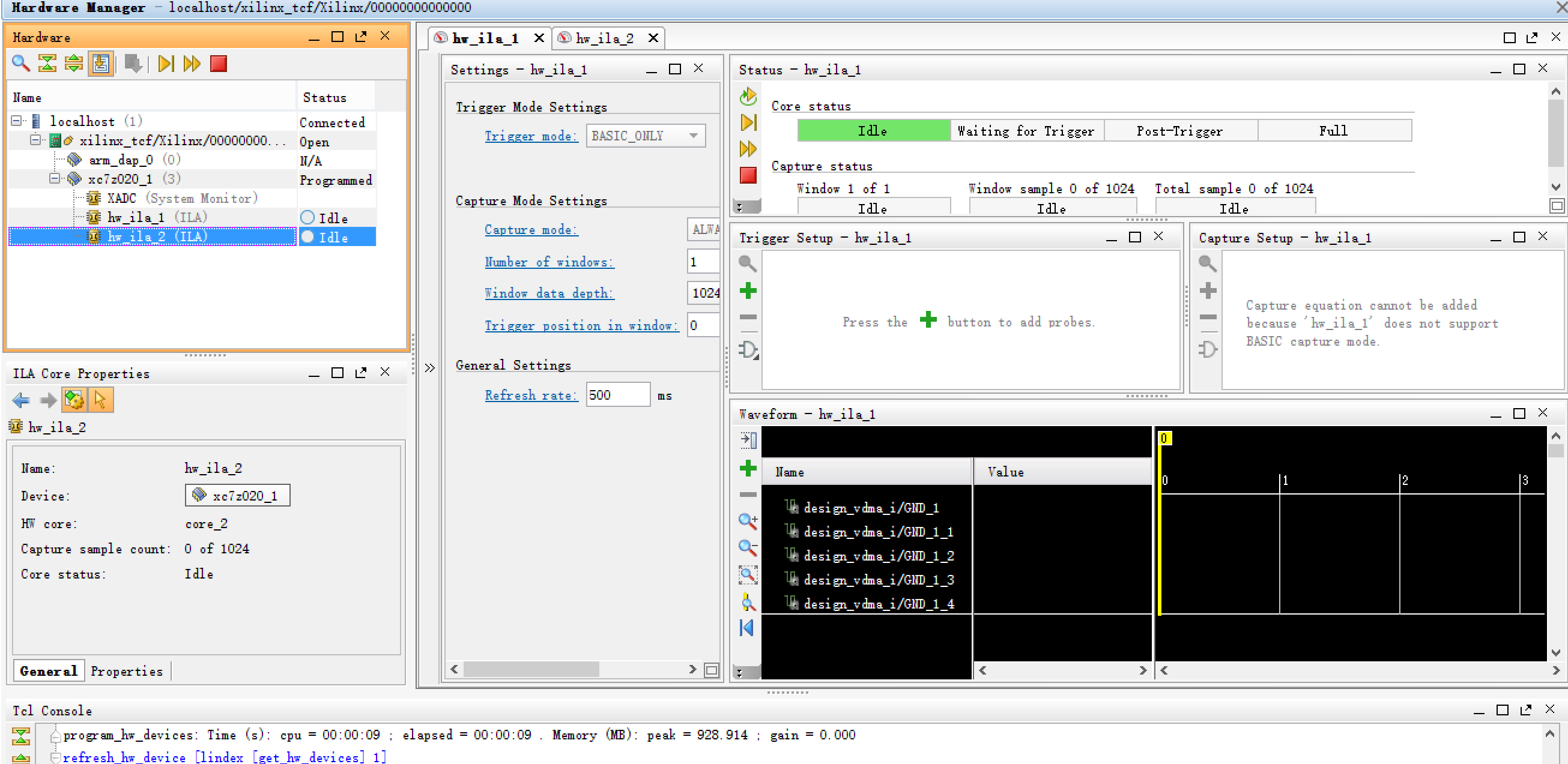

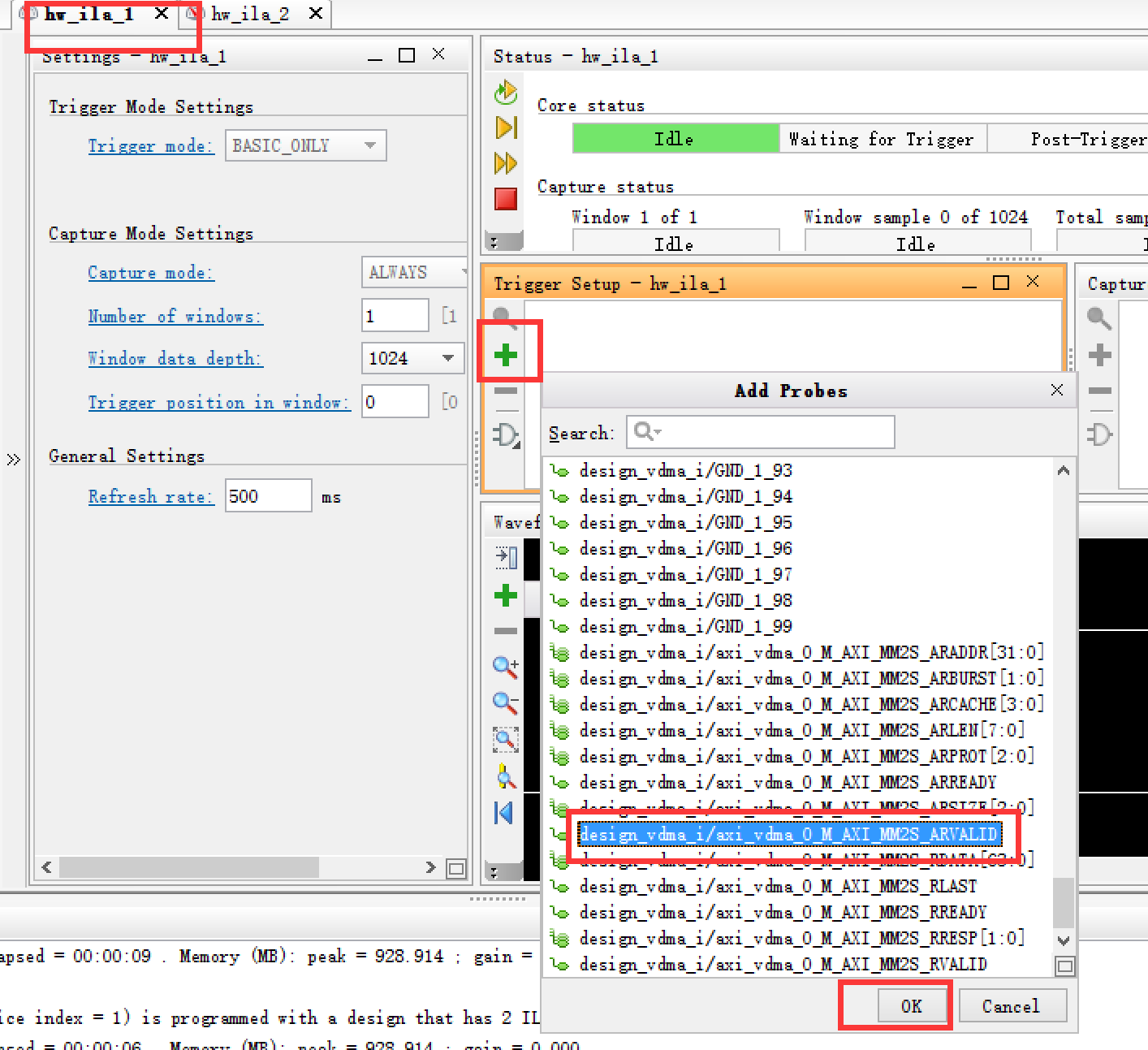

添加ILA IP Core(方法很多,这里未必是最好的)

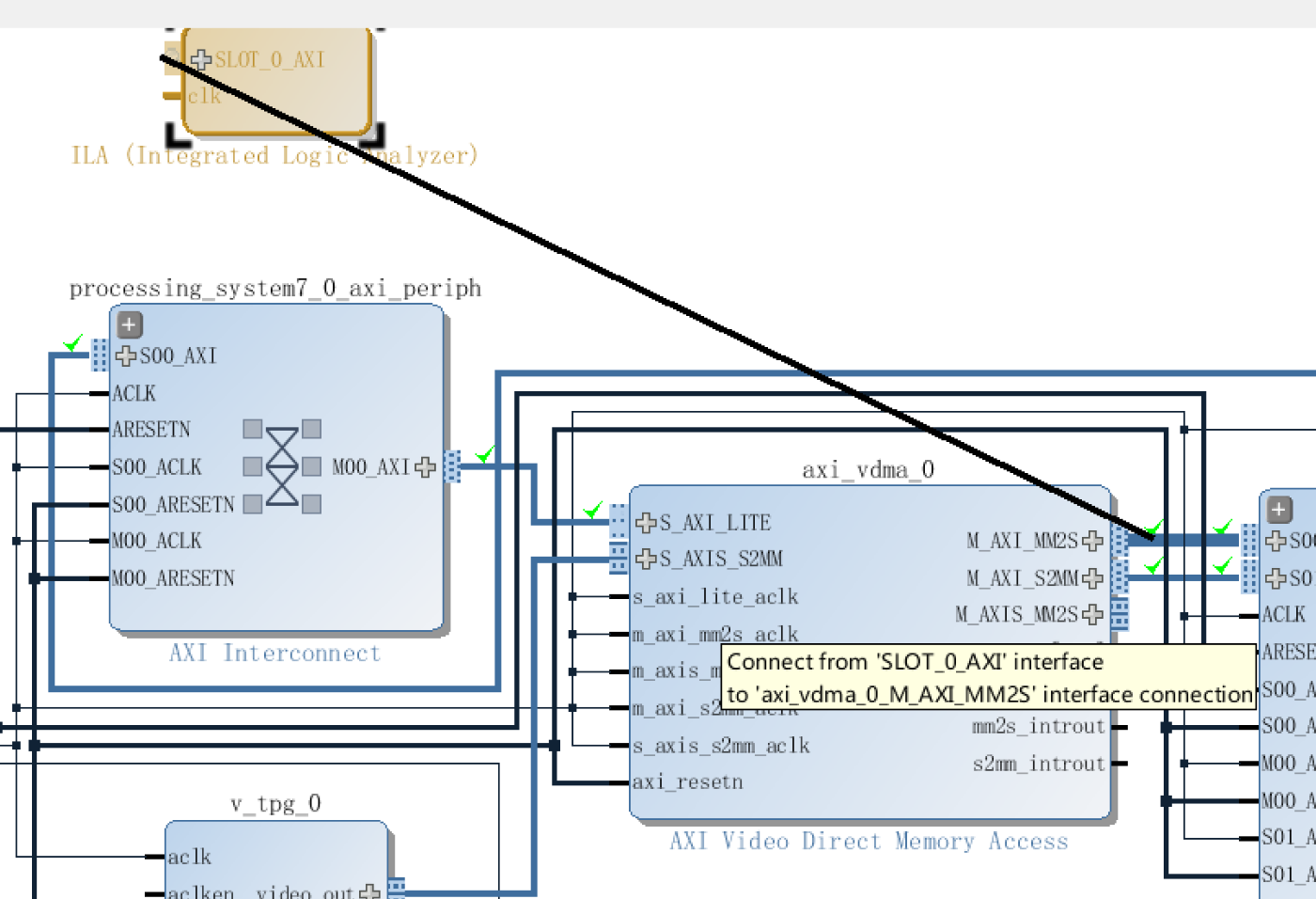

把ila_0的SLOT_0_AXI和VDMA的M_AXI_MM2SS连接在一起

把ila_0的clk和VDMA的aclk连在一起

在添加一个ILA IP Core

把ila_1的SLOT_0_AXI和VDMA的M_AXI_S2MM连接在一起

把ila_1的clk和VDMA的aclk连在一起

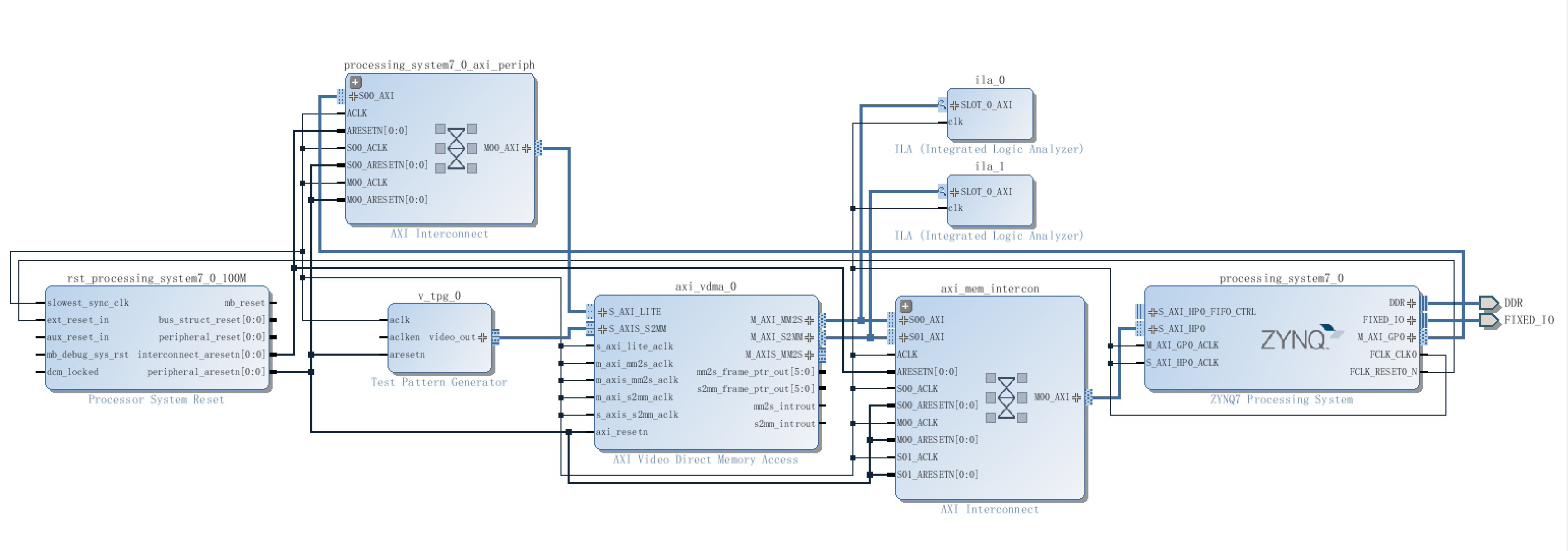

完整的硬件结构框图如下(右击可查看高清大图)

右击Bolock design,选择Create HDL Wrapper

再次右击Bolock design,选择Generate output Prouducts

完成点击Run Synthesisi

完成后,点击Generate bitstream(耐心等待下吧,可以去吃个饭,睡会觉或者浏览下论坛的帖子,发几个评论……)

然后再选择,Tools -> set Up Debug

最后,File->Export->Export Hardware ―-File ->Launch SDK

软件工程

SDK启动后,新建一个Hello World工程

把helloworld.c里的代码修改如下:

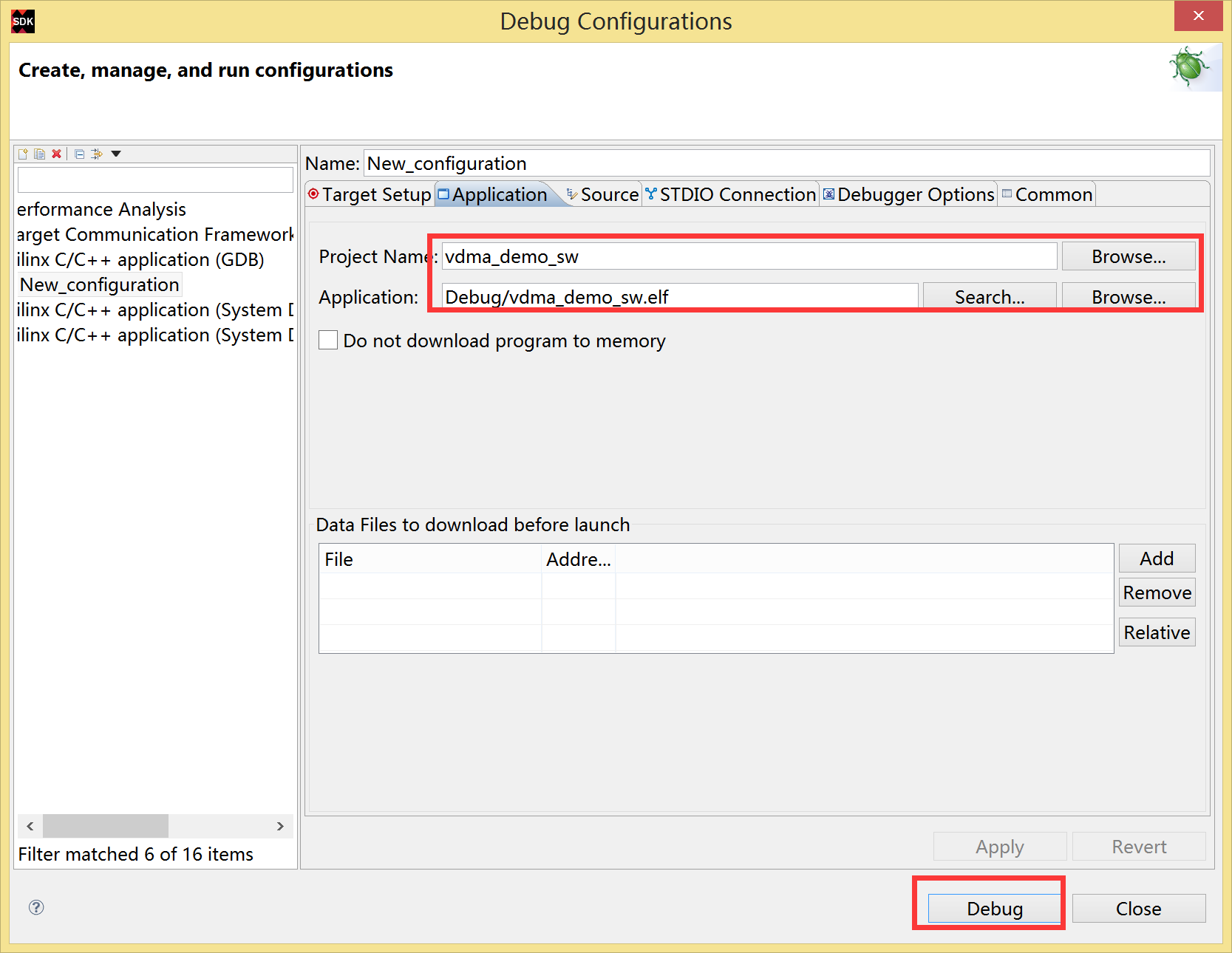

#include <stdio.h>

#include "platform.h"

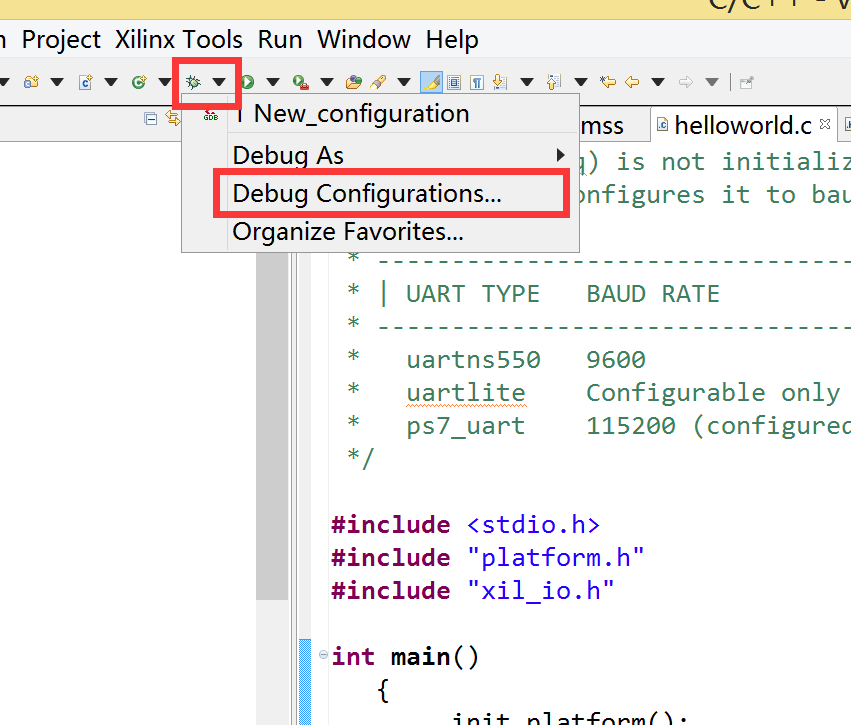

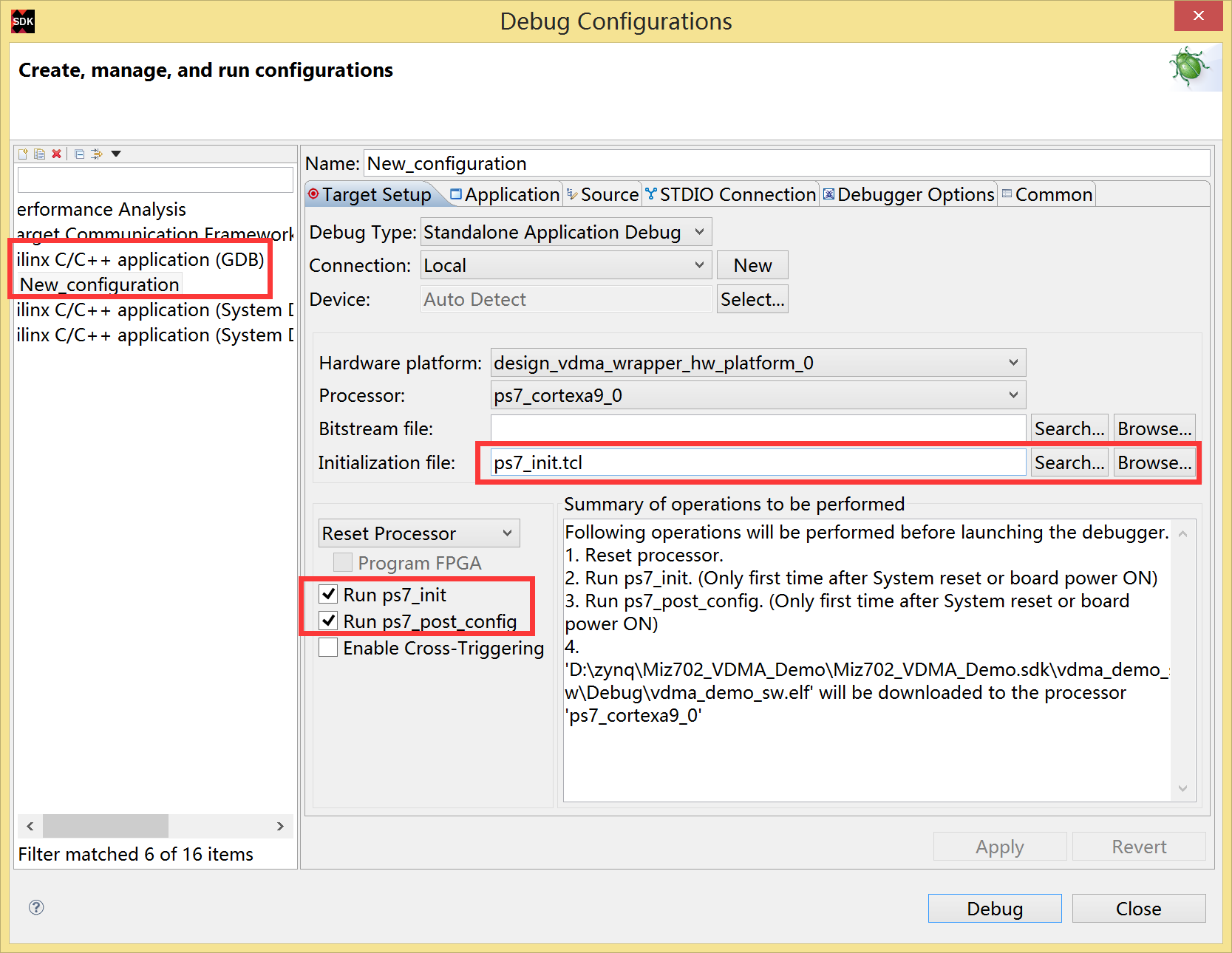

#include "xil_io.h"int main(){init_platform();xil_printf("----------The test is start......----------\n\r");Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x30, 0x4); //reset S2MM VDMA Control RegisterXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x30, 0x8); //genlockXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xAC, 0x08000000);//S2MM Start AddressesXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xAC+4, 0x0A000000);Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xAC+8, 0x09000000);Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA4, 1920*3);//S2MM Horizontal SizeXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA8, 0x01002000);//S2MM Frame Delay and StrideXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x30, 0x3);//S2MM VDMA Control RegisterXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0xA0, 1080);//S2MM Vertical Size start an S2MM transfer//AXI VDMA1Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x0, 0x4); //reset MM2S VDMA Control RegisterXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x0, 0x8); //gen-lockXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x5C, 0x08000000); //MM2S Start AddressesXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x5C+4, 0x0A000000);Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x5C+8, 0x09000000);Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x54, 1920*3);//MM2S HSIZE RegisterXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x58, 0x01002000);//S2MM FRMDELAY_STRIDE Register 1920*3=5760 对齐之后为8192=0x2000Xil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x0, 0x03);//MM2S VDMA Control RegisterXil_Out32(XPAR_AXI_VDMA_0_BASEADDR + 0x50, 1080);//MM2S_VSIZE 启动传输cleanup_platform();return 0;}按照如下配置配置软件Debug