P13 Interface and Program

- 正式运行testcase之前需要做好的准备:

1.对CLK和RESET进行规划,DUT和TB都需要时钟和复位信号。

2.对于第一个testcase用log记录仿真过程,并用display显示仿真结果。

3.首先排除tb的错误,再检查tb给dut环境设置是否错误,全都没错才去检查RTL的错误。

Q:logic数据类型有几个状态?

A:4个,01xz

Interface

Q:如何连接testbench与DUT?

A:先定义连接途径,并利用例化将端口连接起来。

-

Verilog连接方式

1.默认连接方式 .*

e.g. test t1(.*);

要求被例化模块的所有端口在tb当中有名字、类型、数据宽度完全一样的连接路径(不推荐使用)。

2.名字连接方式 .name

3.端口连接方式.name(name)

Q:如果一个被例化模块的端口名发生变化,在上层模块要如何修改?

A:verilog中只能单独修改,SV则可以使用interface规避这个问题。 -

Systemverilog Interface

Interface可以将一组信号放在一起作为一个端口,并将作为单独的部分和tb以及DUT分离开来。这样做可以将不同配置的interface适配给不同的tb,不需要进行繁琐的连接。

关键字:interface/endinterface,端口可选,一般端口当中会列出clk和reset

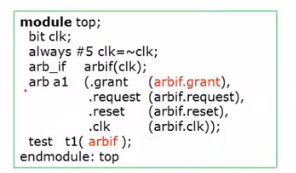

interface需要在top当中进行例化,但是不需要指定输入输出的方向。

与verilog写成的DUT联合仿真时,可以使用端口连接的方式进行连接:

-

代码:

modport

modport用于给interface的信号进行分组,interface可以含有任意多的modport

在上图的modport中给TEST和DUV的端口方向是不一样的。

优点:方便区分功能,缺点:名字变长,命名变复杂

- overview

Stimulus Timing

tb和design的信号时序应当错开,来避免竞争的情况。

一个是尽量不要操纵同一个信号,第二个是在tb中加入延时信息。

可以通过在tb中使用interface的clk来避免时序错乱的情况。

-

Clocking Blocks

可以通过一个时钟模块,将所有行为同步到同一时钟上。

关键字:clocking/endclocking,模块内所有信号以clk的上升沿做触发

default input #1step output #2;

default设置所有的信号:可以使模块去采样clk上升沿前1个时间单位时候的输入,在上升沿#2个时间单位之后输出结果。 -

Timing regions

即使硬件语言是并行语言,实际的执行也有先后顺序。对sv的tb进行仿真时,一个时钟沿含有4个时间域:

1.Active Region(design):模块内的代码仿真

2.Observed Region(assertions):代码仿真以后对断言进行判断

3.Reactive Region(testbench):执行tb

4.Postpone Region(sample):在所有行为结束后对信号采样(如$display等) -

Signal Synchronization

-

Signal Synchronization

通过灵活运用clocking模块内的信号可以完成各个模块的同步。

Program

testbench的顶层应当包含一段program

program内部不能例化其它模块,包括module和interface