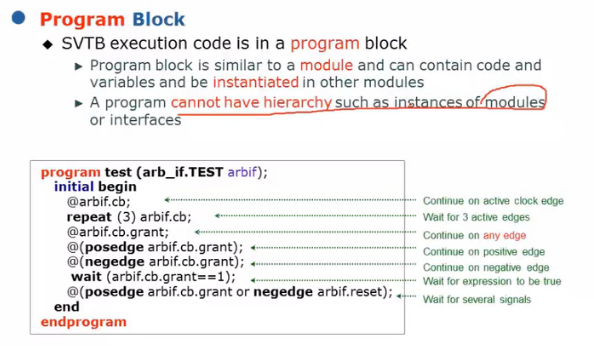

Program

Q:Program能不能含有always块?

A:不能,因为program不能含有module,因此必然不会含有always块。

- 实例

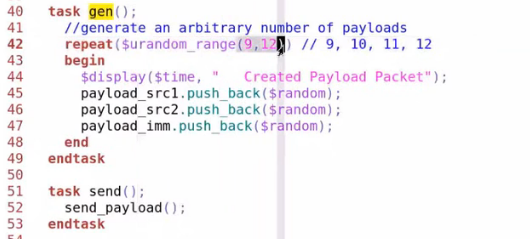

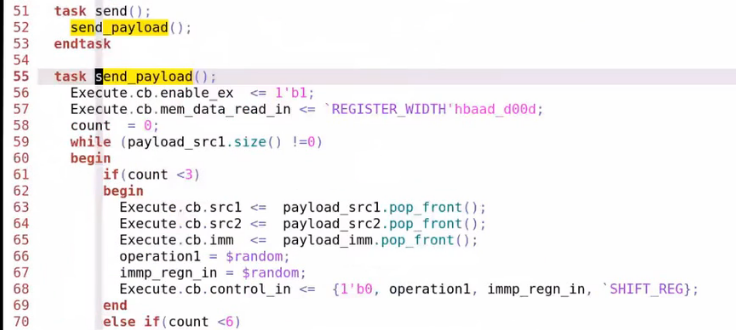

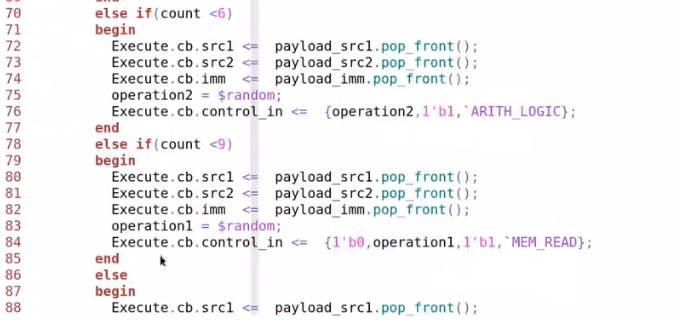

要生成图中激励,可以写出如下的代码:

program test(arb_if.TB arbif);

initial begin//asynch drive reset//reset信号为不同步信号,使用#xns的格式描述时序arbif.reset <= 0;#15ns arbif.reset <= 1;#35ns arbif.reset <= 0;//synch drive request//request信号为同步信号,使用##x的格式描述setup/hold time##1 arbif.cb.request <= 1;##1 arbif.cb.request <= 0;wait (arbif.cb.grant == 1);end

endprograminterface arb_if(input bit clk);logic grant,request,reset;clocking cb@(posedge clk);input grant;output request;endclockingmodport TB(clocking cb, output reset);

endinterface:arb_if- 总结

好处:1.将tb从DUV分离开来;2.通过在不同时域运行,避免竞争的发生;3.为程序运行提供一个切入点;4.划定一个范围去限制数据的产生

作用:1.program可以在top中例化;2.interface和port可以互相连接;3.program下没有子模块,仅仅描述运行的过程;4.program的代码在initial模块下具有一次性,不包含always块;5.在reactive时间域下判定;6.initial模块运行结束以后程序会自动停止运行,相当于具备隐藏的$finish。

-

Top

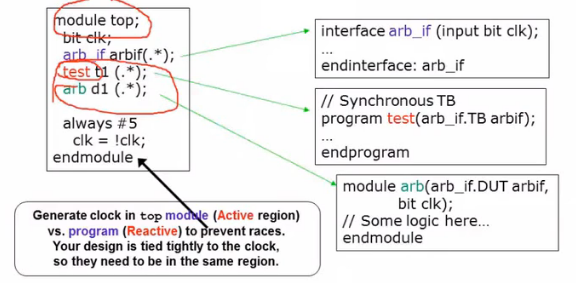

top模块包含的内容:

代码

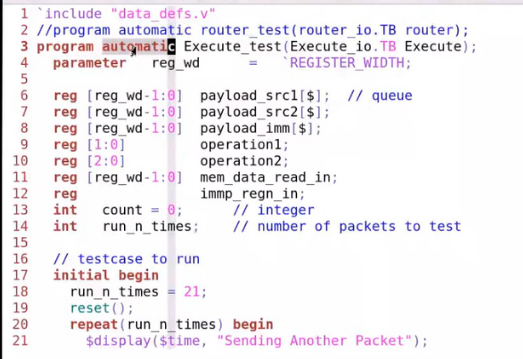

用sv写成的 testbench代码:

automatic的意思与C语言相同,与static静态存储相对,automatic是动态存储。

操作技巧:在文档中搜索某一个变量时,可以将光标放在目标变量上然后按下shift+*,所有同名变量会被高亮。