���߿�

Structure

structure��һ��������߳����ļ��ϣ��ܹ��������ͬʱ�������е�Ԫ�ء�

���

struct{int a,b;logic[7:0] opcode;logic[23:0] address;bit error;

} Instruction_Word

���һ�������structure�����֣����ñ���ʱ�ĸ�ʽΪ��

Instruction_Word.address = 24'hF0000;

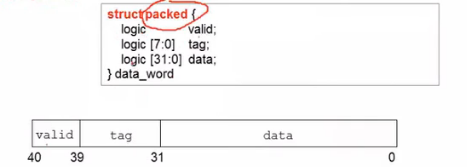

- Packed structure

structureĬ��״̬�����ڴ浱����unpacked״̬������ʹ��packed�ؼ���ʹ�����洢�������Ŀռ䵱�С�

���Կ���ͼ��valid,tag,data��bit��ַ�������ģ�Խ�������ı���bit��Խ��

����packed�Ժ������Ϊһ��������ʻ��д���е�Ԫ�أ�

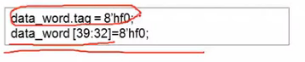

ʵ�ʲ��������Ƽ�ʹ��data_word.tag������ʽ���ã��ɶ��Ըߣ������׳�����

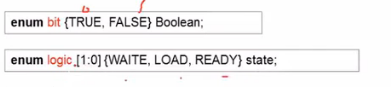

Enumerated Type��ö�٣�

������������ӵ�й̶�ֵ�ı�������״̬�������㳣�������Ӵ���Ŀɶ��ԡ�

���

enum{red,green,blue} RGB

Ĭ��״̬����һ��Ԫ�ظ�ֵ0������Ԫ�ص�ֵ���ε�����

Ҳ���Ը��ض�ֵ��

enum{ONE=1, FIVE=5, TEN=10} RGB

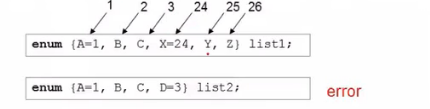

��ͬʱ���ڸ�ֵ��δ��ֵ��Ԫ�أ�δ��ֵ��Ԫ�ػ���ǰһ��Ԫ�صĻ����ϼ�1.

��ֵ������ͻ��ᱨ����error����

- ��������

ö�������ָ��Ԫ�ص��������ͣ�����Ҫע��λ����Ԫ�ظ���Ҫƥ����

��̬������£�ijһԪ�ظ�ֵx����z�ǺϷ��ģ����Dz����ڴ�Ԫ�غ�������δ��ֵ��Ԫ�أ���Ϊx+1��z+1���ܲ����Ϸ��Ľ����

Operators

��C���Խ�Ϊ���ƣ�++�ͨC����blocking assignment�����ܻ�������ð������

==�ڱȽ�x��zʱ�᷵��1��bx��===�ͣ�==�����ʵ����ȫһ�µıȽ�

Procedural Statements

- inside

inside�����жϱ����Dz�����ij��ֵ��Χ��

logic [2:0] a;

if(a inside {3'b001,3'b010,3'b100})

-

Type Casting������ת����

sv���Խ��б���������ת��/����ת��/������ת��������ɼ���ֲᡣ -

ѭ�����

1.for

2.do��while -

case���

sv���ṩ��unique��priority�ؼ��֣�unique����Ψһȷ��ÿ����֧��䣬priority����ȷ��ij����֧�����ȼ���

Tasks and Functions

sv��task��function������ʡȥbegin��end���������˹ؼ���return

sv��void���������Բ�����ֵ

- Tasks

�����ж�������������ܹ�����ʱ���������function/task�� - Functions

�����������κ���ʱ��ʱ�������䣬���ܰ���task

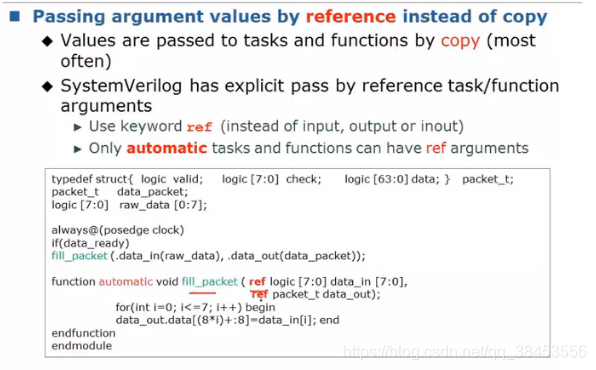

verilog�ĺ������뷵��һ��ֵ - ref