目录

Shift register1

Shift register2

Shift register1

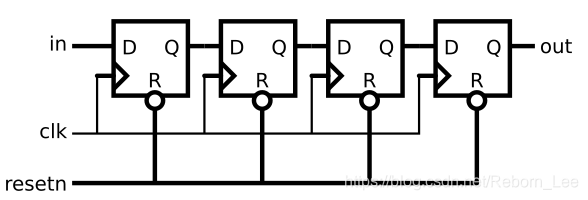

实现下面的电路:

module top_module (input clk,input resetn, // synchronous resetinput in,output out);reg q1, q2, q3, q4;always@(posedge clk) beginif(~resetn) beginq1 <= 0;q2 <= 0;q3 <= 0;q4 <= 0;endelse beginq4 <= q3;q3 <= q2;q2 <= q1;q1 <= in;endendassign out = q4;endmodule

奇怪地是,既然是同步复位,为什么RTL图画的不符合,有点不严谨了哈。

Shift register2

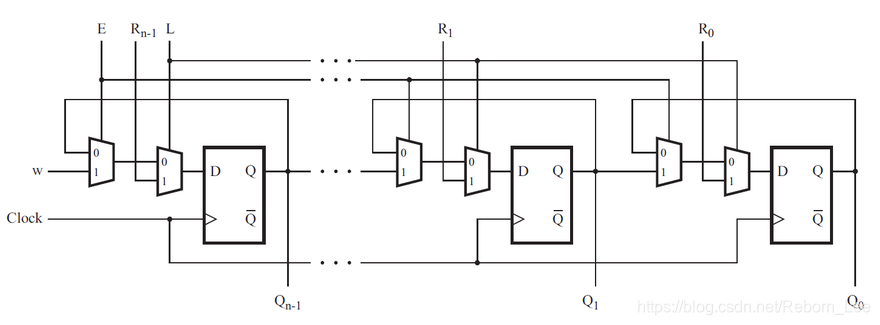

Consider the n-bit shift register circuit shown below:

Write a top-level Verilog module (named top_module) for the shift register, assuming that n = 4. Instantiate four copies of your MUXDFF subcircuit in your top-level module. Assume that you are going to implement the circuit on the DE2 board.

- Connect the R inputs to the SW switches,

- clk to KEY[0],

- E to KEY[1],

- L to KEY[2], and

- w to KEY[3].

- Connect the outputs to the red lights LEDR[3:0].

先给出每一个子模块的设计:

module MUXDFF (input clk,input w, R, E, L,output Q

);//reg Q;wire mid1, mid2;assign mid1 = E ? w : Q;assign mid2 = L ? R : mid1;always@(posedge clk) beginQ <= mid2;endendmodule

通过例化子模块,得到顶层设计:

module top_module (input [3:0] SW,input [3:0] KEY,output [3:0] LEDR

); //

wire q4, q3, q2, q1;MUXDFF inst4(.clk(KEY[0]),.w(KEY[3]),.R(SW[3]),.E(KEY[1]),.L(KEY[2]),.Q(q4));MUXDFF inst3(.clk(KEY[0]),.w(q4),.R(SW[2]),.E(KEY[1]),.L(KEY[2]),.Q(q3));MUXDFF inst2(.clk(KEY[0]),.w(q3),.R(SW[1]),.E(KEY[1]),.L(KEY[2]),.Q(q2));MUXDFF inst1(.clk(KEY[0]),.w(q2),.R(SW[0]),.E(KEY[1]),.L(KEY[2]),.Q(q1));

assign LEDR = {q4, q3, q2, q1};endmodule