目录

前言

原题复现

审题

我的设计

测试吐槽

最后的解决方案

前言

今天的这个问题,并没有满意的解决,路过的朋友,看出问题所在的,可以给个评论,谢谢。

原题复现

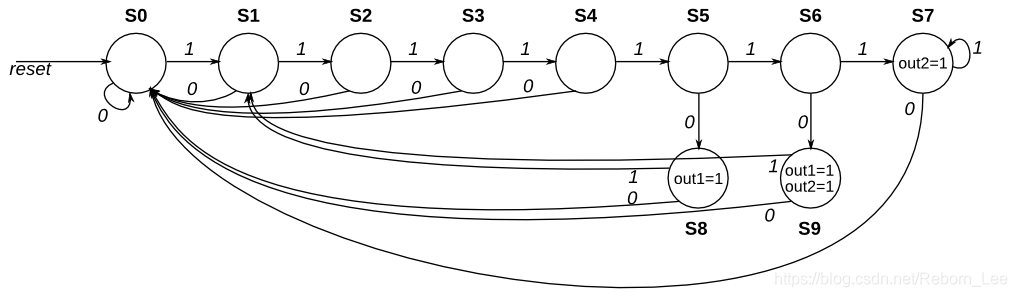

Fsm onehot

下面是一个最基础的状态机的一部分,这是一个题目,我们用最常规的方式来解决它。

原题传送

审题

上图是一个状态转移图,我们用给出的输入输出模型来实现这个状态机,确切的说,这不是一个完整的状态机,如果根据给的输入输出来看:

module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);当前状态作为输入,也就是说不需要寄存器来实现状态转移的时序逻辑部分了。

这里有一个要求,就是状态编码要用独热码,原题如下描述的:

Suppose this state machine uses one-hot encoding, where state[0] through state[9] correspond to the states S0 though S9, respectively. The outputs are zero unless otherwise specified.

Implement the state transition logic and output logic portions of the state machine (but not the state flip-flops). You are given the current state in state[9:0] and must produce next_state[9:0] and the two outputs. Derive the logic equations by inspection assuming a one-hot encoding. (The testbench will test with non-one hot inputs to make sure you're not trying to do something more complicated).

我的设计

我用最基础的方式,做出了如下的设计:

module top_module(input in,input [9:0] state,output [9:0] next_state,output out1,output out2);localparam S0 = 10'b0000_0000_01, S1 = 10'b0000_0000_10, S2 = 10'b0000_0001_00, S3 = 10'b0000_0010_00,S4 = 10'b0000_0100_00; localparam S5 = 10'b0000_1000_00, S6 = 10'b0001_0000_00, S7 = 10'b0010_0000_00, S8 = 10'b0100_0000_00,S9 = 10'b1000_0000_00;always@(*) begincase(state)S0: beginif(in) next_state = S1;else next_state = S0;endS1: beginif(in) next_state = S2;else next_state = S0;endS2: beginif(in) next_state = S3;else next_state = S0;endS3: beginif(in) next_state = S4;else next_state = S0;endS4: beginif(in) next_state = S5;else next_state = S0;endS5: beginif(in) next_state = S6;else next_state = S8;endS6: beginif(in) next_state = S7;else next_state = S9;endS7: beginif(in) next_state = S7;else next_state = S0;endS8: beginif(in) next_state = S1;else next_state = S0;endS9: beginif(in) next_state = S1;else next_state = S0;enddefault: beginnext_state = S0; endendcaseendassign out1 = (state == S8 | state == S9) ? 1 : 0;assign out2 = (state == S9 | state == S7) ? 1 : 0;endmodule

测试吐槽

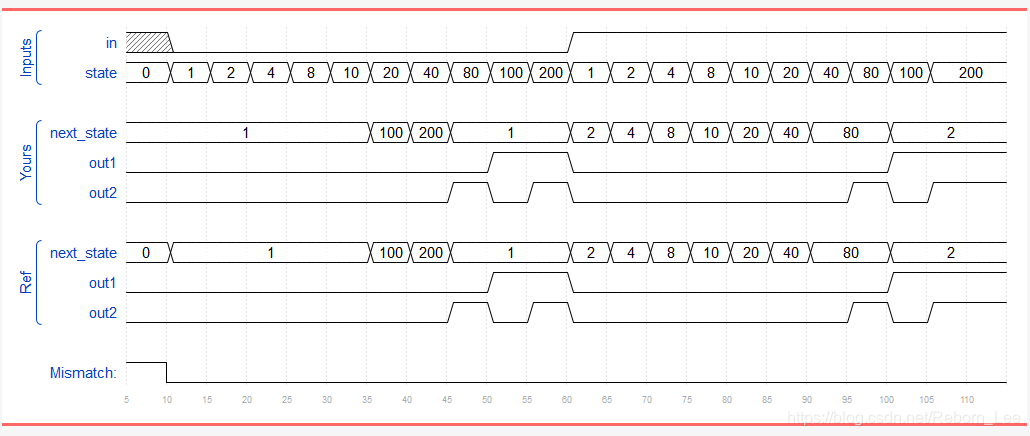

测试结果呢?

从不匹配的地方可以看出,问题在于第一个状态,为了测试,平台给了一个状态0???

你让我用独热码,然后又给我输入了一个状态0?

你不会在逗我吧?

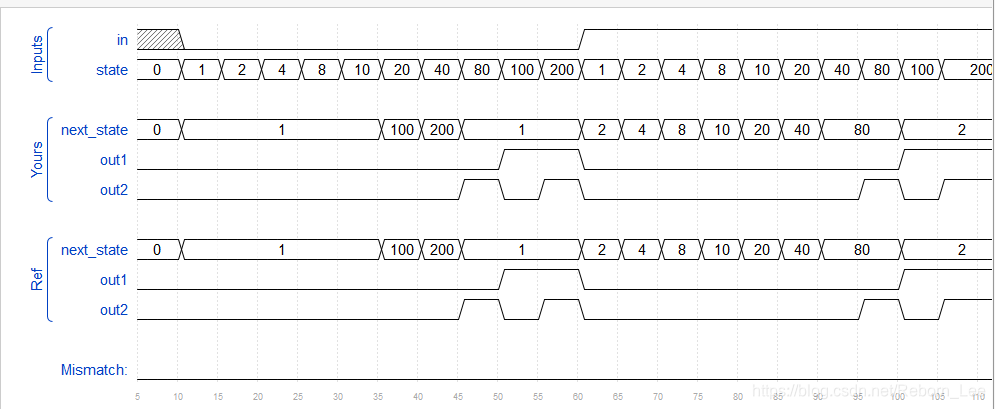

好,假如我屈服与你的淫威,这个状态是我不存在的,我把它加入到default中去,状态转移部分的default改为如下:

default: begin

next_state = 0;

end

可见,这一段测试结果是没错了:

但是问题又出现在了:

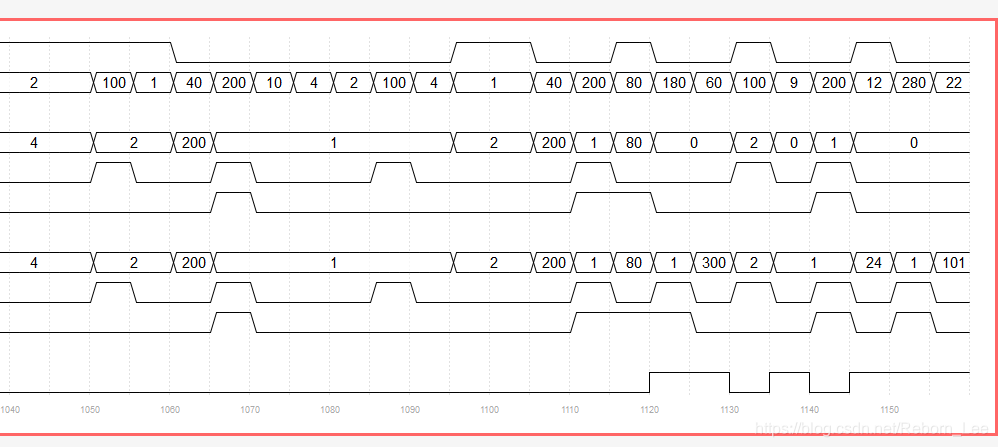

又乱jr给我当前状态,what?180?也就是1_1000_0000?这是独热码吗?我又只能跳到default那部分?于是乎,又和你的不一样了?

罢了罢了,这是我的独热码,你玩你的独热码,到此为止吧。

最后的解决方案

https://blog.csdn.net/Reborn_Lee/article/details/103480678