ЮФеТФПТМ

- ЧАбд

- ЗТецгяЗЈ

-

- Graphic Waveform

-

- Ъ§зжВЈаЮМђНщ

- ДгЪЕМЪЕНЗТец

-

- ЪЕМЪЯЕЭГМьВт

- ШэМўЗТецФЃФт

- ЁАHello worldЁБжЎGraphic Waveform

-

- Д§ЗТецЩшМЦ

- вЛаЉЛцжЦВЈаЮЕФВйзї

-

- ЬэМгЖЫПк

- ДДНЈЪБжгаХКХ

- ЧЏжЦгыЪЭЗХаХКХ

- ЕчЦНЗзЊ

- ЩњГЩЫцЛњађСа

- змЯпЩшжУ

- вЛаЉЙлВьВЈаЮЕФВйзї

-

- ВЈаЮЫѕЗХ

- змЯпЙлВь

- ЬэМгЪББъ

- БпбибАев

- ВЈаЮЗТецНсЙћЗжЮіМАживЊзЂвтЪТЯю

-

- вЛЁЂШчЙћХаЖЯЗТецНсЙћЖдгыДэЃП

- ЖўЁЂЗТец0ЪБПЬЕФвтвхЁЃ

- Ш§ЁЂЁАБпбиЖдБпбиЁБЕФХаЖЈЁЃ

ЧАбд

БОЮФеЊздЁЖFPGAжЎЕРЁЗЁЃ

ЗТецгяЗЈ

БОеТНкНЋЮЊДѓМвНщЩмМИРрГЃгУЕФЗТецБрГЬгяЗЈЃЌАќРЈЭМаЮЛЏЗТецЁЂVHDLЁЂVerilogЁЂSystem VerilogвдМАAssertionЁЃЦфжаЃЌЭМаЮЛЏЗТецЪЧзюдЪМЕФвЛжжЗТецЗНЗЈЃЌдкетРяНщЩмЕФФПЕФЪЧЮЊСЫШУДѓМвЖдЗТецгавЛИіГѕВНСЫНтЃЛVHDLгыVerilogГ§СЫгУгкFPGAЩшМЦЕФУшЪіЭтЃЌвВПЩвдгУРДНјааЗТецДњТыЕФБраДЃЌгЩгкДгЪТFPGAЯюФПЕФЙЄзїШЫдБвЛАуЖМОпгаНЯКУЕФHDLгябдЛљДЁЃЌвђДЫетСНепдкЗТецЗНУцЕФЪЙгУЛЙЪЧБШНЯЙуЗКЕФЃЛЖјSystem VerilogдђЪЧИќЮЊЧПДѓЁЂИќМгзЈвЕЕФЗТецгяЗЈЃЌетвВЪЧБОеТНкНщЩмЕФжиЕуЃЛЖдгкAssertionЃЌгыЦфЫЕЫќЪЧвЛжжЗТецЕФгяЗЈЃЌВЛШчЫЕЫќЪЧвЛжжНјНзЕФЗТецЗНЗЈЛђепЦфЫќЗТецгяЗЈЕФвЛИізгВПЗжЃЌвђЮЊЭЈГЃРДЫЕЫќашвЊНсКЯVHDLЁЂVerilogЛђепSystem VerilogРДЪЙгУЃЌВЛЙ§System VerilogЖдЦфЕФжЇГжЪЧзюШЋУцЁЂзюКУЕФЁЃ

FPGAЗТецгяЗЈгыFPGAЩшМЦгяЗЈзюБОжЪЕФЧјБ№ОЭдкгкгУЦфЫљБраДЕФДњТыЪЧЗёашвЊЖдгІгкОпЬхЕФЪ§зжЕчТЗЁЃЫљвдЗВЪЧFPGAЗТецгяЗЈЖМЪЧШэМўЩшМЦгябдЃЌЗВЪЧFPGAЩшМЦгяЗЈЖМЪЧгВМўУшЪігябдЃЌЙигкетСНепЧјБ№ЕФЯъЯИВћЪіПЩвдВЮдФЁОЙВЭЌгябдЦЊ->гВМўУшЪігябд->ШэМўБрГЬЫМТЗгыFPGAБрГЬЫМТЗЕФБфИяЁПеТНкЁЃвђДЫЃЌдкбЇЯАЗТецгяЗЈЪБЃЌашвЊзЊЛЛвЛЯТЫМТЗЃЌИќЖрЕФвдШэМўЕФЪгНЧШЅЩѓЪгЮЪЬтЃЌвдЗРТфШыЁОГЬађЩшМЦЦЊЁПжаЕФЫМЮЌЖЈЪНЃЌжЦдМСЫЮвУЧЕФЗЂЛгЁЃ

гЩгкFPGAЗТецгяЗЈЦфЪЕЪЧШэМўЕФБрГЬгяЗЈЃЌвђДЫЦфдкБраДЕФЪБКђИќМгЕФЫцвтЁЂИќМгЕФСщЛюЁЃЫљвдЃЌЮЊСЫФмЙЛШУДѓМвБШНЯШнвзЕФШыУХЃЌБОеТНкВЩгУЁАШыУХЗЖР§+гяЗЈНщЩмЁБЕФФЃЪНЁЃЦфжаШыУХЗЖР§ЛЗНкЖМЭГвЛвдЁАHello WorldЁБУќУћЃЌетЪЧвђЮЊЁАHello WorldЁБдкЫљгаБрГЬгябдЕФЦ№ЪМНзЖЮЃЌеМОнзХЮоЗЈКГЖЏЕФРњЪЗЕиЮЛЃЌМИКѕдкЫљгаЙњМвЕФЫљгаАцБОЕФБрГЬНЬВФжаЃЌЁАHello WorldЁБзмЪЧзїЮЊЕквЛИіГЬађВтЪдЗЖР§МЧТМгкЪщБОжЎжаЃЌМИКѕЫљгаБрГЬЕФЕквЛВНОЭдкгкДЫСЫЃЌЫљвдЫќЪЧОЕфжЎжаЕФОЕфЃЁвђДЫБОеТНкШыУХЗЖР§ЛЗНкЕФЗЖР§ЫфШЛВЂВЛвЛЖЈЪфГіЁАHello WorldЁБЙиМќзжЃЌЕЋЦфЖдгкЮвУЧШыУХЗТецгяЗЈЕФживЊадгыЁАHello WorldЁБЪЧвЛбљЕФЃЌвђДЫНЋетаЉаЁНкЭГвЛгУЁАHello WorldЁБУќУћЃЌвдБэЪОЖдетвЛОЕфЕФЩюЩюОДвтЃЁ

зюКѓЧызЂвтЃЌFPGAЕФЗТецгяЗЈвВЪЧжЇГжЛьКЯБрГЬЕФЃЌВЛЙ§Г§ЗЧЭђВЛЕУвбЃЌОЁСПВЛвЊИјздМКевТщЗГЁЃНгЯТРДЃЌЮвУЧОЭПЊЪМж№ИіНщЩметаЉFPGAЗТецгябдЕФгяЗЈЁЃ

Graphic Waveform

Graphic WaveformЗНЗЈЖдгкЙІФмЗТецРДЫЕЪЧШыУХМЖжаЕФШыУХЃЌВЛЙ§дкБОаЁНкжаНщЩмЕФвЛаЉЛљБОИХФюКЭзЂвтЪТЯюШДЪЧЗЧГЃЗЧГЃживЊЕФЃЌЧыЮёБиШЯецдФЖСЁЃ

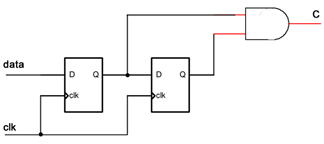

Ъ§зжВЈаЮМђНщ

Ъ§зжВЈаЮОЭЪЧТпМЕчЦНЖдЪБМфЕФЭМаЮБэЪОаЮЪНЁЃ

ЪзЯШЃЌТпМЕчЦНЕФШЁжЕЪЧРыЩЂЕФЃЌР§ШчЃКЖдгкЫФжЕТпМЕчЦНРДЫЕЃЌ0VЕчбЙБэЪОТпМ0ЃЌ1VЕчбЙБэЪОТпМ1ЃЌ2VЕчбЙБэЪОТпМ2ЃЌ3VЕчбЙБэЪОТпМ3ЃЛЖдгкШ§жЕТпМЕчЦНЃЌ-1VЕчбЙБэЪОТпМ-1ЃЌ0VЕчбЙБэЪОТпМ0ЃЌ1VЕчбЙБэЪОТпМ1ЃЛЕШЕШЁЃВЛЙ§дкЪЕМЪжагІгУзюЙуЗКЕФЛЙЪЧЖўжЕТпМЕчЦНЃЌР§ШчЃКTTL3V3ЃЌ0VБэЪОТпМ0ЃЌ3.3VБэЪОТпМ1ЃЛLVCMOS1V8ЃЌ0VБэЪОТпМ0ЃЌ1.8VБэЪОТпМ1ЃЛLVDS2V5ЃЌВюЗжЯпМфбЙВюЮЊ350mVБэЪОТпМ1ЃЌбЙВюЮЊ-350mVБэЪОТпМ0ЃЛЕШЕШЁЃЖўжЕТпМЕчЦНЫфШЛУПвЛДЮДЋЪфЕФаХЯЂСПБШНЯЩйЃЌЕЋЪЧЦфПЙдыЩљадФмШДзюЧПЃЌВЂЧвДЋЪфЫйТЪвВПЩвдКмПьЃЌЖјЧввВЪЧЮяРэзюШнвзЪЕЯжЕФЁЃШчЙћашвЊЭЌЪБДЋЪфИќЖрЕФаХЯЂСПЃЌвВПЩвдРћгУЖрИљаХКХЯпРДзщГЩ2ЕФNДЮЗНжжБфЛЏвдЪЪгІвЊЧѓЁЃЫљвддкЮвУЧЕФFPGAЩшМЦжаЃЌЪЙгУЕФОЭЪЧетжжЖўжЕТпМЕчЦНЁЃЮЊСЫЭГвЛЦ№МћЃЌдкНјааЪ§зжВЈаЮЛцжЦЙ§ГЬжаЃЌТпМЕчЦНЕФЗљЖШжЕЮвУЧЭГвЛгУТпМ1ЁЂТпМ0РДБэЪОЃЌЖјВЛШЅМЦНЯЦфЫљЖдгІЕФЪЕМЪЮяРэЕчЦНЪЧЖрЩйЁЃ

ЦфДЮЃЌЧызЂвтЃЌЫфШЛЪ§зжаХКХдкЗљЖШЩЯЪЧРыЩЂЕФЃЌЕЋЪЧЦфдкЪБМфЩЯШДЪЧСЌајЕФЃЌвђЮЊЕчаХКХдкЪЕМЪжаЖМЪЧСЌајЕФЁЃ

гЩгкТпМЕчЦНЕФШЁжЕЗЖЮЇЪЧгаЯоЕФЧвРыЩЂЕФЃЌЖјЪБМфЕФШЁжЕЗЖЮЇЪЧЮоЯоЕФЧвСЌајЕФЃЌвђДЫдкЪ§зжВЈаЮЕФЛцжЦжаЃЌЮвУЧгУКсзјБъБэЪОЪБМфЃЌзнзјБъБэЪОТпМЕчЦНЕФЗљЖШЁЃвдЯТЪЧвЛаЉЖўжЕЪ§зжВЈаЮЕФЪОР§ЃЌЙЉДѓМвВЮПМЃК

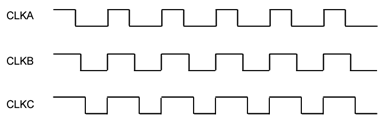

ЪОР§вЛЃКclockAЁЂclockBЁЂclockCжмЦкОљЮЊ10nsЃЌеМПеБШЗжБ№ЮЊ40%ЁЂ50%ЁЂ60%ЁЃ

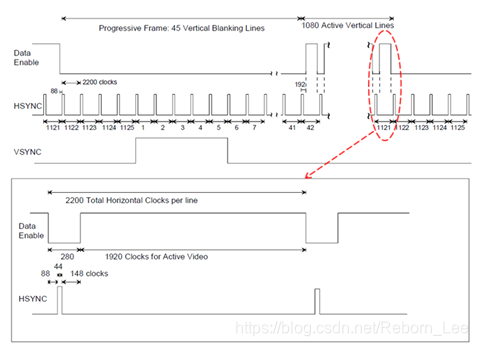

ЪОР§ЖўЃКФГвЛИіЗжБцТЪЮЊ1920x1080ЪгЦЕаХКХЕФааЁЂГЁЩЈУшМАЪ§ОнЪЙФмаХКХЕФДЋЪфВЈаЮЁЃ

ДгЪЕМЪЕНЗТец

ЪЕМЪЯЕЭГМьВт

ЮвУЧЯШРДПДвЛПДЪ§зжЕчТЗдкЯжЪЕЪРНчжаЕФЙЄзїЧщПіАЩЁЃ

ШчЯТЭМЫљЪОЃЌЕчТЗжаЕФFPGAаОЦЌЪЕЯжЕФЪЧвЛИіТпМгыЕФЙІФмЃЌ

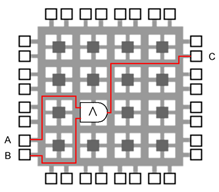

дкЕчТЗе§ГЃЙЄзїЕФЧщПіЯТЃЌЮвУЧПЩвдгУЪОВЈЦїAЁЂBЁЂCЗжБ№ЙлВьЦфСНИіЪфШыв§НХКЭвЛИіЪфГів§НХЃЌЕУЕНЕФВЈаЮЭМПЩФмШчЯТЃК

ЭЈЙ§ЩЯЭМЃЌЮвУЧПЩвдДѓжТХаЖЯГіИУFPGAаОЦЌЕФааЮЊЗћКЯдЄЦкЃЌвђДЫПЩвдЫуЪЧЛљБОЭъГЩСЫИУаОЦЌЕФбщжЄЙЄзїЁЃзЂвтЃЌгЩгкЪЕМЪЕчТЗжаДцдкзХЪБМфбгГйЃЌвђДЫЪОВЈЦїCжаЕФВЈаЮвЊБШAЁЂBжЭКѓвЛаЉЃЌЖјдкЙІФмЗТецжаЪЧВЛашвЊПМТЧШЮКЮЪБМфбгГйаХЯЂЕФЁЃ

ШэМўЗТецФЃФт

ЪВУДЪЧЗТецЃПЗТецОЭЪЧЖдецЪЕЯЕЭГЕФФЃФтЃЌдкМЦЫуЛњММЪѕгІгУШеЧїЙуЗКЕФНёЬьЃЌЗТецЛљБОЩЯЖМЪЧЭЈЙ§МЦЫуЛњРДЭъГЩЁЃЭЈЙ§ЩЯвЛаЁНкЕФНщЩмЃЌЮвУЧПЩвдПДГіЃЌвЊЯыЗТецИУFPGAЩшМЦЃЌзюМђЕЅЕФЫМТЗОЭвЊЯыАьЗЈдкМЦЫуЛњЩЯФЃФтВњЩњГіЪОВЈЦїAЁЂBжаЫљЪОЕФВЈаЮЭМЃЌФЃФтГіFPGAаОЦЌЕФгыТпМЙІФмЃЌзюКѓдйФЃФтГіЪОВЈЦїAЁЂBЁЂCЕФНгЪеЙІФмЃЌгУРДЛцжЦЪфШыЁЂЪфГіаХКХЕФВЈаЮЭМВЂНјааНсЙћЗжЮіЁЃ

вдЩЯШ§ИіашвЊФЃФтЕФвЊЫижаЃЌFPGAЩшМЦЕФЙІФмДњТыЦфЪЕОЭЪЧЖдFPGAаОЦЌЙІФмзюКУЕФвЛИіФЃФтЃЌЖјЗТецЦїБОЩэОЭПЩвдФЃФтЪОВЈЦїЕФВЈаЮЙлВьЙІФмЃЌвђДЫЃЌЮЪЬтЕФНЙЕуОЭМЏжаЕНШчКЮдкМЦЫуЛњЩЯВњЩњаЮШчЪОВЈЦїAЁЂBжаЫљГЪЯжЕФМЄРјВЈаЮЩЯЁЃЕБШЛСЫЃЌНтОіЗНЗЈгаКмЖржжЃЌФуПЩвдЪЙгУЕЋВЛЯогкЁОБОЦЊ->ЗТецгяЗЈЁПеТНкжаЕФШЮКЮвЛжжгяЗЈЃЌВЛЙ§зюжБНгвВзюдЪМЕФЗНЗЈОЭЪЧЪжЖЏЛцжЦВЈаЮМЄРјЁЃНгЯТРДНЋеыЖдGraphic WaveformНјаавЛаЉЛљБОНщЩмЁЃ

ЁАHello worldЁБжЎGraphic Waveform

Д§ЗТецЩшМЦ

Д§ЗТецЩшМЦЕФЪ§зжЕчТЗдРэЭМШчЯТЃК

ЗТецЪОР§

ВЩгУGraphic WaveformЗНЗЈЖдFPGAЩшМЦНјааЗТецЪБЃЌЦфЗТецВЈаЮЕФЪфШывЛАуЖМЪЧЙЄОпЯрЙиЕФЃЌвђЮЊВЛЭЌЕФЗТецЙЄОпЬсЙЉВЛЭЌЕФВЈаЮИёЪНЁЂЛцжЦЗНЗЈКЭЗТецНчУцЁЃВЛЙ§ДѓЬхЕФВНжшШчЯТЃК

1ЁЂЧАЦкзМБИЙЄзїЃЛ

2ЁЂдкВЈаЮжаЬэМгЪфШыЖЫПкКЭД§ЙлВьЕФЪфГіЖЫПкЃЛ

3ЁЂЛцжЦЪфШыМЄРјВЈаЮЭМЃЌеыЖдБОР§ШчЯТЃК

4ЁЂЙлВьЪфГіЖЫПкЕФВЈаЮЃЌВЂОнДЫНјааБОДЮЗТецЗжЮіЃЌеыЖдБОР§ШчЯТЃК

ПЩвдПДГіЃЌдкЕкЖўИіЪБжгЩЯЩ§бижЎЧАЃЌЪфГіЮЊВЛЖЈЬЌЃЌетЪЧвђЮЊДЫЪБМФДцЦїAЁЂBжаЕФЪ§ОнВЂВЛШЗЖЈЃЈПЩвдЭЈЙ§дкДњТыжаИГГѕжЕЕФаЮЪНРДШЅЕєВЛЖЈЬЌЃЉЃЌВЛЙ§дкДЫжЎКѓЃЌЪфГіВЈаЮНсЙћгыдЄЦкЯрЗћЁЃ

вЛаЉЛцжЦВЈаЮЕФВйзї

БОаЁНкНщЩмвЛаЉЛљБОЕФВЈаЮЭМЛцжЦЕФВйзїЃЌЙЉДѓМвВЮПМЃК

ЬэМгЖЫПк

ЬэМгЖЫПкЪЧВЈаЮЭМЛцжЦЕФЕквЛВНЃЌвђЮЊУЛгаЪфШыЖЫПкЃЌФЧУДОЭУЛгаБЛЛцжЦЕФЖдЯѓЃЌЖјУЛгаЪфГіЖЫПкЃЌОЭУЛгаЗТецНсЙћЕФЯдЪОЖдЯѓЁЃВЛЙ§гыЪЕМЪжаЕФЕчТЗВтЪдВЛЭЌЃЌЗТецЕФЪБКђвВПЩвдНЋШЮвтFPGAЩшМЦЛђепЗТецДњТыжаЕФвЛаЉжаМфаХКХЬэМгЕНВЈаЮЭМжаНјааЙлВьЃЌетвВЪЧЗТецЯрЖдгкЪЕВтЕФСэвЛгХЪЦЁЃ

ДДНЈЪБжгаХКХ

Г§СЫДПзщКЯТпМЭтЃЌЭЈГЃFPGAЩшМЦЖМЪЧеыЖдЪБађТпМЕФЃЌвђДЫЪБжгаХКХдкећИіЩшМЦжаеМОнСЫЪЎЗжживЊЕФЕиЮЛЁЃгЩгкЪБжгаХКХОпгажмЦкадЁЂЮоЯоадЃЌвђДЫЦфЛцжЦЙЄзївВЪЧЗЧГЃОпгажиИДадЕФЃЌЫљвдЭЈГЃЮвУЧВЛжБНгЪжЖЏЛцжЦЪБжгаХКХЃЌЖјЪЧЭЈЙ§вЛаЉМђЕЅЩшжУРДдкВЈаЮЭМЩЯЩњГЩвЛИіЗћКЯЮвУЧвЊЧѓЕФЪБжгаХКХЁЃ

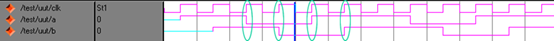

ЧЏжЦгыЪЭЗХаХКХ

ЖдгкЪ§ОнаХКХРДЫЕЃЌГ§СЫЪжЖЏЛцжЦЭтЃЌЭЈГЃгУЧЏжЦКЭЪЭЗХЕФЗНЗЈРДОЋШЗПижЦЁЃЧЏжЦКЭЪЭЗХвВЪЧЭЈЙ§МђЕЅЩшЖЈРДЪЕЯжЕФЃЌР§ШчЃЌдк100nsЪБПЬЃЌЧЏжЦаХКХaЮЊТпМ1ЃЌдк200nsКѓЪЭЗХЖдаХКХЕФЧЏжЦЃЌетбљЃЌдк100nsЪБПЬвдЧАКЭ200nsЪБПЬвдКѓЃЌОЭПЩвдЖдаХКХНјааВЛЭЌЕФЩшжУЁЃ

ЕчЦНЗзЊ

ДЫбЁЯювЛАугУгкКѓЦкЖдЗТецВЈаЮЕФаоИФЃЌЫќПЩвдЖдбЁжаЧјгђЕФВЈаЮЭМНјааЕчЦНЗзЊЃЌМДТпМ1БфЮЊТпМ0ЃЌТпМ0БфЮЊТпМ1ЁЃГ§ДЫвдЭтЃЌгавЛИіаЁММЧЩЃЌОЭЪЧдквЛПЊЪМСюФГвЛИіЪфШыЖЫПкЕФВЈаЮЭМШЋВПЮЊТпМ0ЛђТпМ1ЃЌетбљОЭПЩвдРћгУЕчЦНЗзЊВйзїРДбИЫйЕФЛцжЦГіЯывЊЕФВЈаЮМЄРјЁЃ

ЩњГЩЫцЛњађСа

гаЕФЪБКђЃЌЮвУЧашвЊвЛаЉБШНЯЫцЛњЕФЗТецМЄРјВЈаЮЃЌетЪБЃЌЪжЖЏЛцжЦЭљЭљЙЄзїСПЙ§ДѓЃЌДЫЪБЃЌПЩвдРћгУЩњГЩЫцЛњађСаЕФЙІФмбЁЯюЃЌОЙ§МђЕЅЩшжУВњЩњвЛаЉВЛЙцдђЕФЗТецМЄРјВЈаЮЁЃ

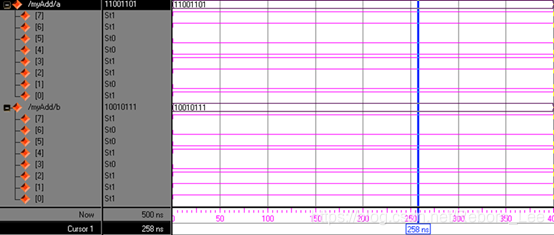

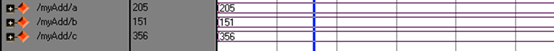

змЯпЩшжУ

гааЉЪБКђЃЌЪфШыаХКХЪЧЖрЮЛЕФЃЌР§ШчСНИі8bitsЮЛПэЕФЪ§ОнAКЭBЯрМгЁЃетИіЪБКђЃЌдкЛцжЦВЈаЮЭМЪБЃЌШчЙћеыЖдAЁЂBЙВ16ИљЪфШыЯпЗжБ№НјааВЈаЮЛцжЦЃЌдђЛсЗЧГЃЕФТщЗГЃЌвђДЫЃЌЗТецЦївЛАуЛсНЋЖрЮЛЪ§ОнаХКХПДзізмЯпЃЌДЫЪБЃЌЮвУЧПЩвдЗжБ№ЖдзмЯпAЁЂBНјааЭГвЛЕФЛцжЦВйзїЃЌЦфаЇЙћНЋЛсЗЧГЃЕФжБЙлЁЃР§ШчЯТЭМЃЌЭЈЙ§жБНгЮЊзмЯпAЁЂBЩшжУ8ЮЛ2НјжЦЪ§жЕЃЌОЭЯрЕБгкеыЖдУПвЛИљЪ§ОнЯпНјааЯргІЕФВЈаЮЛцжЦЁЃ

Г§вдЩЯНщЩмЕФМИЕуЭтЃЌЙигкВЈаЮЛцжЦЕФВйзїЛЙгаКмЖрЃЌДѓМвПЩвддкЪЕМЪЕФЪЙгУжаТ§Т§баОПЃЌетРяВЛдйзИЪіЁЃ

вЛаЉЙлВьВЈаЮЕФВйзї

БОаЁНкНщЩмвЛаЉЛљБОЕФВЈаЮЙлВьВйзїЃЌЙЉДѓМвВЮПМЃК

ВЈаЮЫѕЗХ

ВЈаЮЫѕЗХгІИУЫуЪЧЙлВьВЈаЮЪБзюЮЊГЃгУЕФвЛРрВйзїСЫЃЌгЩгкМЦЫуЛњЯдЪОЦСГпДчЕФЯожЦЃЌвдМАМЦЫуЛњФкДцЕФЯожЦЃЌЖдгкЗТецЪБМфБШНЯГЄЕФВЈаЮЭМЃЌМЦЫуЛњПЯЖЈЮоЗЈЭЌЪБНЋЫљгаЯИНкЖМЯдЪОГіРДЃЌетЪБКђЃЌОЭашвЊгУЕНВЈаЮЫѕЗХВйзїЃЌетРрЫЦгкЮвУЧгУМЦЫуЛњПДGoogleЕиЭМЪБЕФЫѕЗХВйзїЁЃ

змЯпЙлВь

ЭЈГЃЧщПіЯТЃЌзмЯпФЌШЯЖМЪЧвд2НјжЦЪ§ЕФаЮЪНРДБэЪОЕФЃЌШчЁОвЛаЉЛцжЦВЈаЮЕФВйзїЁПаЁНкжазюКѓЕФР§згЫљЪОЁЃГ§ДЫвдЭтЃЌЮЊСЫНјвЛВНЗНБуЮвУЧЙлВьВЈаЮЃЌЮвУЧЛЙПЩвдСюзмЯпЕФЯдЪОаЮЪНЮЊАЫНјжЦЁЂЪЎСљНјжЦЁЂЪЎНјжЦЕШЕШЃЌВЂЧвЛЙПЩИљОнашвЊСюЦфЯдЪОЮЊгаЗћКХЪ§ЛђепЮоЗћКХЪ§ЁЃР§ШчИУР§вВПЩБэЪОЮЊЃК

ЬэМгЪББъ

ЪББъОЭЪЧдкВЈаЮЭМЩЯЬэМгвЛЬѕЪњжБЕФзјБъЯпЃЌКЏЪ§БэДяЪНЮЊt=DЃЌЦфжаDЮЊФГвЛГЃЪ§ЁЃЪББъЪЧНјааВЈаЮЭМЙлВьЪБвЛжжКмКУЕФИЈжњЗНЪНЃЌЭЈЙ§в§ШыЖрИіЪББъЛЙПЩвдгУРДНјааТіГхВтСПЕШВйзїЃЌР§ШчЃК

БпбибАев

Ъ§зжВЈаЮЕФБфЛЏДІЭљЭљЪЧЮвУЧзюЙиаФЕФЮЛжУЃЌвђДЫЙлВьВЈаЮЪБЃЌвЛРрГЃгУЕФВйзїОЭЪЧБпбиВщевЃЌЦфжавдЬјзЊжСЯТвЛБпбиКЭЬјзЊжСЩЯвЛБпбиСНжжВйзїзюЮЊГЃгУЁЃзЂвтЃЌЖдгкзмЯпРраЭЕФЪ§ОнРДЫЕЃЌБпбижИЕФОЭЪЧЪ§ОнБфЛЏЕФЮЛжУЁЃ

Г§вдЩЯНщЩмЕФМИЕуЭтЃЌЙигкВЈаЮЙлВьЕФВйзїЛЙгаКмЖрЃЌДѓМвПЩвддкЪЕМЪЕФЪЙгУжаТ§Т§баОПЃЌетРяВЛдйзИЪіЁЃ

ВЈаЮЗТецНсЙћЗжЮіМАживЊзЂвтЪТЯю

дкЗжЮіЗТецНсЙћЪБЃЌгавЛаЉашвЊЬиБ№зЂвтЕФЕиЗНЃЌдкетРяЮЊДѓМвзівЛаЉЛљБОЕФНщЩмЁЃЧызЂвтЃЌБОаЁНкЕФФкШнВЛЙтЪЪгУгкGraphic WaveformЗНЗЈЃЌЖдгкЦфЫќгяЗЈаЮЪНЖМЪЪгУЁЃ

вЛЁЂШчЙћХаЖЯЗТецНсЙћЖдгыДэЃП

гаСНжжЗНЗЈЁЃЕквЛжжЃЌгУблОІПДЁЃетЪЧзюГЃгУЕФвЛжжЗНЗЈЃЌгЩгкЮвУЧЖдЪфГіВЈаЮЕФИёЪНгадЄЦкЃЌвђДЫЮвУЧПЩвджБНгЙлВьЗТецНсЙћРДХаЖЯБЛЗТецFPGAЩшМЦааЮЊЕФе§ШЗадЁЃЕкЖўжжЃЌВЈаЮБШНЯЃЌетжжЗНЗЈИќМгИпМЖвЛаЉЃЌЮвУЧПЩвдЯШЛцжЦГідЄЦкЕФЗТецНсЙћВЈаЮЃЌШЛКѓНЋИУВЈаЮгыЗТецНсЙћВЈаЮНјааЖдБШЃЌСНепВЛвЛжТЕФЕиЗНЛсвдКьЩЋЛђепИпССЯдЪОЃЌетбљИќЗНБуЮвУЧевЕНГіЮЪЬтЕФЕиЗНЁЃ

ЖўЁЂЗТец0ЪБПЬЕФвтвхЁЃ

ЪВУДЪЧЗТецЕФ0ЪБПЬЃПвЛАуРДЫЕЃЌФЌШЯЗТецзюПЊЪМЕФЪБПЬОЭЪЧЗТец0ЪБПЬЃЌвВОЭЪЧЕБФуЕуЛїПЊЪМЗТецАДХЅЕФФЧвЛЫВМфЃЌЗТец0ЪБПЬМЭдЊПЊЪМЁЃЧызЂвтЃЌЗТец0ЪБПЬЪЧвЛИіЯрЖджЕЃЌЖјВЛЪЧвЛИіОјЖдЕФжЕЃЌетРрЫЦгкЕчбЙжа0ЕчЪЦЕФЖЈвхЃЌживЊЕФВЛЪЧШЯЖЈЪВУДЪБКђВХЪЧ0ЪБПЬЃЌЖјЪЧашвЊШЗЖЈетУДвЛИіЪБПЬЃЌКУШУЫљгаЦфЫќЕФЪБПЬЖМПЩвдДЫЪБПЬЮЊЛљзМЃЌРДНјааУшЪіЁЃЭЈГЃРДЫЕЃЌетИіБЛШЗЖЈЕФЪБПЬГЦЮЊ0ЪБПЬЃЌЕБШЛСЫЃЌФувВПЩвдГЦжЎЮЊ1ЪБПЬЁЂ-1ЪБПЬЩѕжСNЪБПЬЃЌВЛЙ§ГЦжЎЮЊ0ЪБПЬИќгаРћгкЮвУЧЖдвЛаЉЪБМфИХФюЕФБэЪіКЭРэНтЁЃетОЭКУБШФуЗЧвЊЙцЖЈ0ЩуЪЯЖШЪЧЫЎЩеПЊЕФЮТЖШЃЌФЧУДдкДЫВЮееЯЕЯТЃЌ-100ЩуЪЯЖШЖдгІБљЫЎЛьКЯЮяЕФЮТЖШЃЌетВЂУЛгаЪВУДДэЮѓЃЌжЛВЛЙ§гыЮвУЧЭЈГЃЫљНгДЅЕНЕФИХФюгаЫљГіШыЃЌвђДЫРэНтЦ№РДЛсРЇФбаэЖрЁЃ

Ш§ЁЂЁАБпбиЖдБпбиЁБЕФХаЖЈЁЃ

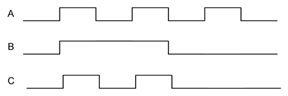

ЖдгкЪБађТпМЕФЗТецРДЫЕЃЌЕБГіЯжЪБжгаХКХЕФгааЇБпбиЪБЃЈвЛАуЪЧЩЯЩ§биЃЉЃЌЖдгІЕФЪ§ОнаХКХЕФТпМЕчЦНЛсБЛДЋЕнЕНМФДцЦїЕФЪфГіЖЫЃЌР§ШчЁАHello worldЁБаЁНкжаЕФЛцжЦЕФВЈаЮМЄРјЃЌЪБжгаХКХгыЪ§ОнаХКХЪЧвЛжжЁАБпбиЖдЕчЦНЁБЕФЙиЯЕЃЌвђДЫЖдгкМФДцЦїAЕФааЮЊФЃФтЮвУЧУЛгаШЮКЮвьвщЁЃПЩЪЧЃЌШчЙћЪБжгаХКХЕФгааЇБпбие§КУвВЖдгІЕНСЫЪ§ОнаХКХЕФБпбиЃЌгЩгкЮоЗЈЫЕЧхГўЪ§ОнаХКХДЫЪБЕНЕзЪЧТпМ1ЛЙЪЧТпМ0ЃЌМФДцЦїДЋЕнЕФаХКХЧщПігжИУЪЧдѕбљФиЃПЖдгкЙІФмЗТецРДЫЕЃЌИјГіШчЯТЭЈНтЃК

ШчЙћЪБжгБпбиЗЂЩњдкtЪБПЬЃЌФЧУДСюІЄЮЊе§ЮоЧюаЁЃЌдђБЛМФДцЦїДЋЕнЕФЪ§ОнТпМЕчЦНЫљДІЕФЪБПЬЮЊt-ІЄЪБПЬЁЃЖдгкЪБжггааЇБпбигыЪ§ОнаХКХЕФЫФжжЖдгІЙиЯЕСаОйШчЯТЃК

1ЁЂЪБжггааЇБпбиЖдгІЪ§ОнТпМ1ЕчЦНЃЌдђt-ІЄЪБПЬЕФЪ§ОнЯпЩЯШдЮЊТпМ1ЕчЦНЃЌетжжЧщПіЯТМФДцЦїЪфГіТпМ1ЕчЦНжСЦфЪфГіЖЫЃЛ

2ЁЂЪБжггааЇБпбиЖдгІЪ§ОнТпМ0ЕчЦНЃЌдђt-ІЄЪБПЬЕФЪ§ОнЯпЩЯШдЮЊТпМ0ЕчЦНЃЌетжжЧщПіЯТМФДцЦїЪфГіТпМ0ЕчЦНжСЦфЪфГіЖЫЃЛ

3ЁЂЪБжггааЇБпбие§КУЖдЦыЪ§ОнЯпЩЯДгТпМ1ЕНТпМ0ЕчЦНЕФЬјБфЃЌдђt-ІЄЪБПЬЕФЪ§ОнЯпЩЯгІИУЮЊТпМ1ЕчЦНЃЌетжжЧщПіЯТМФДцЦїЪфГіТпМ1ЕчЦНжСЦфЪфГіЖЫЃЛ

4ЁЂЪБжггааЇБпбие§КУЖдЦыЪ§ОнЯпЩЯДгТпМ0ЕНТпМ1ЕчЦНЕФЬјБфЃЌдђt-ІЄЪБПЬЕФЪ§ОнЯпЩЯгІИУЮЊТпМ0ЕчЦНЃЌетжжЧщПіЯТМФДцЦїЪфГіТпМ0ЕчЦНжСЦфЪфГіЖЫЃЛ

ШчЙћДѓМвзЂвтЙлВьЃЌЦфЪЕЁАHello worldЁБаЁНкжаМФДцЦїBЕФЪфШыЖЫХіЕНЕФОЭЪЧЁАБпбиЖдБпбиЁБЕФЧщПіЃЌЭЈЙ§ЙлВьЦфЪфШыЁЂЪфГіЖЫПкЕФЗТецВЈаЮЃЌЮвУЧПДЕНЦфНсЙћЗћКЯЩЯЪіЭЈНтЁЃ

ЩЯЪіЫФИіБъГіЕФЮЛжУДгзѓЕНгвЗжБ№ЖдгІгкЭЈНтжаЕФЙиЯЕ3ЁЂ2ЁЂ4ЁЂ1ЁЃ

ЪТЪЕЩЯЃЌЮвУЧе§ЪЧДгвЦЮЛМФДцЦїЫљгІОпгаЕФааЮЊЩЯЕУГіСЫЙІФмЗТецЪБМФДцЦїЕФЭЈНтЃЌЕЋЪЧЧызЂвтЃЌЯжЪЕжаЕФдвђЭљЭљетбљЕФЃКШчЙћЪБжгБпбиЗЂЩњдкtЪБПЬЃЌФЧУДСюІЄЮЊНЯаЁЕФе§бгГйЪБМфВЮЪ§ЃЈвЛАуЯрЖдгкЪБжгжмЦкРДЫЕНЯаЁЃЉЃЌдђМФДцЦїЃСЪфГіИќаТЕФЪБПЬЮЊt+ІЄЪБПЬЃЌдкВЛПМТЧЪБжгТЗОЖбгГйЕФЧщПіЯТЃЌМФДцЦїЃТЕФЪБжггааЇБпбиЪБПЬЮЊtЪБПЬЃЌЖдгІЕФЪ§ОнТпМЕчЦНЦфЪЕЛЙЪЧМФДцЦїЃСдкЃєЪБПЬЪфГіЕФТпМЕчЦНЃЌвђДЫЪ§ОнВХФмдквЦЮЛМФДцЦїжаж№ИіДЋЕнЯТШЅЁЃ

ПЩЪЧгЩгкЙІФмЗТецжаВЛПМТЧбгГйЃЌЫљвдМФДцЦїЃСЪфГіЕФИќаТЪБПЬШдЮЊЃєЪБПЬЃЌвђДЫдкетИіЪБКђЃЌЮЊСЫШЗЖЈМФДцЦїЃТЕФЪфГіЃЌОЭБиаызЗЫЗЕНt-ІЄЪБПЬЁЃ

зюКѓЃЌЧызЂвтЃЌЙІФмЗТецжаПЩвдГіЯжЁАБпбиЖдБпбиЁБЕФЧщПіЃЌвђЮЊЙІФмЗТецВЛПМТЧЪБМфбгГйВЮЪ§ЃЌжЛЪЧДгдРэЩЯРДбщжЄFPGAЩшМЦЃЌЕЋЪЧдкЪБађЗТецжаЃЌЁАБпбиЖдБпбиЁБЕФЧщПівЛАуЖМЪЧЛсгаЪБађЮЪЬтЕФЃЌЩѕжССНИіБпбиРыЕУЬЋНќЖМЛсЕМжТЩшМЦааЮЊЗЂЩњДэЮѓЁЃвђДЫЙІФмЗТецжаЕФГіЯжЁАБпбиЖдБпбиЁБЧщПігыЪЕМЪЕчТЗГіЯжЁАБпбиЖдБпбиЁБЕФЧщПіжЎМфУЛгаШЮКЮБиШЛСЊЯЕЃЌЫљвдВЛБиЕЃаФЫќЛсЕМжТМФДцЦїЕФНЈСЂЪБМфЛђБЃГжЪБМфгрСПВЛТњзуЁЃЮвМћЙ§гааЉШЫЃЌвђЮЊдкЙІФмЗТецЕФЪБКђЗЂЯжСЫЁАБпбиЖдБпбиЁБЕФЧщПіОЭЯыЕБШЛЕФСЊЯыЕНСЫвЛжЊАыНтЕФЪБађИХФюЃЌгкЪЧОЭИЯНєЖдМФДцЦїBЕФЪБжгзіИіЗДЯђЃЌДгЖјЧѓЕУаФРэЩЯЕФМЋДѓАВЮПгыТњзуЃЌЪтВЛжЊетбљзіЕФаЇЙћЭљЭљЪЪЕУЦфЗДЃЌЪЧЗЧГЃВЛПЩШЁЕФЁЃ