ЧАбд

БОЮФЪзЗЂздЃКFPGAТпМЩшМЦЛиЙЫЃЈ10ЃЉDDR/DDR2/DDR3жаЕФЪБађВЮЪ§ЕФКЌвх

ЩЯЦЊЮФеТЃКFPGAТпМЩшМЦЛиЙЫЃЈ9ЃЉDDRЕФЧАЪРНёЩњвдМАбнБфЙ§ГЬжаЕФММЪѕВювьгаЬсЕНЃЌжЦдьЩЬЛсвдвЛЯЕСагЩЦЦелКХИєПЊЕФЪ§зжРДаћВМДцДЂЪБађЃЈР§Шч5-5-5-5ЁЂ7-10-10-10ЕШЃЉЁЃ CASбгГйЪМжеЪЧетаЉађСажаЕФЕквЛИіЪ§зжЁЃ

ФЧЦфЫћЕФЪ§зжФиЃПетЦЊЮФеТЛсНВетаЉЪ§зжДњБэЕФКЌвхНВНтЧхГўЁЃ

ФкДцВЮЪ§БъЪЖКЌвх

DDRЁЂDDR2КЭDDR3ФкДцЪЧИљОнЦфЙЄзїЕФзюИпЫйЖШКЭЪБађРДЗжРрЕФЃЌЪБађЪЧ3-4-4-8ЁЂ5-5-5-15ЁЂ7-7-7-21Лђ9-9-9-24ЕШЪ§зжЃЌдНЕЭдНКУЁЃЯТУцНтЪЭетаЉЪ§зжЕФКЌвхЁЃ

DDRЁЂDDR2КЭDDR3ФкДцзёбDDRxxx/PCyyyyЗжРрЁЃ

ЕквЛИіЪ§зжxxxБэЪОИУФкДцаОЦЌжЇГжЕФзюИпЪБжгЫйЖШЁЃР§ШчЃЌDDR400ФкДцЕФзюИпЙЄзїЦЕТЪЮЊ400MHzЃЌDDR2-800ЕФзюИпЙЄзїЦЕТЪЮЊ800MHzЃЌDDR3-1333ЕФзюИпЙЄзїЦЕТЪЮЊ1,333MHzЁЃашвЊзЂвтЕФЪЧЃЌетВЂВЛЪЧФкДцЕФецЪЕЪБжгЫйЖШЁЃDDRЁЂDDR2КЭDDR3ФкДцЕФЪЕМЪЪБжгЪЧБъзЂЪБжгЫйЖШЕФвЛАыЁЃвђДЫDDR400ФкДцЕФЙЄзїЦЕТЪЮЊ200MHzЃЌDDR2-800ФкДцЕФЙЄзїЦЕТЪЮЊ400MHzЃЌDDR3-1333ФкДцЕФЙЄзїЦЕТЪЮЊ666MHzЁЃ

ЕкЖўИіЪ§зжБэЪОИУФкДцДяЕНЕФзюДѓДЋЪфЫйТЪЃЌЕЅЮЛЮЊMB/sЁЃDDR400ФкДцДЋЪфЪ§ОнЕФЫйЖШзюИпЮЊ3,200MB/sЃЌвђДЫБЛБъМЧЮЊPC3200ЁЃDDR2-800ФкДцДЋЪфЪ§ОнЕФЫйЖШЮЊ6400MB/sЃЌЫћУЧБЛБъзЂЮЊPC2-6400ЁЃЖјDDR3-1333ФкДцПЩвдвд10664MB/sЕФЫйЖШДЋЪфЪ§ОнЃЌЫќУЧБЛБъзЂЮЊPC3-10600ЛђPC3-10666ЁЃе§ШчФуЫљПДЕНЕФЃЌЮвУЧдк "DDR "Лђ "PC "КѓУцгУЪ§зж "2 "Лђ "3 "РДБэЪОЮвУЧЫЕЕФЪЧDDR2ЛђDDR3ФкДцЃЌЖјВЛЪЧDDRЁЃ

ЕквЛИіЗжРрЃЌDDRxxxЃЌЪЧгУРДЛЎЗжФкДцаОЦЌЕФБъзМЃЌЖјЕкЖўИіЗжРрЃЌPCyyyyЃЌЪЧгУРДЛЎЗжФкДцФЃПщЕФБъзМЁЃ

етдкЩЯвЛЦЊЮФеТжавВЫЕСЫЃК

ДгРэТлЩЯНВЃЌИУУќУћЯЕЭГDDRx-yyyyЃЈЦфжаxЪЧММЪѕЪРДњЃЌyyyyЪЧDDRЪБжгЫйТЪЃЉНігУгкДцДЂаОЦЌЁЃФкДцФЃПщЃЈгУгкКИНгФкДцаОЦЌЕФаЁгЁЫЂЕчТЗАхЃЉЪЙгУВЛЭЌЕФУќУћЯЕЭГЃКPCx-zzzzЃЌЦфжаxЪЧММЪѕДњКХЃЌzzzzЪЧзюДѓРэТлДЋЪфЫйТЪЃЈгжГЦзюДѓДјПэЃЉЁЃ

ЯТЭМжаЃЌПЩвдПДЕНвЛИіPC3-10666ФкДцФЃПщЃЌЫќЪЙгУЕФЪЧDDR3-1333ФкДцаОЦЌЁЃзЂвтЪБађЃЈ7-7-7-18ЃЉКЭЕчбЙЃЈ1.5VЃЉЁЃ

ДцДЂЦїФЃПщЕФзюДѓДЋЪфЫйТЪПЩвдЭЈЙ§вдЯТЙЋЪНМЦЫуЁЃ

- зюДѓРэТлДЋЪфТЪ = ЪБжг x ЮЛЪ§ / 8

гЩгкDIMMФЃПщвЛДЮДЋЪф64ЮЛЃЌЫљвд "ЮЛЪ§ "НЋЪЧ64ЮЛЁЃгЩгк64 / 8 = 8ЃЌЮвУЧПЩвдНЋетИіЙЋЪНМђЛЏЮЊЁЃ

- зюДѓРэТлДЋЪфТЪ = ЪБжг x 8 Ё

ШчЙћНЋФкДцФЃПщАВзАдкФкДцзмЯпвдНЯЕЭЕФЪБжгЫйТЪдЫааЕФЯЕЭГЩЯЃЌФкДцФЃПщЪЕЯжЕФзюДѓДЋЪфЫйТЪНЋЕЭгкЦфРэТлЩЯЕФзюДѓДЋЪфЫйТЪЁЃЪЕМЪЩЯЃЌетЪЧвЛИіЗЧГЃГЃМћЕФЮѓХаЁЃ

БШШчЫЕЃЌФуТђСЫвЛЖдDDR3-2133/PC3-17000ФкДцЁЃОЁЙмЫќУЧБЛБъзЂЮЊDDR3-2133ЃЌЕЋЫќУЧВЛЛсдкФуЕФЯЕЭГЩЯвд2133MHzЕФЫйЖШздЖЏдЫааЁЃетЪЧЫќУЧжЇГжЕФзюДѓЪБжгЫйТЪЃЌЖјВЛЪЧЫќУЧдЫааЕФЪБжгЫйТЪЁЃШчЙћФуНЋЫќАВзАдкжЇГжDDR3ФкДцЕФЦеЭЈPCЯЕЭГЩЯЃЌЫќУЧПЩФмЛсвд1,333 MHz(DDR3-1333)ЕФЫйЖШдЫааЈCетЪЧDDR3ЕФзюИпБъзМЫйЖШЈCЪЕЯж10,664 MB/sЕФзюДѓДЋЪфЫйТЪЁЃЫљвдЃЌЫќУЧВЛЛсздЖЏдЫаадк2,133 MHzЃЌвВВЛЛсздЖЏДяЕН17,000 MB/ДЋЪфЫйТЪЁЃ

ФЧУДЃЌЮЊЪВУДгаШЫЛсТђетаЉФЃПщЃПгаШЫЛсТђЫћУЧЕФГЌЦЕЁЃгЩгкжЦдьЩЬБЃжЄетаЉФЃПщНЋдЫааЕН2,133езКеЃЌФужЊЕРФуПЩвдЬсИпФкДцзмЯпЪБжгЕН1,066езКеЃЌвдЪЕЯжИќИпЕФадФмгыФњЕФЯЕЭГЃЌЕЋЪЧЃЌФуЕФжїАхБиаыжЇГжетжжГЌЦЕЁЃвђДЫЃЌШчЙћФњВЛДђЫуЖдЯЕЭГНјааГЌЦЕЃЌФЧУДЙКТђБъЪОЪБжгЦЕТЪИпгкЯЕЭГжЇГжЕФФкДцФЃПщЪЧУЛгагУЕФЁЃ

ЖдгкЦеЭЈгУЛЇРДЫЕЃЌетОЭЪЧФуашвЊжЊЕРЕФЙигкDDRЁЂDDR2КЭDDR3ФкДцЕФвЛЧаЁЃЖдгкИпМЖгУЛЇРДЫЕЃЌЛЙгаСэвЛИіЬиЕуЃКФкДцЕФЪБађЛђбгГйЁЃ

ФкДцЪБађВЮЪ§КЌвх

гЩгкЪБађЕФдвђЃЌСНИіРэТлЩЯзюДѓДЋЪфЫйТЪЯрЭЌЕФФкДцФЃПщПЩвдДяЕНВЛЭЌЕФадФмЫЎЦНЁЃЮЊЪВУДдкСНепвдЯрЭЌЕФЪБжгЫйТЪдЫааЕФЧщПіЯТЛсГіЯжетжжЧщПіЃП

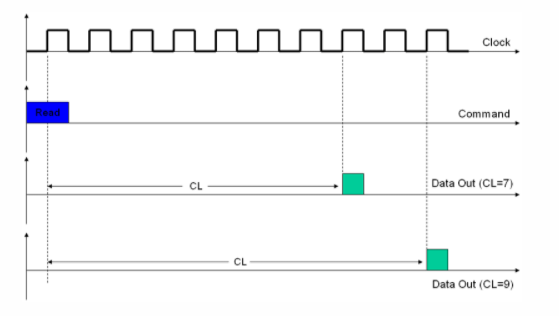

ЪБађКтСПЕФЪЧФкДцаОЦЌдкФкВПзіФГЪТЕФбгГйЪБМфЁЃЯТУцЪЧвЛИіР§згЁЃПМТЧЕНзюжјУћЕФВЮЪ§ЃЌЫќБЛГЦЮЊCAS LatencyЃЈЛђCLЛђ ЁАЗУЮЪЪБМфЁБЃЌЁАСабЁЭЈбгГйЁБЃЉЃЌЫќИцЫпЮвУЧФкДцФЃПщдкЗЕЛиCPUЧыЧѓЕФЪ§ОнЪБНЋбгГйЖрЩйИіЪБжгжмЦкЁЃвЛИіCLЮЊ9ЕФФкДцФЃПщНЋбгГй9ИіЪБжгжмЦкРДЬсЙЉЧыЧѓЕФЪ§ОнЃЌЖјвЛИіCLЮЊ7ЕФФкДцФЃПщНЋбгГй7ИіЪБжгжмЦкРДЬсЙЉЪ§ОнЁЃЫфШЛетСНИіФЃПщПЩФмвдЯрЭЌЕФЪБжгЫйТЪдЫааЃЌЕЋЕкЖўИіФЃПщЕФЫйЖШЛсИќПьЃЌвђЮЊЫќНЋБШЕквЛИіФЃПщИќПьЕиНЛИЖЪ§Он.етИіЮЪЬтБЛГЦЮЊ ЁАбгГйЁБЁЃе§ШчФудкЯТЭМжаПДЕНЕФЃЌФЧРяЕФФЃПщЕФCLЮЊ7ЁЃ

ФкДцЪБађЪЧЭЈЙ§вЛЯЕСаЪ§зжИјГіЕФЃЌР§ШчЃЌ4-4-4-8,5-5-5-15,7-7-7-21Лђ9-9-9-24ЁЃетаЉЪ§зжБэЪОФкДцжДааФГЯюВйзїЫљашЕФЪБжгжмЦкЪ§ЁЃЪ§зждНаЁЃЌФкДцЕФЫйЖШдНПьЁЃЩЯЭМУшЛцЕФФкДцФЃПщЕФЪБађЮЊ7-7-7-18ЃЌЯТЭМжаУшЛцЕФФкДцФЃПщЕФЪБађЮЊ8-8-8-24ЁЃ

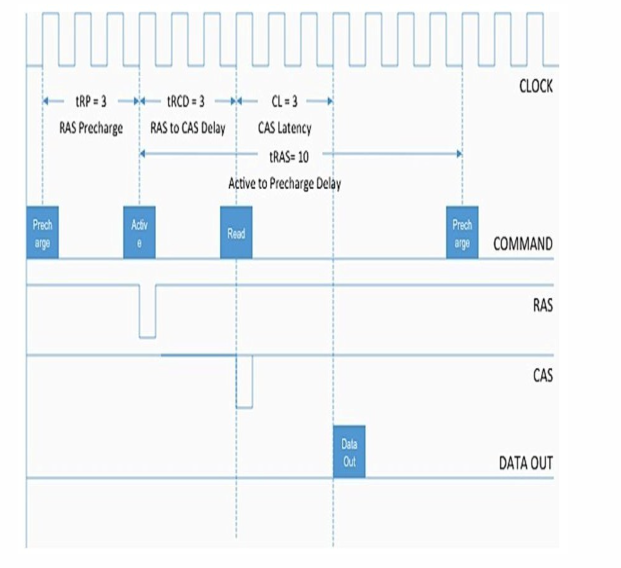

етаЉЪ§зжЫљБэЪОЕФВйзїШчЯТЁЃCL -tRCD -tRP -tRAS -CMDЁЃвЊРэНтЫќУЧЃЌЧыМЧзЁЃЌДцДЂЦїЕФФкВПзщжЏЪЧвЛИіОиеѓЃЌЪ§ОнДцДЂдкааКЭСаЕФНЛЕуДІЁЃ

CASбгГй(CL)

CAS Latency(CL)ЪЧзюжјУћЕФФкДцВЮЪ§ЃЌЫќИцЫпЮвУЧФкДцНЋбгГйЖрЩйИіЪБжгжмЦкРДДЋЫЭЫљЧыЧѓЕФЪ§ОнЃЌвЛИіCL=7ЕФФкДцНЋбгГй7ИіЪБжгжмЦкРДДЋЫЭЪ§ОнЃЌЖјCL=9ЕФФкДцНЋбгГй9ИіЪБжгжмЦкРДжДааЭЌбљЕФВйзїЁЃвђДЫЃЌЖдгквдЯрЭЌЪБжгЫйТЪдЫааЕФСНИіФкДцФЃПщРДЫЕЃЌCLжЕзюЕЭЕФФЧИіФЃПщЛсИќПьЁЃ

ЧызЂвтЃЌетРяЕФЪБжгЫйТЪЪЧФкДцФЃПщдЫааЪБЕФЪЕМЪЪБжгЫйТЪЃЌМДЖюЖЈЪБжгЫйТЪЕФвЛАыЁЃгЩгкDDRЁЂDDR2КЭDDR3ФкДцдкУПИіЪБжгжмЦкФкПЩвдЬсЙЉСНИіЪ§ОнЃЌвђДЫЫќУЧЕФЖюЖЈЪБжгЫйТЪЪЧЪЕМЪЪБжгЫйТЪЕФСНБЖЁЃ

ЯТЭМжаЃЌПЩвдПДЕНCLЕФЙЄзїдРэЁЃЮвУЧОйСЫСНИіР§згЃЌвЛИіЪЧCL=7ЕФФкДцФЃПщЃЌвЛИіЪЧCL=9ЕФФкДцФЃПщЁЃРЖЩЋЕФУќСюНЋЪЧвЛИі "ЖС "ЕФУќСюЁЃ

ПМТЧЕНСНепдкЯрЭЌЕФЪБжгЫйТЪЯТдЫааЃЌCL=7ЕФФкДцНЋБШCL=9ЕФФкДцбгГйЬсИп22.2%ЁЃ

ФуЩѕжСПЩвдМЦЫуГіФкДцбгГйЕНПЊЪМДЋЪфЪ§ОнЕФЪБМфЃЌУПИіЪБжгжмЦкЕФжмЦкПЩвдЭЈЙ§ЙЋЪНЧсЫЩМЦЫуГіРДЁЃ

T = 1 / f

вђДЫЃЌDDR3-1333ФкДцдк1333 MHzЃЈ666.66 MHzЪБжгЃЉЯТдЫааЕФУПИіЪБжгжмЦкЕФжмЦкЮЊ1.5 nsЃЈns=ФЩУыЃЛ1 ns=0.000000001 sЃЉЁЃЫљвдЃЌетИіDDR3-1333ФкДцШчЙћCL=7ЕФЛАЃЌЛсбгГй10.5 nsПЊЪМДЋЪфЪ§ОнЃЌШчЙћCL=9ЕФЛАЃЌдђбгГй13.5 nsЁЃ

RASЕНCASбгГй(tRCD)

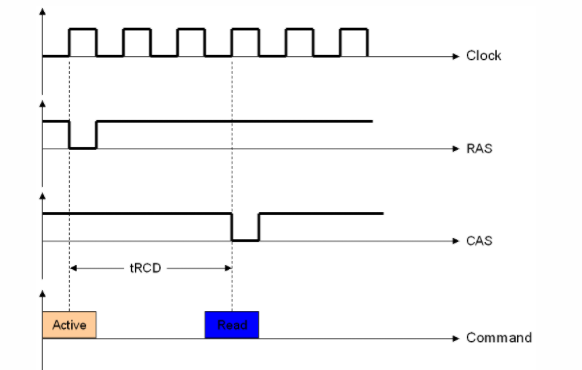

УПИіДцДЂаОЦЌФкВПЖМЪЧвдОиеѓЕФаЮЪНзщжЏЕФЁЃдкУПвЛааКЭУПвЛСаЕФНЛВцЕуЃЌЮвУЧгавЛИіаЁЕчШнЃЌИКд№ДцДЂ "0 "Лђ ЁА1ЁБЈCЪ§ОнЁЃдкДцДЂЦїФкВПЃЌЗУЮЪДцДЂЪ§ОнЕФЙ§ГЬЪЧЭЈЙ§ЯШМЄЛюааЃЌдйМЄЛюСаРДЭъГЩЕФЁЃетжжМЄЛюЪЧЭЈЙ§СНИіПижЦаХКХРДЭъГЩЕФЃЌетСНИіаХКХБЛГЦЮЊRAS(Row AddressStrobe)КЭCAS(Column Address Strobe)ЁЃетСНИіаХКХжЎМфЕФЪБМфМфИєдНЖЬдНКУЃЌвђЮЊЪ§ОнЛсБЛИќПьЕиЖСШЁЁЃRASЕНCASбгГйЛђtRCDВтСПетИіЪБМфЁЃШчЯТЭМЃЌЮвУЧЫЕУїСЫетвЛЕуЃЌЯдЪОСЫвЛИіФкДцЃЌRCD=3ЁЃ

е§ШчФњЫљПДЕНЕФЃЌRASЕНCASбгГйвВЪЧ "ЛюЖЏ "УќСюКЭ "ЖС "Лђ "аД "УќСюжЎМфЕФЪБжгжмЦкЪ§ЁЃ

гыCAS LatencyвЛбљЃЌRASЕНCAS DelayЕФЙЄзїдРэЪЧФкДцЪЕМЪЪБжгЃЈЪЧБъМЧЪБжгЕФвЛАыЃЉЁЃИУВЮЪ§дНЕЭЃЌФкДцЫйЖШдНПьЃЌвђЮЊЫќНЋИќдчЕиПЊЪМЖСШЁЛђаДШыЪ§ОнЁЃ

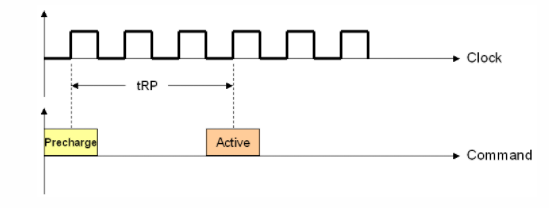

RASдЄГфЕч(tRP)

ДгФкДцжаШЁГіЪ§ОнКѓЃЌашвЊЗЂГівЛЬѕУћЮЊPrechargeЕФУќСюЃЌЙиБее§дкЪЙгУЕФФкДцааЃЌдЪаэаТЕФааБЛМЄЛюЁЃRASдЄГфЕчЪБМф(tRP)ЪЧжИДгPrechargeУќСюЕНЯТвЛИіActiveУќСюПЩвдЗЂГіЕФЪБМфЁЃе§ШчжЎЧАЫљСЫНтЕНЕФЃЌActiveУќСюЦєЖЏСЫвЛИіЖСЛђаДжмЦкЁЃ

ЩЯЭМжаЃЌЮвУЧвдtRP=3ЕФДцДЂЦїЮЊР§ЁЃ

гыЦфЫћВЮЪ§вЛбљЃЌRASдЄГфЕчгыФкДцЪЕМЪЪБжгЃЈЪЧБъзЂЪБжгЕФвЛАыЃЉвЛЦ№ЙЄзїЁЃетИіВЮЪ§дНЕЭЃЌФкДцЕФЫйЖШОЭдНПьЃЌвђЮЊЫќЛсИќдчЕиЗЂГіActiveУќСюЁЃ

МгЩЯЮвУЧЫљПДЕНЕФвЛЧаЃЌДгЗЂГіPrechargeУќСюЕНЪЕМЪЕУЕНЪ§ОнжЎМфЕФЪБМфНЋЪЧtRP + tRCD + CLЁЃ

ЦфЫћВЮЪ§

ЮвУЧдйРДПДПДСэЭтСНИіВЮЪ§ЃЌActive to Precharge DelayЃЈtRASЃЉКЭCommand RateЃЈCMDЃЉЁЃгыЦфЫћВЮЪ§вЛбљЃЌетСНИіВЮЪ§гыФкДцЪЕМЪЪБжгЃЈМДФкДцБъЪОЪБжгЕФвЛАыЃЉгаЙиЁЃетаЉВЮЪ§дНЕЭЃЌФкДцЕФЫйЖШОЭдНПьЁЃ

ActiveЕНдЄГфЕчбгГйЃЈtRASЃЉЁЃЗЂГівЛЬѕActiveУќСюКѓЃЌдкtRASЙ§КѓВХФмЗЂГіСэвЛЬѕPrechargeУќСюЁЃЫљвдЃЌетИіВЮЪ§ЯожЦСЫФкДцКЮЪБПЩвдПЊЪМЖСШЁЃЈЛђаДШыЃЉВЛЭЌЕФааЁЃ

УќСюЫйТЪЃЈCMDЃЉЁЃЫќЪЧжИФкДцаОЦЌДгБЛМЄЛюЃЈЭЈЙ§CS-аОЦЌбЁдё-в§НХЃЉЕНПЩвдЯђФкДцЗЂГіШЮКЮУќСюЫљашЕФЪБМфЁЃИУВЮЪ§ДјгазжФИ ЁАTЁБЁЃПЩФмЕФжЕЪЧ1TЛђ2TЃЌЗжБ№БэЪОвЛИіЪБжгжмЦкЛђСНИіЪБжгжмЦкЁЃ

ЮЊСЫИќКУЕиРэНтЃЌЯТЭМЮЊЪБађВЮЪ§ЮЊ3-3-3-10ЃЈМйЩшЃЉЕФДцДЂЦїЕФЪБађЭМЁЃ

дкЮФеТЕФзюКѓЃЌЮвУЧПЩвдНЋЪБађВЮЪ§змНсШчЯТЁЃ

-

CASбгГй(CL)ЪЧжИдке§ШЗЕФаавбОДђПЊЕФЧщПіЯТЃЌДгDRAMжаЖСШЁЕквЛИіФкДцЮЛЫљашЕФЪБМфЁЃ

-

дкУЛгаШЮКЮЛюЖЏааЕФЧщПіЯТЃЌДгDDRжаЖСШЁЕквЛИіФкДцЮЛЕФЪБМфЮЊtRCD+CLЁЃ

-

ДгвЛИіУЛгаЛюЖЏааЕФDRAMжаЖСШЁЕквЛИіФкДцЮЛЕФЪБМфЪЧtRP + tRCD + CLЁЃ

-

ДгЗЂГі "ЛюЖЏ "УќСюЕНЗЂГі "дЄГфЕч "УќСюЫљашЕФЪБжгжмЦкЪ§ЮЊtRASЁЃ

етаЉаХЯЂЖМПЩвдДгЩЯЭМжаЕУЕНЁЃ