Lec04 Page tables бЇЯАБЪМЧ

АВзАРЯЪІЕФТпМ

ДгЕижЗПеМф гВМў ащФтФкДцДњТы

3ИіЗНУцећРэСЫвЛЯТПЮГЬФкШн

ЮФеТФПТМ

-

- НёЬьЕФПЮГЬжаЃЌЮвУЧЯыЙизЂЕФЪЧФкДцЕФИєРыадЁЃ

- ЕижЗПеМфЃЈAddress SpacesЃЉ

-

- ГѕВНЪЕЯжЕижЗзЊЛЛЃЈРэЯыЛЏЃЉ

- ЪЕМЪЩЯвГБэШчКЮЙЄзї

-

- ЕижЗзЊЛЛБэЪЧвдpageЮЊСЃЖШ(ВЛЪЧЕижЗ)

- page tableЪЧвЛИіЖрМЖЕФНсЙЙ(НкЪЁПеМф)

- PTEжаЕФflag

- вГБэЛКДцЃЈTranslation Lookaside BufferЃЉ

- жЇГжащФтФкДцЕФгВМў

-

- Kernel Page Table

- kernel stack КЭ ШЈЯо

- XV6жаЕФащФтФкДцДњТы

-

- kvminit КЏЪ§

- kvminithart КЏЪ§

- walk КЏЪ§

-

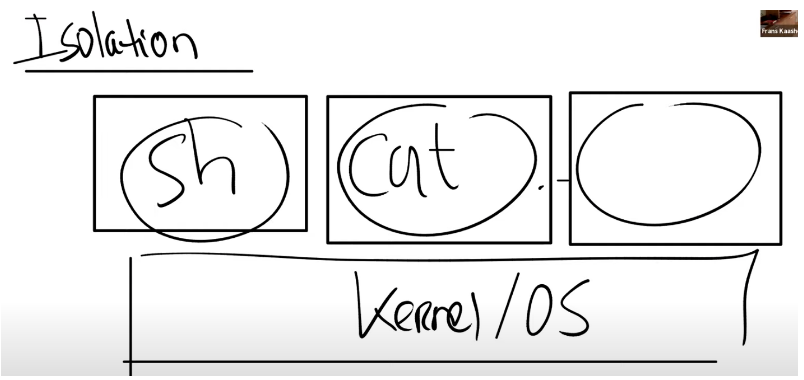

НёЬьЕФПЮГЬжаЃЌЮвУЧЯыЙизЂЕФЪЧФкДцЕФИєРыадЁЃ

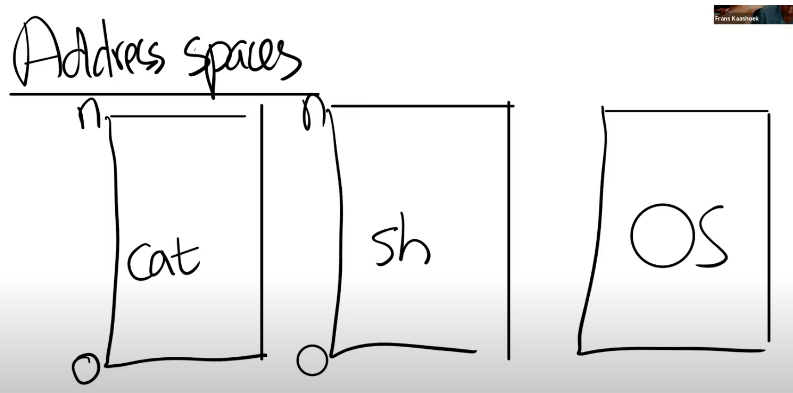

ЕижЗПеМфЃЈAddress SpacesЃЉ

ЮвУЧЦкЭћДгИєРыаджаЕУЕНЪВУДбљЕФаЇЙћ

- УПИігУЛЇГЬађЖМБЛзАНјвЛИіКазгРяЃЌетбљЫќУЧОЭВЛЛсБЫДЫгАЯьСЫЁЃРрЫЦЕФЃЌЮвУЧвВЯыШУЫќУЧгыФкКЫВйзїЯЕЭГЯрЛЅЖРСЂЃЌетбљШчЙћФГИігІгУГЬађЮовтЛђепЙЪвтзіСЫвЛаЉЛЕЪТЃЌвВВЛЛсгАЯьЕНВйзїЯЕЭГЁЃ

ЮЊСЫЗРжЙcatКЭshell ЛьТв

- ЮвУЧИјАќРЈФкКЫдкФкЕФЫљгаГЬађзЈЪєЕФЕижЗПеМфЁЃЫљвдЃЌЕБЮвУЧдЫааcatЪБЃЌЫќЕФЕижЗПеМфДг0ЕНФГИіЕижЗНсЪјЁЃЕБЮвУЧдЫааShellЪБЃЌЫќЕФЕижЗвВДг0ПЊЪМЕНФГИіЕижЗНсЪјЁЃФкКЫЕФЕижЗПеМфвВДг0ПЊЪМЕНФГИіЕижЗНсЪјЁЃ

ШчЙћcatГЬађЯывЊЯђЕижЗ1000аДШыЪ§ОнЃЌФЧУДcatжЛЛсЯђЫќздМКЕФЕижЗ1000ЃЌЖјВЛЪЧShellЕФЕижЗ1000аДШыЪ§ОнЁЃЫљвдЃЌЛљБОЩЯРДЫЕЃЌУПИіГЬађЖМдЫаадкздМКЕФЕижЗПеМфЃЌВЂЧветаЉЕижЗПеМфБЫДЫжЎМфЯрЛЅЖРСЂЁЃ**дкетжжВЛЭЌЕижЗПеМфЕФИХФюжаЃЌcatГЬађЩѕжСЖМВЛОпБИв§гУЪєгкShellЕФФкДцЕижЗЕФФмСІЁЃ**етЪЧЮвУЧЯывЊДяГЩЕФжеМЋФПБъЃЌвђЮЊетжжЗНЪНЮЊЮвУЧЬсЙЉСЫЧПИєРыадЃЌcatЯждкВЛФмв§гУШЮКЮВЛЪєгкздМКЕФФкДцЁЃ

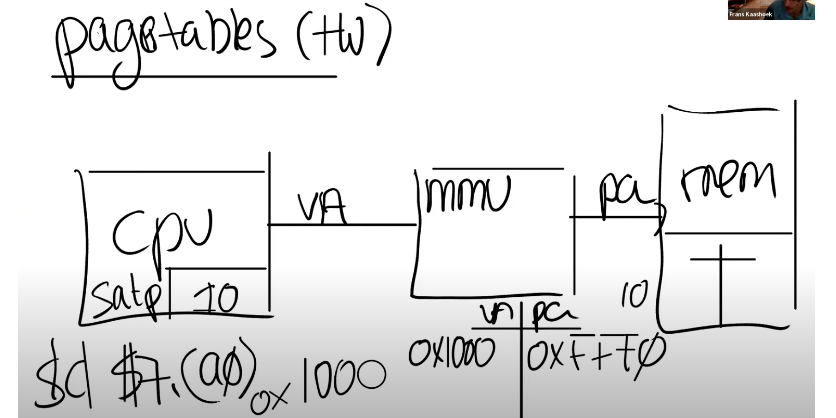

ГѕВНЪЕЯжЕижЗзЊЛЛЃЈРэЯыЛЏЃЉ

ШчКЮЪЕЯжЩЯЪіЕФЕижЗПеМфЃПдквЛИіЮяРэФкДцЩЯЃЌДДНЈВЛЭЌЕФЕижЗПеМф

- зюГЃМћЕФЗНЗЈЃЌЭЌЪБвВЪЧЗЧГЃСщЛюЕФвЛжжЗНЗЈОЭЪЧЪЙгУвГБэЃЈPage TablesЃЉЁЃвГБэЪЧдкгВМўжаЭЈЙ§ДІРэЦїКЭФкДцЙмРэЕЅдЊЃЈMemory Management UnitЃЉЪЕЯж

ЪЕЯжЙ§ГЬ

SD АбСНИізжНкЕФЪ§ОнДгМФДцЦїДцДЂЕНДцДЂЦїжа

SD $7, a0(R2)

-

ЖдгкШЮКЮвЛЬѕДјгаЕижЗЕФжИСюЃЌЦфжаЕФЕижЗгІИУШЯЮЊЪЧащФтФкДцЕижЗЖјВЛЪЧЮяРэЕижЗЁЃМйЩшМФДцЦїa0жаЪЧЕижЗ0x1000ЃЌФЧУДетЪЧвЛИіащФтФкДцЕижЗЁЃащФтФкДцЕижЗЛсБЛзЊЕНФкДцЙмРэЕЅдЊЃЈMMUЃЌMemory Management UnitЃЉ

-

ФкДцЙмРэЕЅдЊЛсНЋащФтЕижЗЗвыГЩЮяРэЕижЗЁЃжЎКѓетИіЮяРэЕижЗЛсБЛгУРДЫїв§ЮяРэФкДцЃЌВЂДгЮяРэФкДцМгдиЃЌЛђепЯђЮяРэФкДцДцДЂЪ§ОнЁЃ

-

ДгCPUЕФНЧЖШРДЫЕЃЌвЛЕЉMMUДђПЊСЫЃЌЫќжДааЕФУПЬѕжИСюжаЕФЕижЗЖМЪЧащФтФкДцЕижЗЁЃ

-

ЮЊСЫФмЙЛЭъГЩащФтФкДцЕижЗЕНЮяРэФкДцЕижЗЕФЗвыЃЌ**MMUЛсШЅВщПДвЛИіБэЕЅЃЌБэЕЅжаЃЌвЛБпЪЧащФтФкДцЕижЗЃЌСэвЛБпЪЧЮяРэФкДцЕижЗЁЃОйИіР§згЃЌащФтФкДцЕижЗ0x1000ЖдгІСЫвЛИіЮвЫцПкЫЕЕФЮяРэФкДцЕижЗ0xFFF0ЁЃ**етбљЕФБэЕЅПЩвдЗЧГЃСщЛюЁЃ

-

**ЭЈГЃРДЫЕЃЌФкДцЕижЗЖдгІЙиЯЕЕФБэЕЅвВБЃДцдкФкДцжаЁЃЫљвдCPUжаашвЊгавЛаЉМФДцЦїгУРДДцЗХБэЕЅдкЮяРэФкДцжаЕФЕижЗЁЃ**ЯждкЃЌдкФкДцЕФФГИіЮЛжУБЃДцСЫЕижЗЙиЯЕБэЕЅЃЌЮвУЧМйЩшетИіЮЛжУЕФЮяРэФкДцЕижЗЪЧ0x10ЁЃФЧУДдкRISC-VЩЯвЛИіНазіSATPЕФМФДцЦїЛсБЃДцЕижЗ0x10ЁЃ

етбљЃЌCPUОЭПЩвдИцЫпMMUЃЌПЩвдДгФФевЕННЋащФтФкДцЕижЗЗвыГЩЮяРэФкДцЕижЗЕФБэЕЅЁЃ -

УПИігІгУГЬађЖМгаздМКЖРСЂЕФБэЕЅЃЌВЂЧветИіБэЕЅЖЈвхСЫгІгУГЬађЕФЕижЗПеМфЁЃЫљвдЕБВйзїЯЕЭГНЋCPUДгвЛИігІгУГЬађЧаЛЛЕНСэвЛИігІгУГЬађЪБЃЌЭЌЪБвВашвЊЧаЛЛSATPМФДцЦїжаЕФФкШнЃЌДгЖјжИЯђаТЕФНјГЬБЃДцдкЮяРэФкДцжаЕФЕижЗЖдгІБэЕЅЁЃ

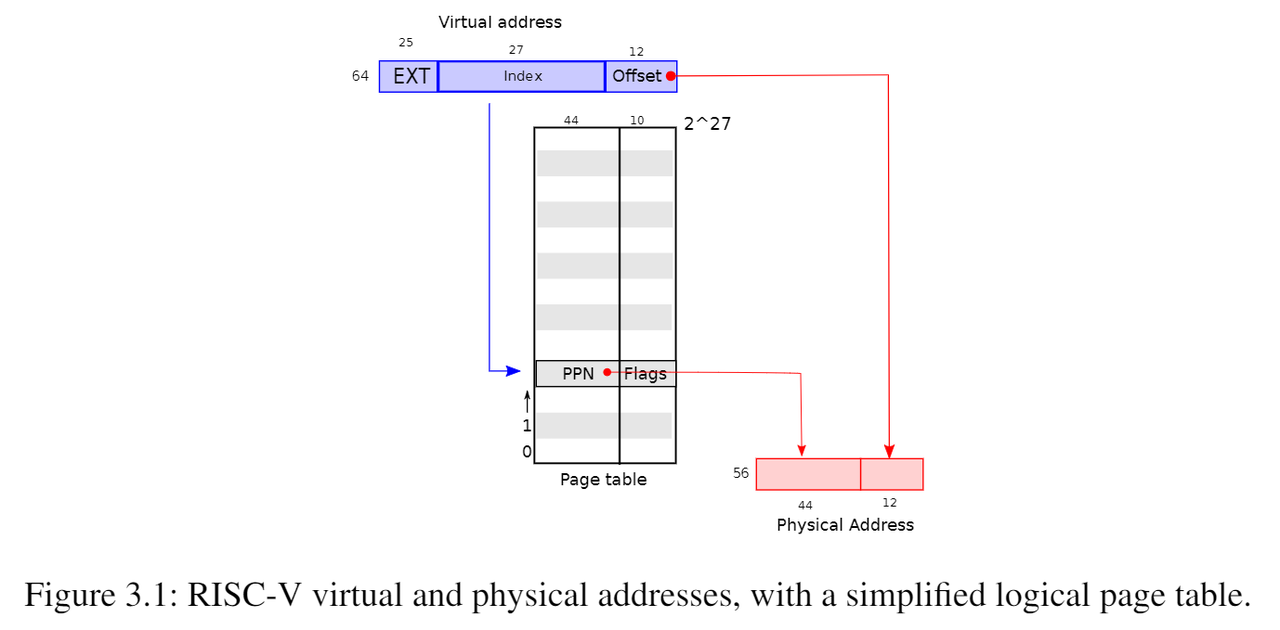

ЪЕМЪЩЯвГБэШчКЮЙЄзї

- дкRISC-VЩЯЛсгаЖрЩйЕижЗЃЌЛђепвЛИіМФДцЦїПЩвдБЃДцЖрЩйИіЕижЗЃПМФДцЦїЪЧ64bitЕФЃЌЫљвдгаЖрЩйИіЕижЗФиЃПЪЧЕФЃЌ2^64ИіЕижЗЃЌЫљвдШчЙћЮвУЧвдЕижЗЮЊСЃЖШРДЙмРэЃЌБэЕЅЛсБфЕУЗЧГЃОоДѓЁЃЪЕМЪЩЯЃЌЫљгаЕФФкДцЖМЛсБЛетРяЕФБэЕЅКФОЁЃЌЫљвдетвЛЕувВВЛКЯРэЁЃ

ЕквЛВНЃК**ВЛвЊЮЊУПИіЕижЗДДНЈвЛЬѕБэЕЅЬѕФПЃЌЖјЪЧЮЊУПИіpageДДНЈвЛЬѕБэЕЅЬѕФПЃЌЫљвдУПвЛДЮЕижЗЗвыЖМЪЧеыЖдвЛИіpageЁЃ**ЖјRISC-VжаЃЌвЛИіpageЪЧ4KBЃЌвВОЭЪЧ4096BytesЁЃетИіДѓаЁЗЧГЃГЃМћЃЌМИКѕЫљгаЕФДІРэЦїЖМЪЙгУ4KBДѓаЁЕФpageЛђепжЇГж4KBДѓаЁЕФpageЁЃ

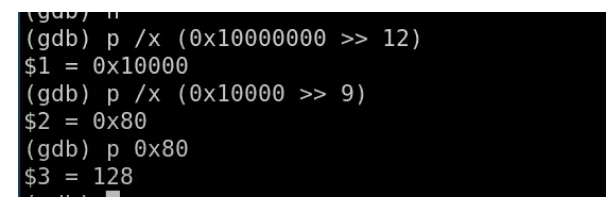

етбљОЭЫѕаЁСЫ 2^12ЃЌдЪаэДДНЈ2^27ИізЊЛЛБэЕЅЬѕФПЃЌЭЈЙ§ащФтФкДцздДјЕФЕЭ12ЮЛ

гаЙиRISC-VЕФвЛМўгавтЫМЕФЪТЧщЪЧЃЌащФтФкДцЕижЗЖМЪЧ64bitЃЌетвВЫЕЕФЭЈЃЌвђЮЊRISC-VЕФМФДцЦїЪЧ64bitЕФЁЃЕЋЪЧЪЕМЪЩЯЃЌдкЮвУЧЪЙгУЕФRSIC-VДІРэЦїЩЯЃЌВЂВЛЪЧЫљгаЕФ64bitЖМБЛЪЙгУСЫЃЌвВОЭЪЧЫЕИп25bitВЂУЛгаБЛЪЙгУЁЃетбљЕФНсЙћЪЧЯожЦСЫащФтФкДцЕижЗЕФЪ§СПЃЌащФтФкДцЕижЗЕФЪ§СПЯждкжЛга2^39ИіЃЌДѓИХЪЧ512GBЁЃЕБШЛЃЌШчЙћБивЊЕФЛАЃЌзюаТЕФДІРэЦїЛђаэПЩвджЇГжИќДѓЕФЕижЗПеМфЃЌжЛашвЊНЋЮДЪЙгУЕФ25bitФУГіРДзіЮЊащФтФкДцЕижЗЕФвЛВПЗжМДПЩЁЃ

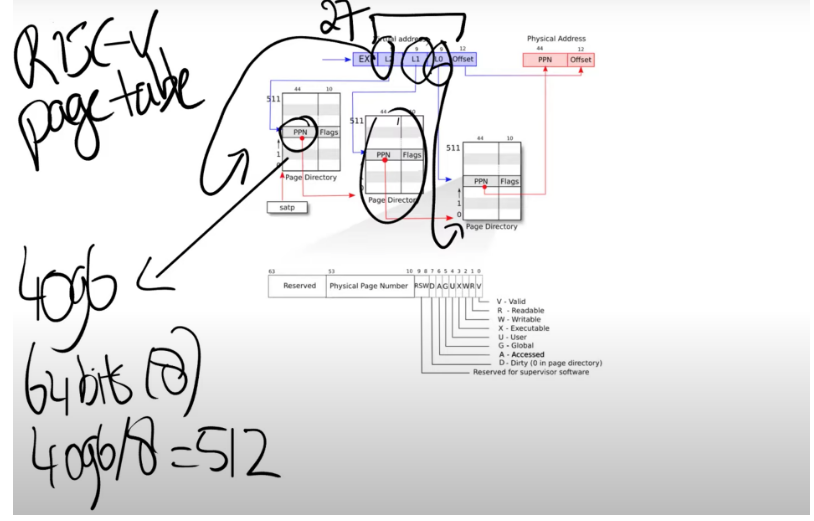

дкЪЃЯТЕФ39bitжаЃЌга27bitБЛгУРДЕБзіindexЃЌ12bitБЛгУРДЕБзіoffsetЁЃoffsetБиаыЪЧ12bitЃЌвђЮЊЖдгІСЫвЛИіpageЕФ4096ИізжНкЁЃ

дкRISC-VжаЃЌЮяРэФкДцЕижЗЪЧ56bitЁЃЫљвдЮяРэФкДцПЩвдДѓгкЕЅИіащФтФкДцЕижЗПеМфЃЌЕЋЪЧвВзюЖрЕН2^56ЁЃДѓЖрЪ§жїАхЛЙВЛжЇГж2^56етУДДѓЕФЮяРэФкДцЃЌЕЋЪЧддђЩЯЃЌШчЙћФуФмдьГіетбљЕФжїАхЃЌФЧУДзюЖрПЩвджЇГж2^56зжНкЕФЮяРэФкДцЁЃ

ЕижЗзЊЛЛБэЪЧвдpageЮЊСЃЖШ(ВЛЪЧЕижЗ)

ТдЮЂЕФВЛЭЌСЫЁЃЪзЯШЖдгкащФтФкДцЕижЗЃЌЮвУЧНЋЫќЛЎЗжЮЊСНИіВПЗжЃЌindexКЭoffsetЃЌindexгУРДВщевpageЃЌoffsetЖдгІЕФЪЧвЛИіpageжаЕФФФИізжНкЁЃ

-

ЕБMMUдкзіЕижЗЗвыЕФЪБКђЃЌЭЈЙ§ЖСШЁащФтФкДцЕижЗжаЕФindexПЩвджЊЕРЮяРэФкДцжаЕФpageКХЃЌетИіpageКХЖдгІСЫЮяРэФкДцжаЕФ4096ИізжНкЁЃжЎКѓащФтФкДцЕижЗжаЕФoffsetжИЯђСЫpageжаЕФ4096ИізжНкжаЕФФГвЛИіЃЌМйЩшoffsetЪЧ12ЃЌФЧУДpageжаЕФЕк12ИізжНкБЛЪЙгУСЫЁЃНЋoffsetМгЩЯpageЕФЦ№ЪМЕижЗЃЌОЭПЩвдЕУЕНЮяРэФкДцЕижЗЁЃ

-

ЮяРэФкДцЕижЗЪЧ56bitЃЌЦфжа44bitЪЧЮяРэpageКХЃЈPPNЃЌPhysical Page NumberЃЉЃЌЪЃЯТ12bitЪЧoffsetЭъШЋМЬГаздащФтФкДцЕижЗЃЈвВОЭЪЧЕижЗзЊЛЛЪБЃЌжЛашвЊНЋащФтФкДцжаЕФ27bitЗвыГЩЮяРэФкДцжаЕФ44bitЕФpageКХЃЌЪЃЯТЕФ12bitoffsetжБНгПНБДЙ§РДМДПЩЃЉЁЃ

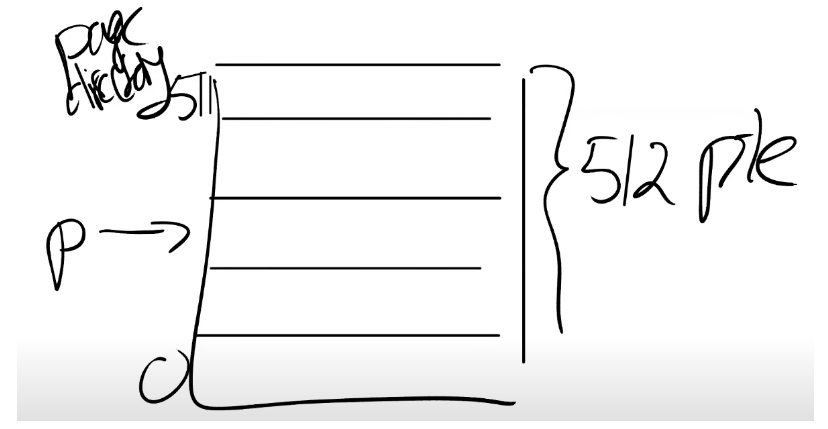

page tableЪЧвЛИіЖрМЖЕФНсЙЙ(НкЪЁПеМф)

-

ЮвУЧжЎЧАЬсЕНЕФащФтФкДцЕижЗжаЕФ27bitЕФindexЃЌЪЕМЪЩЯЪЧгЩ3Иі9bitЕФЪ§зжзщГЩЃЈL2ЃЌL1ЃЌL0ЃЉЁЃ

ЧА9ИіbitБЛгУРДЫїв§зюИпМЖЕФpage directoryЃЈзЂЃКЭЈГЃpage directoryЪЧгУРДЫїв§page tableЛђепЦфЫћpage directoryЮяРэЕижЗЕФБэЕЅЃЌЕЋЪЧдкПЮГЬжаЃЌpage tableЃЌpage directoryЃЌ page directory tableЧјЗжВЂВЛУїЯдЃЌПЩвдЖМШЯЮЊЪЧгаЯрЭЌНсЙЙЕФЕижЗЖдгІБэЕЅЃЉЁЃ -

вЛИіdirectoryЪЧ4096BytesЃЌОЭИњpageЕФДѓаЁЪЧвЛбљЕФЁЃDirectoryжаЕФвЛИіЬѕФПБЛГЦЮЊPTEЃЈPage Table EntryЃЉЪЧ64bitsЃЌОЭЯёМФДцЦїЕФДѓаЁвЛбљЃЌвВОЭЪЧ8BytesЁЃЫљвдвЛИіDirectory pageга512ИіЬѕФПЁЃ

зЂЃК 2^9ЃЈЫїв§ДѓаЁЃЉ * 8 BytesЃЈМФДцЦїДѓаЁЃЉ = 4096 BytesЃЈвГДѓаЁЃЉ

-

ЫљвдЪЕМЪЩЯЃЌSATPМФДцЦїЛсжИЯђзюИпвЛМЖЕФpage directoryЕФЮяРэФкДцЕижЗЃЌжЎКѓЮвУЧгУ**ащФтФкДцжаindexЕФИп9bitгУРДЫїв§зюИпвЛМЖЕФpage directoryЃЌетбљЮвУЧОЭФмЕУЕНвЛИіPPNЃЌвВОЭЪЧЮяРэpageКХЁЃ**етИіPPNжИЯђСЫжаМфМЖЕФpage directoryЁЃ

-

ЕБЮвУЧдкЪЙгУжаМфМЖЕФpage directoryЪБЃЌЮвУЧЭЈЙ§ащФтФкДцЕижЗжаЕФL1ВПЗжЭъГЩЫїв§ЁЃНгЯТРДЛсзпЕНзюЕЭМЖЕФpage directoryЃЌЮвУЧЭЈЙ§ащФтФкДцЕижЗжаЕФL0ВПЗжЭъГЩЫїв§ЁЃдкзюЕЭМЖЕФpage directoryжаЃЌЮвУЧПЩвдЕУЕНЖдгІгкащФтФкДцЕижЗЕФЮяРэФкДцЕижЗЁЃ

-

ДгФГжжГЬЖШЩЯРДЫЕЃЌгыжЎЧАвЛжжЗНАИЛЙЪЧКмЯрЫЦЕФЃЌГ§СЫЪЕМЪЕФЫїв§ЪЧгЩ3ВНЃЌЖјВЛЪЧ1ВНЭъГЩЁЃ**етжжЗНЪНЕФжївЊгХЕуЪЧЃЌШчЙћЕижЗПеМфжаДѓВПЗжЕижЗЖМУЛгаЪЙгУЃЌФуВЛБиЮЊУПвЛИіindexзМБИвЛИіЬѕФПЁЃ**ОйИіР§згЃЌШчЙћФуЕФЕижЗПеМфжЛЪЙгУСЫвЛИіpageЃЌ4096BytesЁЃ

-

Г§ДЫжЎЭтЃЌФуУЛгаЪЙгУШЮКЮЦфЫћЕФЕижЗЁЃЯждкЃЌФуашвЊЖрЩйИіpage table entryЃЌЛђепpage table directoryРДгГЩфетвЛИіpageЃП

-

дкзюИпМЖЃЌФуашвЊвЛИіpage directoryЁЃдкетИіpage directoryжаЃЌФуашвЊвЛИіЪ§зжЪЧ0ЕФPTEЃЌжИЯђжаМфМЖpage directoryЁЃЫљвддкжаМфМЖЃЌФувВашвЊвЛИіpage directoryЃЌРяУцвВЪЧвЛИіЪ§зж0ЕФPTEЃЌжИЯђзюЕЭМЖpage directoryЁЃЫљвдетРязмЙВашвЊ3Иіpage directoryЃЈвВОЭЪЧ3 * 512ИіЬѕФПЃЉЁЃ

-

**ЖјдкЧАвЛИіЗНАИжаЃЌЫфШЛЮвУЧжЛЪЙгУСЫвЛИіpageЃЌЛЙЪЧашвЊ2^27ИіPTEЁЃетИіЗНАИжаЃЌЮвУЧжЛашвЊ3 * 512ИіPTEЁЃЫљашЕФПеМфДѓДѓМѕЩйСЫЁЃетЪЧЪЕМЪЩЯгВМўВЩгУетжжВуДЮЛЏЕФ3МЖpage directoryНсЙЙЕФжївЊдвђЁЃ**етРягаЪВУДЮЪЬтТ№ЃПетВПЗжЛЙЪЧКмживЊЕФЁЃ

ЫљгаЕФpage directoryДЋЕнЕФЖМЪЧPPN(ЮяРэpageКХ)ЃЌЖдгІЕФЮяРэЕижЗЪЧ44bitЕФPPNМгЩЯ12bitЕФ0ЃЈзЂЃЌвВОЭЪЧpageЕФЦ№ЪМЕижЗЃЌвђЮЊУПИіpage directoryЖМЪЙгУвЛИіЭъећЕФpageЃЌЫљвджБНгДгpageЦ№ЪМЕижЗПЊЪМЪЙгУОЭааЃЉЁЃШчЙћЮвУЧВщПДетРяЕФPTEЬѕФПЃЌЫќУЧЖМгаЯрЭЌЕФИёЪНЃЌЦфжа44bitЪЧPPNЃЌЕЋЪЧМФДцЦїЪЧ64bitЕФЃЌЫљгагавЛаЉbitЪЧСєПеЕФЁЃЪЕМЪЩЯЃЌжЇГжpageЕФгВМўдкЕЭ10bitДцСЫвЛаЉБъжОЮЛгУРДПижЦЕижЗШЈЯоЁЃ

ШчЙћФуАб44bitЕФPPNКЭ10bitЕФFlagsЯрМгЪЧ54bitЃЌвВОЭЪЧЫЕЛЙга10bitЮДБЛЪЙгУЃЌет10bitБЛгУРДзїЮЊЮДРДРЉеЙЁЃБШШчЫЕФГвЛЬьФугаСЫвЛИіаТЕФRISC-VДІРэЦїЃЌЫќЕФpage tableПЩФмТдгаВЛЭЌЃЌЛђаэгаГЌЙ§44bitЕФPPNЁЃШчЙћФуПДЯТУцетеХЭМЃЌФуПЩвдПДЕНЃЌетРяга10bitЪЧзїЮЊБЃСєзжЖЮДцдкЕФЁЃ

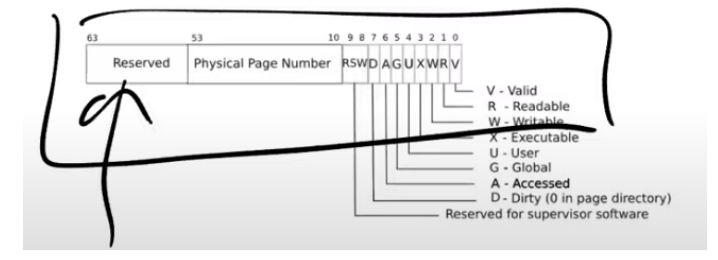

PTEжаЕФflag

НгЯТРДЃЌШУЮвУЧПДПДPTEжаЕФFlagЃЌвђЮЊЫќвВКмживЊЁЃУПИіPTEЕФЕЭ10bitЪЧвЛЖбБъжОЮЛЃК

- ЕквЛИіБъжОЮЛЪЧValidЁЃШчЙћValid bitЮЛЮЊ1ЃЌФЧУДБэУїетЪЧвЛЬѕКЯЗЈЕФPTEЃЌФуПЩвдгУЫќРДзіЕижЗЗвыЁЃЖдгкИеИеОйЕУФЧИіаЁР§згЃЈгІгУГЬађжЛгУСЫ1ИіpageЕФР§згЃЉЃЌЮвУЧжЛЪЙгУСЫ3Иіpage directoryЃЌУПИіpage directoryжажЛгаЕк0ИіPTEБЛЪЙгУСЫЃЌЫљвджЛгаЕк0ИіPTEЕФValid bitЮЛЛсБЛЩшжУГЩ1ЃЌЦфЫћЕФ511ИіPTEЕФValid bitЮЊ0ЁЃетИіБъжОЮЛИцЫпMMUЃЌФуВЛФмЪЙгУетЬѕPTEЃЌвђЮЊетЬѕPTEВЂВЛАќКЌгагУЕФаХЯЂЁЃ

- ЯТСНИіБъжОЮЛЗжБ№ЪЧReadableКЭWritableЁЃБэУїФуЪЧЗёПЩвдЖС/аДетИіpageЁЃ

- ExecutableБэУїФуПЩвдДгетИіpageжДаажИСюЁЃ

- UserБэУїетИіpageПЩвдБЛдЫаадкгУЛЇПеМфЕФНјГЬЗУЮЪЁЃ

- ЦфЫћБъжОЮЛВЂВЛЪЧФЧУДживЊЃЌЫћУЧХМЖћЛсГіЯжЃЌЧАУц5ИіЪЧживЊЕФБъжОЮЛ

вГБэЛКДцЃЈTranslation Lookaside BufferЃЉ

ЕБДІРэЦїДгФкДцМгдиЛђепДцДЂЪ§ОнЪБЃЌЛљБОЩЯЖМвЊзі3ДЮФкДцВщевЃЌЕквЛДЮдкзюИпМЖЕФpage directoryЃЌЕкЖўДЮдкжаМфМЖЕФpage directoryЃЌзюКѓвЛДЮдкзюЕЭМЖЕФpage directoryЁЃЫљвдЖдгквЛИіащФтФкДцЕижЗЕФбАжЗЃЌашвЊЖСШ§ДЮФкДцЃЌетРяДњМлгаЕуИп**ЁЃЫљвдЪЕМЪжаЃЌМИКѕЫљгаЕФДІРэЦїЖМЛсЖдгкзюНќЪЙгУЙ§ЕФащФтЕижЗЕФЗвыНсЙћгаЛКДцЁЃетИіЛКДцБЛГЦЮЊЃКTranslation Lookside BufferЃЈЭЈГЃЗвыГЩвГБэЛКДцЃЉЁЃ**ФуЛсОГЃПДЕНЫќЕФЫѕаДTLBЁЃЛљБОЩЯРДЫЕЃЌетОЭЪЧPage Table EntryЕФЛКДцЃЌвВОЭЪЧPTEЕФЛКДцЁЃ

ЕБДІРэЦїЕквЛДЮВщеввЛИіащФтЕижЗЪБЃЌгВМўЭЈЙ§3МЖpage tableЕУЕНзюжеЕФPPNЃЌTLBЛсБЃДцащФтЕижЗЕНЮяРэЕижЗЕФгГЩфЙиЯЕЁЃетбљЯТвЛДЮЕБФуЗУЮЪЭЌвЛИіащФтЕижЗЪБЃЌДІРэЦїПЩвдВщПДTLBЃЌTLBЛсжБНгЗЕЛиЮяРэЕижЗЃЌЖјВЛашвЊЭЈЙ§page tableЕУЕННсЙћЁЃ

жЇГжащФтФкДцЕФгВМў

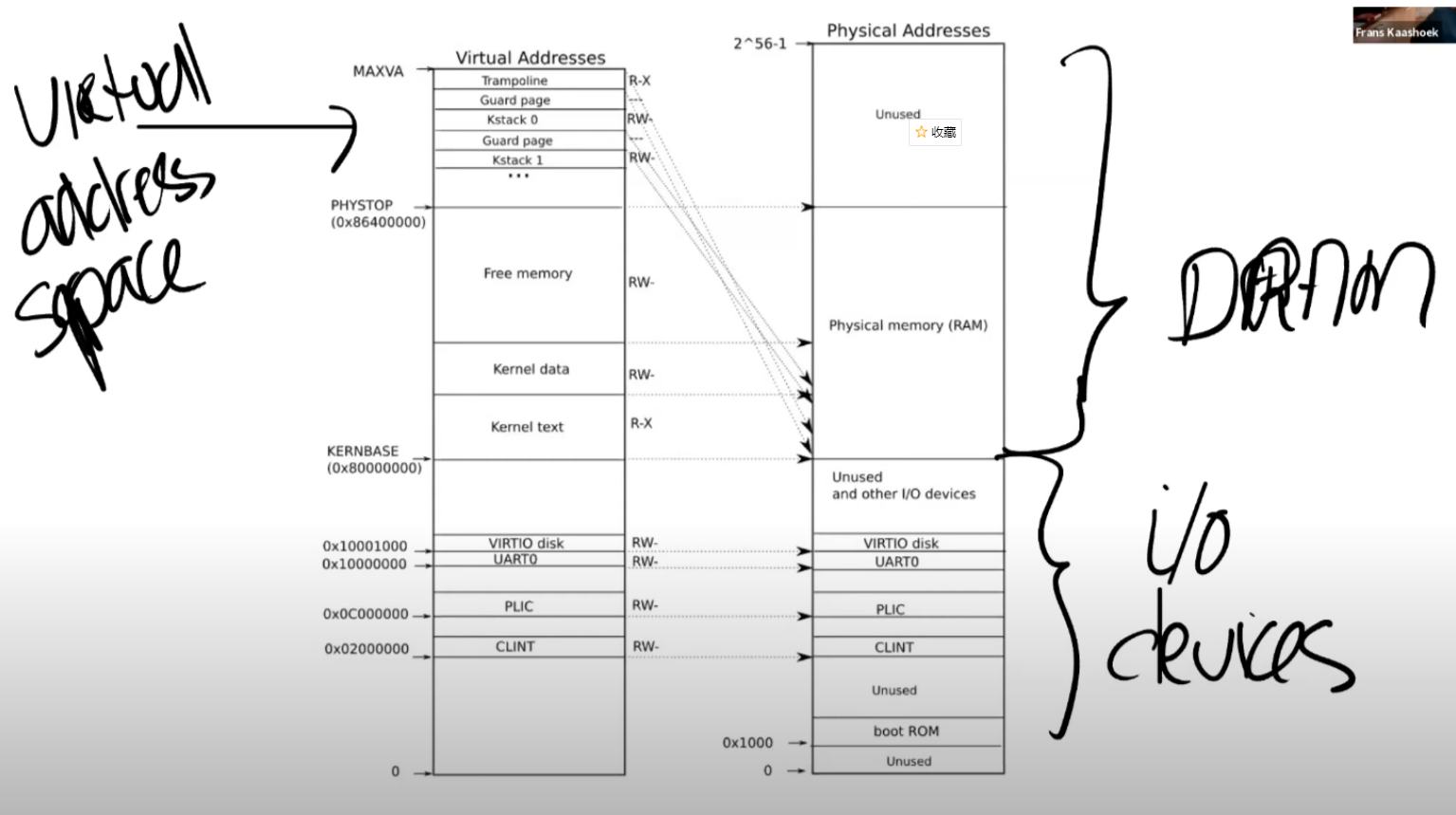

Kernel Page Table

вдЯТФкШнДПЃЈИДЪіЃЉ

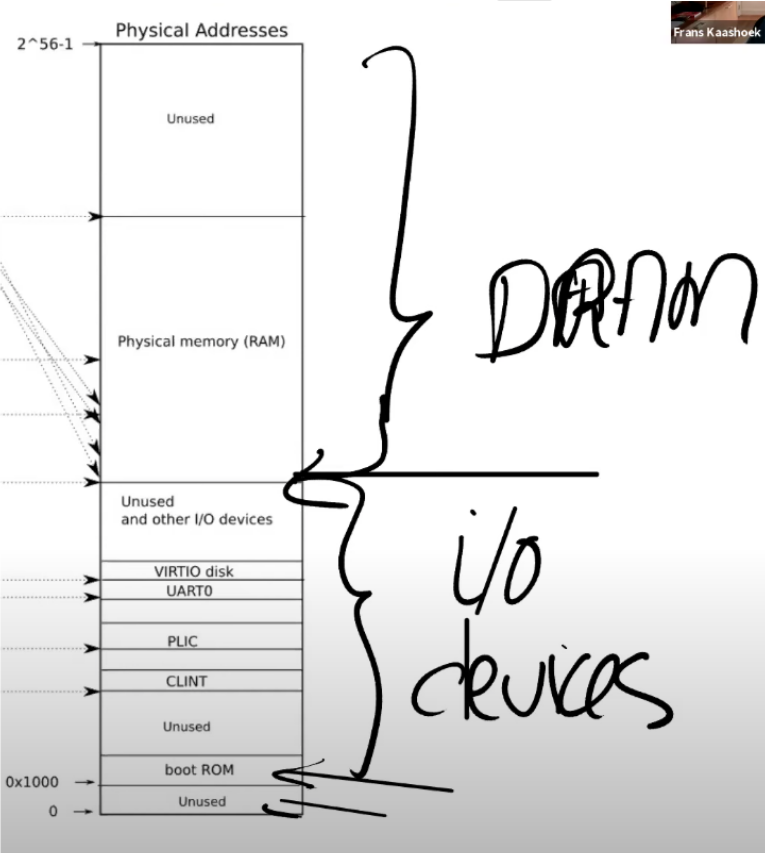

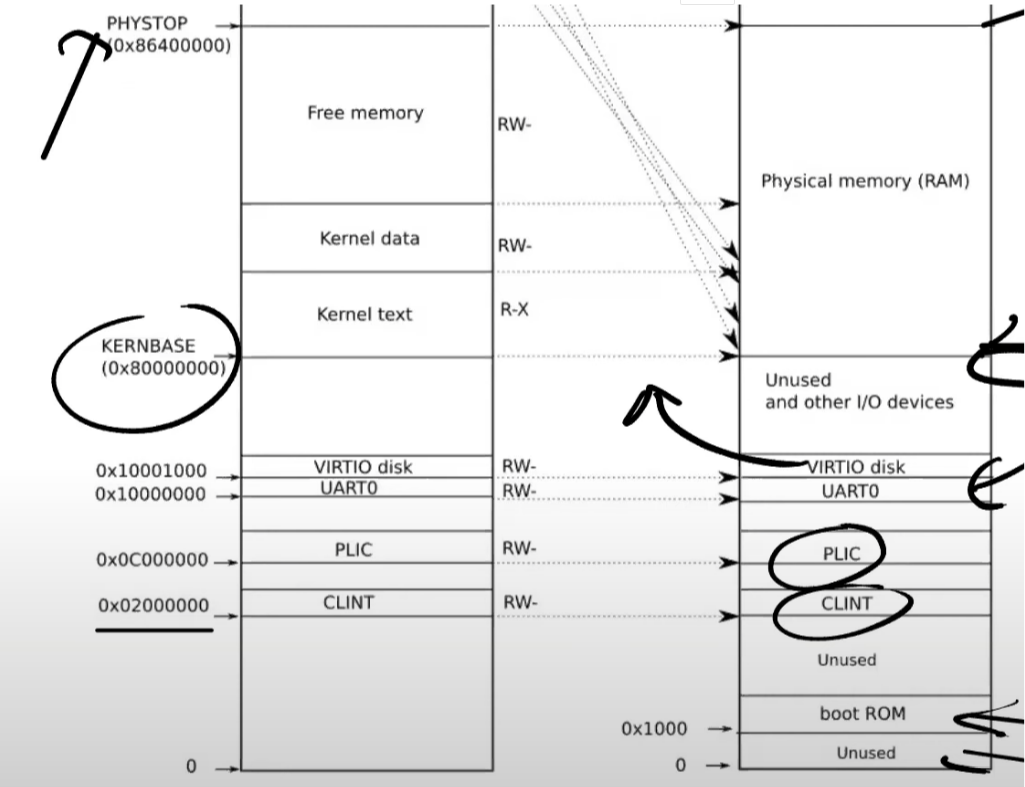

НгЯТРДЃЌЮвУЧПДвЛЯТдкXV6жаЃЌpage tableЪЧШчКЮЙЄзїЕФЃПЪзЯШЮвУЧРДПДвЛЯТkernel pageЕФЗжВМЁЃЯТЭМОЭЪЧФкКЫжаЕижЗЕФЖдгІЙиЯЕЃЌзѓБпЪЧФкКЫЕФащФтЕижЗПеМфЃЌгвБпЩЯАыВПЗжЪЧЮяРэФкДцЛђепЫЕЪЧDRAMЃЌгвБпЯТАыВПЗжЪЧI/OЩшБИЁЃНгЯТРДЮвЛсЪзЯШНщЩмгвАыВПЗжЃЌШЛКѓдйНщЩмзѓАыВПЗжЁЃ

ЭМжаЕФгвАыВПЗжЕФНсЙЙЭъШЋгЩгВМўЩшМЦепОіЖЈЁЃШчФуУЧЩЯНкПЮПДЕНЕФвЛбљЃЌЕБВйзїЯЕЭГЦєЖЏЪБЃЌЛсДгЕижЗ0x80000000ПЊЪМдЫааЃЌетИіЕижЗЦфЪЕвВЪЧгЩгВМўЩшМЦепОіЖЈЕФЁЃОпЬхЕФРДЫЕЃЌШчЙћФуУЧПДвЛИіжїАхЃЌ

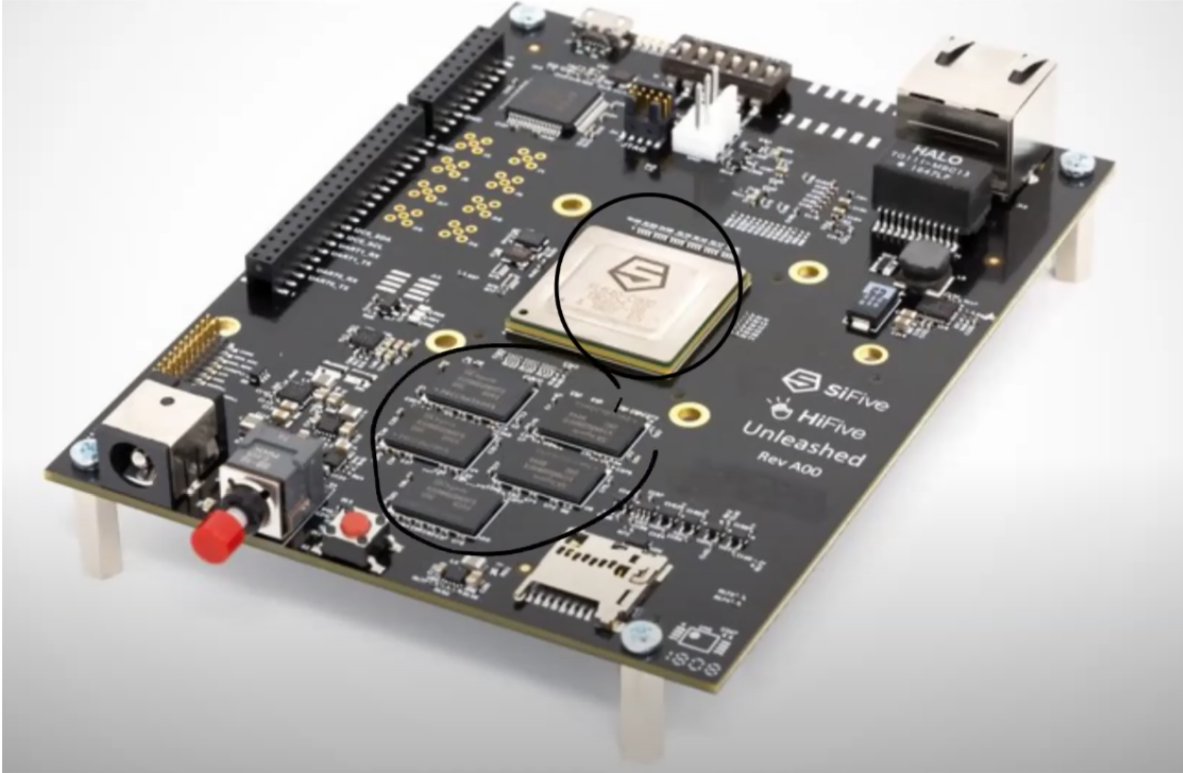

жаМфЪЧRISC-VДІРэЦїЃЌЮвУЧЯждкжЊЕРСЫДІРэЦїжага4ИіКЫЃЌУПИіКЫЖМгаздМКЕФMMUКЭTLBЁЃДІРэЦїХдБпОЭЪЧDRAMаОЦЌЁЃ

**жїАхЕФЩшМЦШЫдБОіЖЈСЫЃЌдкЭъГЩСЫащФтЕНЮяРэЕижЗЕФЗвыжЎКѓЃЌШчЙћЕУЕНЕФЮяРэЕижЗДѓгк0x80000000ЛсзпЯђDRAMаОЦЌЃЌШчЙћЕУЕНЕФЮяРэЕижЗЕЭгк0x80000000ЛсзпЯђВЛЭЌЕФI/OЩшБИЁЃ**етЪЧгЩетИіжїАхЕФЩшМЦШЫдБОіЖЈЕФЮяРэНсЙЙЁЃШчЙћФуЯывЊВщПДетРяЕФЮяРэНсЙЙЃЌФуПЩвддФЖСжїАхЕФЪжВсЃЌЪжВсжаЛсвЛвЛНщЩмЮяРэЕижЗЖдгІЙиЯЕЁЃ

ЪзЯШЃЌЕижЗ0ЪЧБЃСєЕФЃЌ**ЕижЗ0x10090000ЖдгІвдЬЋЭјЃЌЕижЗ0x80000000ЖдгІDDRФкДцЃЌДІРэЦїЭтЕФвзЪЇДцДЂЃЈOff-Chip Volatile MemoryЃЉЃЌвВОЭЪЧжїАхЩЯЕФDRAMаОЦЌЁЃ**ЫљвдЃЌдкФуУЧЕФФдКЃРягІИУвЊМЧзЁетеХжїАхЕФЭМЦЌЃЌМДЪЙЮвУЧНгЯТРДЛсЛљгкФуУЧЖМжЊЕРЕФCгябдГЬађЁЊQEMUРДзіНщЩмЃЌЕЋЪЧзюжеЫљгаЕФЪТЧщЖМЪЧгЩжїАхгВМўОіЖЈЕФЁЃ

бЇЩњЬсЮЪЃКЕБФуЫЕетРяЪЧгЩгВМўОіЖЈЕФЃЌгВМўЪЧЬижИCPUЛЙЪЧЫЕCPUЫљдкЕФжїАхЃП

FransНЬЪкЃКCPUЫљдкЕФжїАхЁЃCPUжЛЪЧжїАхЕФвЛаЁВПЗжЃЌDRAMаОЦЌЮЛгкДІРэЦїжЎЭтЁЃЪЧжїАхЩшМЦепНЋДІРэЦїЃЌDRAMКЭаэЖрI/OЩшБИЛузмдквЛЦ№ЁЃЖдгквЛИіВйзїЯЕЭГРДЫЕЃЌCPUжЛЪЧвЛИіВПЗжЃЌI/OЩшБИЭЌбљвВКмживЊЁЃЫљвдЕБФудкаДвЛИіВйзїЯЕЭГЪБЃЌФуашвЊЭЌЪБДІРэCPUКЭI/OЩшБИЃЌБШШчФуашвЊЯђЛЅСЊЭјЗЂЫЭвЛИіБЈЮФЃЌВйзїЯЕЭГашвЊЕїгУЭјПЈЧ§ЖЏКЭЭјПЈРДЪЕМЪЭъГЩетИіЙЄзїЁЃ

ЛиЕНзюГѕФЧеХЭМЕФгвВрЃКЮяРэЕижЗЕФЗжВМЁЃПЩвдПДЕНзюЯТУцЪЧЮДБЛЪЙгУЕФЕижЗЃЌетгыжїАхЮФЕЕФкШнЪЧвЛжТЕФЃЈЕижЗЮЊ0ЃЉЁЃЕижЗ0x1000ЪЧboot ROMЕФЮяРэЕижЗЃЌЕБФуЖджїАхЩЯЕчЃЌжїАхзіЕФЕквЛМўЪТЧщОЭЪЧдЫааДцДЂдкboot ROMжаЕФДњТыЃЌЕБbootЭъГЩжЎКѓЃЌЛсЬјзЊЕНЕижЗ0x80000000ЃЌВйзїЯЕЭГашвЊШЗБЃФЧИіЕижЗгавЛаЉЪ§ОнФмЙЛНгзХЦєЖЏВйзїЯЕЭГЁЃ

етРяЛЙгавЛаЉЦфЫћЕФI/OЩшБИЃК

- PLICЪЧжаЖЯПижЦЦїЃЈPlatform-Level Interrupt ControllerЃЉЮвУЧЯТжмЕФПЮЛсНВЁЃ

- CLINTЃЈCore Local InterruptorЃЉвВЪЧжаЖЯЕФвЛВПЗжЁЃЫљвдЖрИіЩшБИЖМФмВњЩњжаЖЯЃЌашвЊжаЖЯПижЦЦїРДНЋетаЉжаЖЯТЗгЩЕНКЯЪЪЕФДІРэКЏЪ§ЁЃ

- UART0ЃЈUniversal Asynchronous Receiver/TransmitterЃЉИКд№гыConsoleКЭЯдЪОЦїНЛЛЅЁЃ

- VIRTIO diskЃЌгыДХХЬНјааНЛЛЅЁЃ

**ЕижЗ0x02000000ЖдгІCLINTЃЌЕБФуЯђетИіЕижЗжДааЖСаДжИСюЃЌФуЪЧЯђЪЕЯжСЫCLINTЕФаОЦЌжДааЖСаДЁЃ**етРяФуПЩвдШЯЮЊФужБНгдкгыЩшБИНЛЛЅЃЌЖјВЛЪЧЖСаДЮяРэФкДцЁЃ

бЇЩњЬсЮЪЃКШЗШЯвЛЯТЃЌЕЭгк0x80000000ЕФЮяРэЕижЗЃЌВЛДцдкгкDRAMжаЃЌЕБЮвУЧдкЪЙгУетаЉЕижЗЕФЪБКђЃЌжИСюЛсжБНгзпЯђЦфЫћЕФгВМўЃЌЖдТ№ЃП

FransНЬЪкЃКЪЧЕФЁЃИпгк0x80000000ЕФЮяРэЕижЗЖдгІDRAMаОЦЌЃЌЕЋЪЧЖдгкР§ШчвдЬЋЭјНгПкЃЌвВгавЛИіЬиЖЈЕФЕЭгк0x80000000ЕФЮяРэЕижЗЃЌЮвУЧПЩвдЖдетИіНазіФкДцгГЩфI/OЃЈMemory-mapped I/OЃЉЕФЕижЗжДааЖСаДжИСюЃЌРДЭъГЩЩшБИЕФВйзїЁЃ

бЇЩњЬсЮЪЃКЮЊЪВУДЮяРэЕижЗзюЩЯУцвЛДѓПщБъЮЊЮДБЛЪЙгУЃП

FransНЬЪкЃКЮяРэЕижЗзмЙВга2^56ФЧУДЖрЃЌЕЋЪЧФуВЛгУдкжїАхЩЯНгШыФЧУДЖрЕФФкДцЁЃЫљвдВЛТлжїАхЩЯгаЖрЩйDRAMаОЦЌЃЌзмЪЧЛсгавЛВПЗжЮяРэЕижЗУЛгаБЛгУЕНЁЃЪЕМЪЩЯдкXV6жаЃЌЮвУЧЯожЦСЫФкДцЕФДѓаЁЪЧ128MBЁЃ

бЇЩњЬсЮЪЃКЕБЖСжИСюДгCPUЗЂГіКѓЃЌЫќЪЧдѕУДТЗгЩЕНе§ШЗЕФI/OЩшБИЕФЃПБШШчЫЕЃЌЕБCPUвЊЗЂГіжИСюЪБЃЌЫќПЩвдЗЂЯжЯждкЕижЗЪЧЕЭгк0x80000000ЃЌЕЋЪЧЫќдѕУДНЋжИСюЫЭЕНе§ШЗЕФI/OЩшБИЃП

FransНЬЪкЃКФуПЩвдШЯЮЊдкRISC-VжагавЛИіЖрТЗЪфГібЁдёЦїЃЈdemultiplexerЃЉЁЃ

НгЯТРДЮвЛсЧаЛЛЕНЕквЛеХЭМЕФзѓБпЃЌетОЭЪЧXV6ЕФащФтФкДцЕижЗПеМфЁЃЕБЛњЦїИеИеЦєЖЏЪБЃЌЛЙУЛгаПЩгУЕФpageЃЌXV6ВйзїЯЕЭГЛсЩшжУКУФкКЫЪЙгУЕФащФтЕижЗПеМфЃЌвВОЭЪЧетеХЭМзѓБпЕФЕижЗЗжВМЁЃ

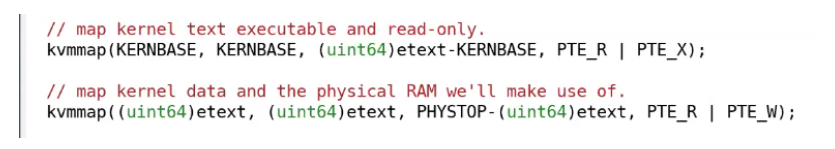

вђЮЊЮвУЧЯыШУXV6ОЁПЩФмЕФМђЕЅвзЖЎЃЌЫљвдетРяЕФащФтЕижЗЕНЮяРэЕижЗЕФгГЩфЃЌДѓВПЗжЪЧЯрЕШЕФЙиЯЕЁЃБШШчЫЕФкКЫЛсАДееетжжЗНЪНЩшжУpage tableЃЌащФтЕижЗ0x02000000ЖдгІЮяРэЕижЗ0x02000000ЁЃетвтЮЖзХзѓВрЕЭгкPHYSTOPЕФащФтЕижЗЃЌгыгвВрЪЙгУЕФЮяРэЕижЗЪЧвЛбљЕФЁЃ

ЫљвдЃЌетРяЕФМ§ЭЗЖМЪЧЫЎЦНЕФЃЌвђЮЊетРяЪЧЭъШЋЯрЕШЕФгГЩфЁЃ

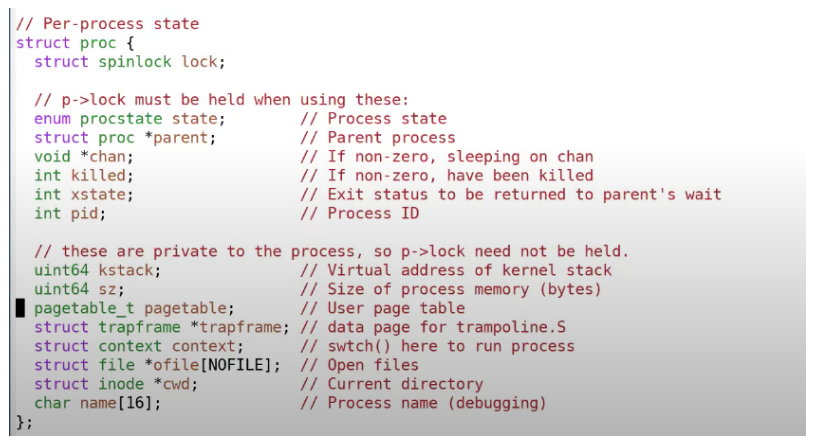

kernel stack КЭ ШЈЯо

Г§ДЫжЎЭтЃЌетРяЛЙгаСНМўживЊЕФЪТЧщЃК

ЕквЛМўЪТЧщЪЧЃЌгавЛаЉpageдкащФтФкДцжаЕФЕижЗКмППКѓЃЌ==БШШчkernel stackдкащФтФкДцжаЕФЕижЗОЭКмППКѓЁЃетЪЧвђЮЊдкЫќжЎЯТгавЛИіЮДБЛгГЩфЕФGuard pageЃЌетИіGuard pageЖдгІЕФPTEЕФValid БъжОЮЛУЛгаЩшжУЃЌетбљЃЌШчЙћkernel stackКФОЁСЫЃЌЫќЛсвчГіЕНGuard pageЃЌЕЋЪЧвђЮЊGuard pageЕФPTEжаValidБъжОЮЛЮДЩшжУЃЌЛсЕМжТСЂМДДЅЗЂpage faultЃЌетбљЕФНсЙћКУЙ§ФкДцдННчжЎКѓдьГЩЕФЪ§ОнЛьТвЁЃ==СЂМДДЅЗЂвЛИіpanicЃЈвВОЭЪЧpage faultЃЉЃЌФуОЭжЊЕРkernel stackГіДэСЫЁЃЭЌЪБЮвУЧвВгжВЛЯыРЫЗбЮяРэФкДцИјGuard pageЃЌЫљвдGuard pageВЛЛсгГЩфЕНШЮКЮЮяРэФкДцЃЌЫќжЛЪЧеМОнСЫащФтЕижЗПеМфЕФвЛЖЮППКѓЕФЕижЗЁЃ

ЭЌЪБЃЌkernel stackБЛгГЩфСЫСНДЮЃЌдкППКѓЕФащФтЕижЗгГЩфСЫвЛДЮЃЌдкPHYSTOPЯТЕФKernel dataжагжгГЩфСЫвЛДЮЃЌЕЋЪЧЪЕМЪЪЙгУЕФЪБКђгУЕФЪЧЩЯУцЕФВПЗжЃЌвђЮЊгаGuard pageЛсИќМгАВШЋЁЃ

етЪЧжкЖрФуПЩвдЭЈЙ§page tableЪЕЯжЕФгавтЫМЕФЪТЧщжЎвЛЁЃ**ФуПЩвдЯђЭЌвЛИіЮяРэЕижЗгГЩфСНИіащФтЕижЗЃЌФуПЩвдВЛНЋвЛИіащФтЕижЗгГЩфЕНЮяРэЕижЗЁЃПЩвдЪЧвЛЖдвЛЕФгГЩфЃЌвЛЖдЖргГЩфЃЌЖрЖдвЛгГЩфЁЃXV6жСЩйдк1-2ИіЕиЗНгУЕНРрЫЦЕФММЧЩЁЃ**етЕФkernel stackКЭGuard pageОЭЪЧXV6Лљгкpage tableЪЙгУЕФгаШЄММЧЩЕФвЛИіР§згЁЃ

ЕкЖўМўЪТЧщЪЧШЈЯоЁЃР§ШчKernel text pageБЛБъЮЛR-XЃЌвтЮЖзХФуПЩвдЖСЫќЃЌвВПЩвддкетИіЕижЗЖЮжДаажИСюЃЌЕЋЪЧФуВЛФмЯђKernel textаДЪ§ОнЁЃЭЈЙ§ЩшжУШЈЯоЮвУЧПЩвдОЁдчЕФЗЂЯжBugДгЖјБмУтBugЁЃЖдгкKernel dataашвЊФмБЛаДШыЃЌЫљвдЫќЕФБъжОЮЛЪЧRW-ЃЌЕЋЪЧФуВЛФмдкетИіЕижЗЖЮдЫаажИСюЃЌЫљвдЫќЕФXБъжОЮЛЮДБЛЩшжУЁЃЃЈзЂЃЌЫљвдЃЌkernel textгУРДДцДњТыЃЌДњТыПЩвдЖСЃЌПЩвддЫааЃЌЕЋЪЧВЛФмДлИФЃЌkernel dataгУРДДцЪ§ОнЃЌЪ§ОнПЩвдЖСаДЃЌЕЋЪЧВЛФмЭЈЙ§Ъ§ОнЮБзАДњТыдкkernelжадЫааЃЉ

бЇЩњЬсЮЪЃКЖдгкВЛЭЌЕФНјГЬЛсгаВЛЭЌЕФkernel stackТ№ЃП

FransЃКД№АИЪЧЕФЁЃУПвЛИігУЛЇНјГЬЖМгавЛИіЖдгІЕФkernel stack

бЇЩњЬсЮЪЃКгУЛЇГЬађЕФащФтФкДцЛсгГЩфЕНЮДЪЙгУЕФЮяРэЕижЗПеМфТ№ЃП

FransНЬЪкЃКдкkernel page tableжаЃЌгавЛЖЮFree MemoryЃЌЫќЖдгІСЫЮяРэФкДцжаЕФвЛЖЮЕижЗЁЃ

XV6ЪЙгУетЖЮfree memoryРДДцЗХгУЛЇНјГЬЕФpage tableЃЌtextКЭdataЁЃШчЙћЮвУЧдЫааСЫЗЧГЃЖрЕФгУЛЇНјГЬЃЌФГИіЪБМфЕуЮвУЧЛсКФОЁетЖЮФкДцЃЌетИіЪБКђforkЛђепexecЛсЗЕЛиДэЮѓЁЃ

ЭЌвЛИібЇЩњЬсЮЪЃКетОЭвтЮЖзХЃЌгУЛЇНјГЬЕФащФтЕижЗПеМфЛсБШФкКЫЕФащФтЕижЗПеМфаЁЕФЖрЃЌЪЧТ№ЃП

FransНЬЪкЃКБОжЪЩЯРДЫЕЃЌСНБпЕФащФтЕижЗПеМфДѓаЁЪЧвЛбљЕФЁЃЕЋЪЧгУЛЇНјГЬЕФащФтЕижЗПеМфЪЙгУТЪЛсИќЕЭЁЃ

бЇЩњЬсЮЪЃКШчЙћЖрИіНјГЬЖМНЋФкДцгГЩфЕНСЫЭЌвЛИіЮяРэЮЛжУЃЌетРяЛсгХЛЏКЯВЂЕНЭЌвЛИіЕижЗТ№ЃП

FransНЬЪкЃКXV6ВЛЛсзіетбљЕФЪТЧщЃЌЕЋЪЧpage tableЪЕбщжагавЛВПЗжОЭЪЧзіетИіЪТЧщЁЃеце§ЕФВйзїЯЕЭГЛсзіетбљЕФЙЄзїЁЃЕБФуУЧЭъГЩСЫpage tableЪЕбщЃЌФуУЧОЭЛсЖдетаЉФкШнИќМгСЫНтЁЃ

ЃЈвдЯТЮЪД№РДздПЮГЬНсЪјВПЗжЃЌвдЮЊФкШнЯрЙиОЭвЦЙ§РДСЫЃЉ

бЇЩњЬсЮЪЃКУПИіНјГЬЖМЛсгаздМКЕФ3МЖЪїзДpage tableЃЌЭЈЙ§етИіpage tableНЋащФтЕижЗЗвыГЩЮяРэЕижЗЁЃЫљвдПДЦ№РДЕБЮвУЧНЋФкКЫащФтЕижЗЗвыГЩЮяРэЕижЗЪБЃЌЮвУЧВЂВЛашвЊkernelЕФpage tableЃЌвђЮЊНјГЬЛсЪЙгУздМКЕФЪїзДpage tableВЂЭъГЩЕижЗЗвыЃЈзЂЃЌВЛЬЋРэНтетИіЮЪЬтЕудкФФЃЉЁЃ

FransНЬЪкЃКЕБkernelДДНЈСЫвЛИіНјГЬЃЌеыЖдетИіНјГЬЕФpage tableвВЛсДгFree memoryжаЗжХфГіРДЁЃФкКЫЛсЮЊгУЛЇНјГЬЕФpage tableЗжХфМИИіpageЃЌВЂЬюШыPTEЁЃдкФГИіЪБМфЕуЃЌЕБФкКЫдЫааСЫетИіНјГЬЃЌФкКЫЛсНЋНјГЬЕФИљpage tableЕФЕижЗМгдиЕНSATPжаЁЃДгФЧИіЪБМфЕуПЊЪМЃЌДІРэЦїЛсЪЙгУФкКЫЮЊФЧИіНјГЬЙЙНЈЕФащФтЕижЗПеМфЁЃ

ЭЌвЛИібЇЩњЬсЮЪЃКЫљвдФкКЫЮЊНјГЬЗХЦњСЫвЛаЉздМКЕФФкДцЃЌЕЋЪЧНјГЬЕФащФтЕижЗПеМфРэТлЩЯгыФкКЫЕФащФтЕижЗПеМфвЛбљДѓЃЌЫфШЛЪЕМЪжаПЯЖЈВЛЛсетУДДѓЁЃ

FransНЬЪкЃКЪЧЕФЃЌЯТЭМЪЧгУЛЇНјГЬЕФащФтЕижЗПеМфЗжВМЃЌгыФкКЫЕижЗПеМфвЛбљЃЌЫќвВЪЧДг0ЕНMAXVAЁЃ

ЫќгагЩФкКЫЩшжУКУЕФЃЌзЈЪєгкНјГЬЕФpage tableРДЭъГЩЕижЗЗвыЁЃ

бЇЩњЬсЮЪЃКЕЋЪЧЮвУЧВЛФмНЋЫљгаЕФMAXVAЕижЗЖМЪЙгУАЩЃП

FransНЬЪкЃКЪЧЕФЮвУЧВЛФмЃЌетбљЮвУЧЛсКФОЁФкДцЁЃДѓЖрЪ§ЕФНјГЬЪЙгУЕФФкДцЖМдЖдЖаЁгкащФтЕижЗПеМфЁЃ

XV6жаЕФащФтФкДцДњТы

kvminit КЏЪ§

НгЯТРДЃЌШУЮвУЧПДвЛПДДњТыЃЌЮвШЯЮЊКмЖрЖЋЮїЖМЛсвђДЫБфЕУИќМгЧхЮњЁЃ

ЪзЯШЃЌЮвУЧРДзівЛИіЕФГЃЙцВйзїЃЌЦєЖЏЮвУЧЕФXV6ЃЌетРяQEMUЪЕЯжСЫжїАхЃЌЭЌЪБЮвУЧДђПЊgdbЁЃ

ЩЯвЛДЮЮвУЧПДСЫbootЕФСїГЬЃЌЮвУЧИњЕНСЫmainКЏЪ§ЁЃmainКЏЪ§жаЕїгУЕФвЛИіКЏЪ§ЪЧkvminitЃЈ3.9ЃЉЃЌетИіКЏЪ§ЛсЩшжУКУkernelЕФЕижЗПеМфЁЃkvminitЕФДњТыШчЯТЃК

void

kvminit()

{

kernel_pagetable = (pagetable_t) kalloc();memset(kernel_pagetable, 0, PGSIZE);// uart registerskvmmap(UART0, UART0, PGSIZE, PTE_R | PTE_W);// virtio mmio disk interfacekvmmap(VIRTIO0, VIRTIO0, PGSIZE, PTE_R | PTE_W);// CLINTkvmmap(CLINT, CLINT, 0x10000, PTE_R | PTE_W);// PLICkvmmap(PLIC, PLIC, 0x400000, PTE_R | PTE_W);// map kernel text executable and read-only.kvmmap(KERNBASE, KERNBASE, (uint64)etext-KERNBASE, PTE_R | PTE_X);// map kernel data and the physical RAM we'll make use of.kvmmap((uint64)etext, (uint64)etext, PHYSTOP-(uint64)etext, PTE_R | PTE_W);// map the trampoline for trap entry/exit to// the highest virtual address in the kernel.kvmmap(TRAMPOLINE, (uint64)trampoline, PGSIZE, PTE_R | PTE_X);

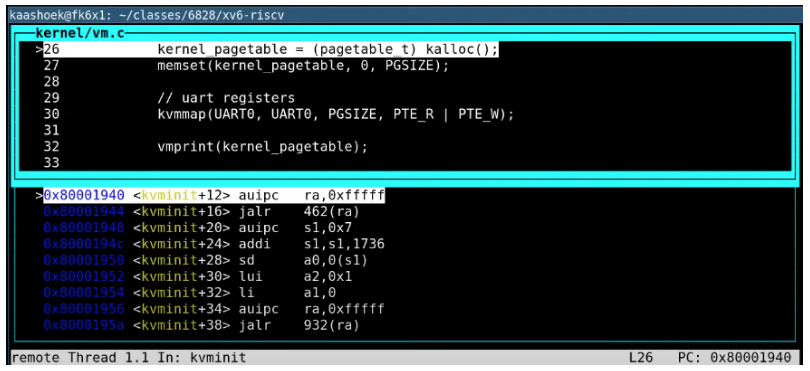

}ЮвУЧдкЧАвЛВПЗжПДСЫkernelЕФЕижЗПеМфГЄГЩЪВУДбљЃЌетРяЮвУЧРДПДвЛЯТДњТыЪЧШчКЮНЋЫќЩшжУКУЕФЁЃЪзЯШдкkvminitжаЩшжУвЛИіЖЯЕуЃЌжЎКѓдЫааДњТыЕНЖЯЕуЮЛжУЁЃдкgdbжажДааlayout splitЃЌПЩвдПДЕНЃЈДгЩЯУцЕФДњТывВПЩвдПДГіЃЉКЏЪ§ЕФЕквЛВНЪЧЮЊзюИпвЛМЖpage directoryЗжХфЮяРэpageЃЈзЂЃЌЕїгУkallocОЭЪЧЗжХфЮяРэpageЃЉЁЃЯТвЛааНЋетЖЮФкДцГѕЪМЛЏЮЊ0ЁЃ

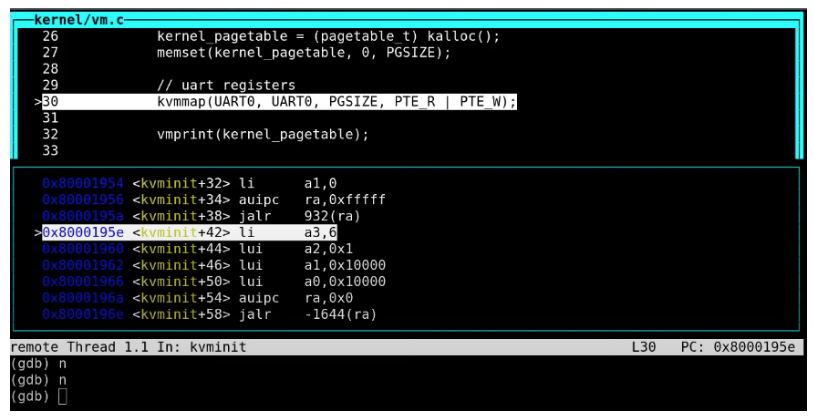

жЎКѓЃЌЭЈЙ§kvmmapКЏЪ§ЃЌНЋУПвЛИіI/OЩшБИгГЩфЕНФкКЫЁЃР§ШчЃЌЯТЭМжаИпССЕФааНЋUART0гГЩфЕНФкКЫЕФЕижЗПеМфЁЃ

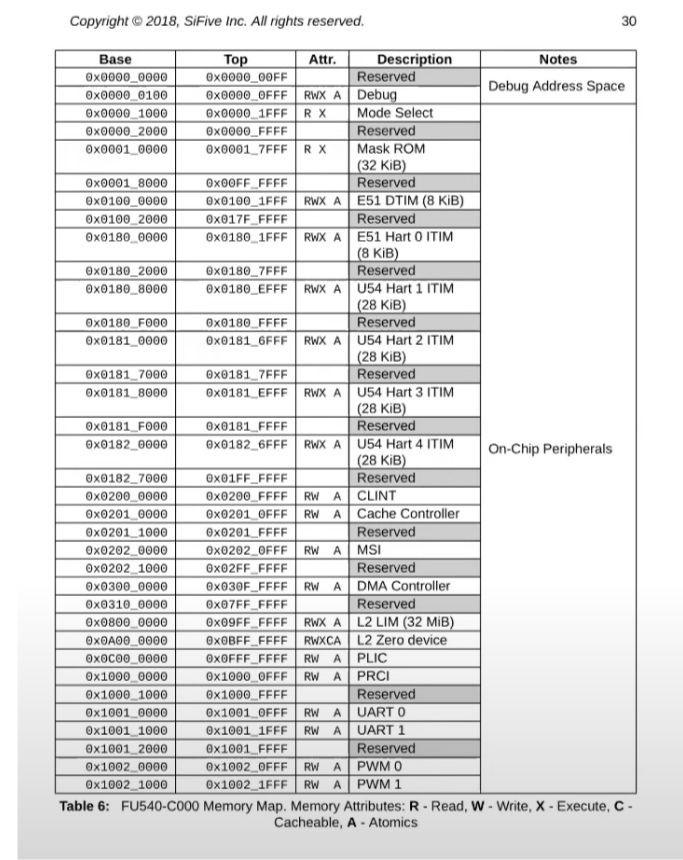

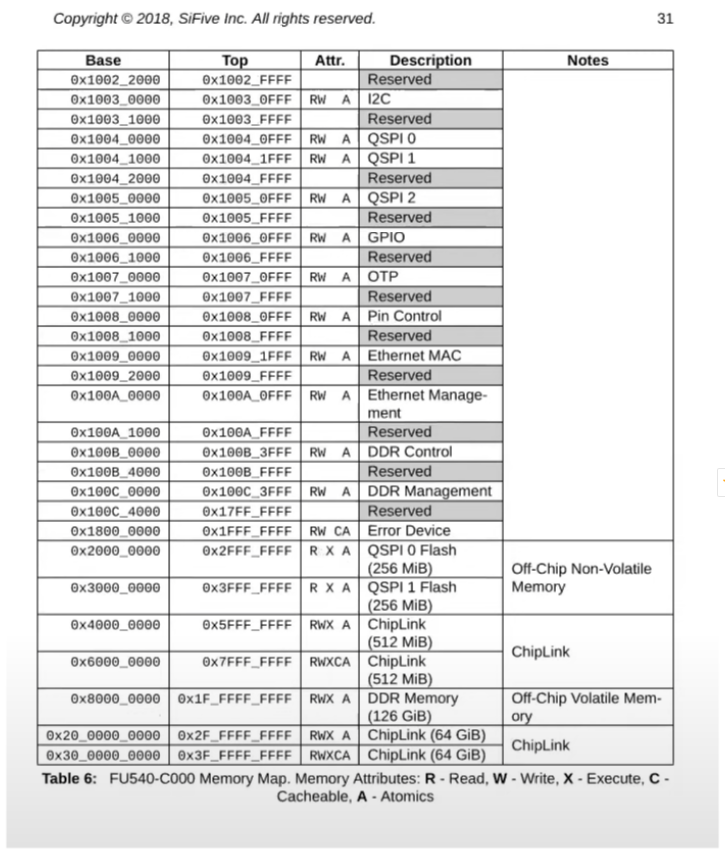

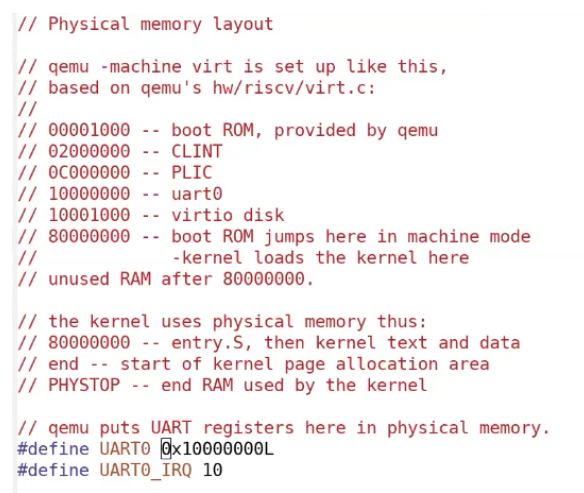

ЮвУЧПЩвдВщПДвЛИіЮФМўНазіmemlayout.hЃЌЫќНЋ4.5жаЕФЮФЕЕЗвыГЩСЫвЛЖбГЃСПЁЃдкетИіЮФМўРяУцПЩвдПДЕНЃЌUART0ЖдгІСЫЕижЗ0x10000000ЃЈзЂЃЌ4.5жаЕФЮФЕЕЪЧеце§SiFive RISC-VЕФЮФЕЕЃЌЖјЯТЭМЪЧQEMUЕФЕижЗЃЌЫљвд4.5жаЕФЮФЕЕЕижЗгыетРяЕФВЛЗћЃЉЁЃ

ЫљвдЃЌЭЈЙ§kvmmapПЩвдНЋЮяРэЕижЗгГЩфЕНЯрЭЌЕФащФтЕижЗЃЈзЂЃЌвђЮЊkvmmapЕФЧАСНИіВЮЪ§вЛжТЃЉЁЃ

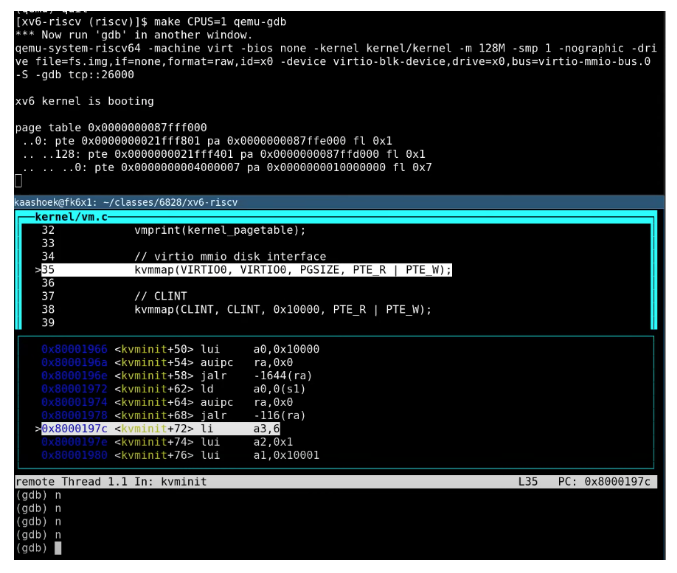

дкpage tableЪЕбщжаЃЌЕквЛИіСЗЯАЪЧЪЕЯжvmprintЃЌетИіКЏЪ§ЛсДђгЁЕБЧАЕФkernel page tableЁЃЮвУЧЯждкЬјЙ§етИіКЏЪ§ЃЌПДвЛЯТжДааЭъЕквЛИіkvmmapЪБЕФkernel page tableЁЃ

ЮвУЧРДПДвЛЯТетРяЕФЪфГіЁЃЕквЛааЪЧзюИпвЛМЖpage directoryЕФЕижЗЃЌетОЭЪЧДцдкSATPЛђепНЋЛсДцдкSATPжаЕФЕижЗЁЃЕкЖўааПЩвдПДЕНзюИпвЛМЖpage directoryжЛгавЛЬѕPTEађКХЮЊ0ЃЌЫќАќКЌСЫжаМфМЖpage directoryЕФЮяРэЕижЗЁЃЕкШ§ааПЩвдПДЕНжаМфМЖЕФpage directoryжЛгавЛЬѕPTEађКХЮЊ128ЃЌЫќжИЯђСЫзюЕЭМЖpage directoryЕФЮяРэЕижЗЁЃЕкЫФааПЩвдПДЕНзюЕЭМЖЕФpage directoryАќКЌСЫPTEжИЯђЮяРэЕижЗЁЃФуУЧПЩвдПДЕНзюЕЭвЛМЖ page directoryжаPTEЕФЮяРэЕижЗОЭЪЧ0x10000000ЃЌЖдгІСЫUART0ЁЃ

ЧАУцЪЧЮяРэЕижЗЃЌЮвУЧПЩвдДгащФтЕижЗЕФНЧЖШРДбщжЄетРяЗћКЯдЄЦкЁЃЮвУЧНЋЕижЗ0x10000000ЯђгввЦЮЛ12bitЃЌетбљПЩвдЕУЕНащФтЕижЗЕФИп27bitЃЈindexВПЗжЃЉЁЃжЎКѓЮвУЧдйЖдетВПЗжгввЦЮЛ9bitЃЌВЂДђгЁГЩ10НјжЦЪ§ЃЌПЩвдЕУЕН128ЃЌетОЭЪЧжаМфМЖpage directoryжаPTEЕФађКХЁЃетгыжЎЧАЃЈ4.4ЃЉНщЩмЕФФкШнЪЧЗћКЯЕФЁЃ

ДгБъжОЮЛРДПДЃЈflВПЗжЃЉЃЌзюЕЭвЛМЖpage directoryжаЕФPTEгаЖСаДБъжОЮЛЃЌВЂЧвValidБъжОЮЛвВЩшжУСЫЃЈ4.3ЕзВПгаБъжОЮЛЕФНщЩмЃЉЁЃ

ФкКЫЛсГжајЕФАДееетжжЗНЪНЃЌЕїгУkvmmapРДЩшжУЕижЗПеМфЁЃжЎКѓЛсЖдVIRTIO0ЁЂCLINTЁЂPLICЁЂkernel textЁЂkernel dataЁЂзюКѓЪЧTRAMPOLINEНјааЕижЗгГЩфЁЃзюКѓЮвУЧЛЙЛсЕїгУvmprintДђгЁЭъећЕФkernel page directoryЃЌПЩвдПДГівбОЩшжУСЫКмЖрPTEЁЃ

етРяОЭВЛЙ§ЯИНкСЫЃЌЕЋЪЧетаЉPTEЙЙГЩСЫЮвУЧдк4.5жаПДЕНЕФЕижЗПеМфЖдгІЙиЯЕЁЃ

ЃЈЯТУцЮЪД№РДздПЮГЬНсЪјВПЗжЃЌвђЮЊФкШнЯрЙиОЭвЦЕНетРяЁЃЃЉ

бЇЩњЃКЯТУцетСНааФкДцВЛЛсдННчТ№ЃП

FransЃКВЛЛсЁЃетРяKERNBASEЪЧ0x80000000ЃЌетЪЧФкДцПЊЪМЕФЕижЗЁЃkvmmapЕФЕкШ§ИіВЮЪ§ЪЧsizeЃЌetextЪЧkernel textЕФзюКѓвЛИіЕижЗЃЌetext - KERNBASEЛсЗЕЛиkernel textЕФзжНкЪ§ЃЌЮвВЛШЗЖЈетПщгаЖрДѓЃЌДѓИХЪЧ60-90ИіpageЃЌетВПЗжЪЧkernelЕФtextВПЗжЁЃPHYSTOPЪЧЮяРэФкДцЕФзюДѓЮЛжУЃЌPHYSTOP-textЪЧkernelЕФdataВПЗжЁЃЛсгазуЙЛЕФDRAMРДЭъГЩетРяЕФгГЩфЁЃ

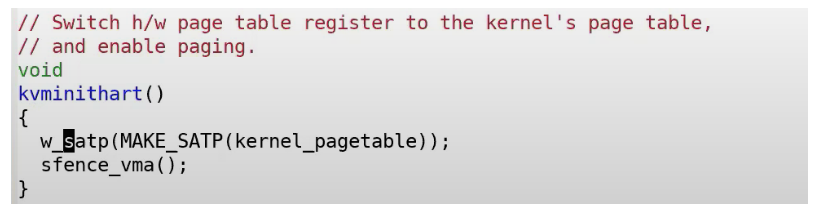

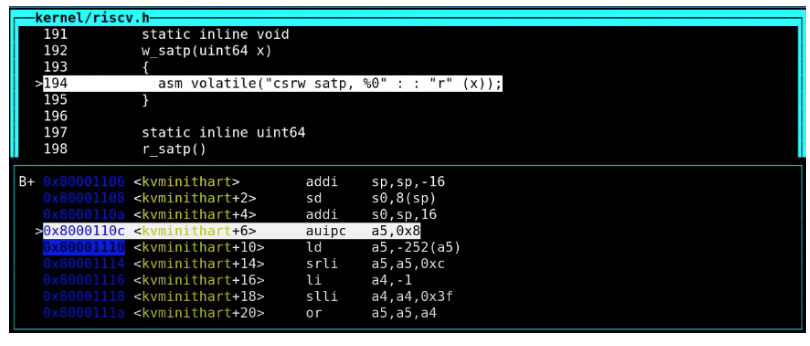

kvminithart КЏЪ§

жЎКѓЃЌkvminitКЏЪ§ЗЕЛиСЫЃЌдкmainКЏЪ§жаЃЌЮвУЧдЫааЕНСЫkvminithartКЏЪ§ЁЃ

етИіКЏЪ§ЪзЯШЩшжУСЫSATPМФДцЦїЃЌkernel_pagetableБфСПРДздгкkvminitЕквЛааЁЃЫљвдетРяЪЕМЪЩЯЪЧФкКЫИцЫпMMUРДЪЙгУИеИеЩшжУКУЕФpage tableЁЃЕБетРяетЬѕжИСюжДаажЎКѓЃЌЯТвЛИіжИСюЕФЕижЗЛсЗЂЩњЪВУДЃП

дкетЬѕжИСюжЎЧАЃЌЛЙВЛДцдкПЩгУЕФpage tableЃЌЫљвдвВОЭВЛДцдкЕижЗЗвыЁЃжДааЭъетЬѕжИСюжЎКѓЃЌГЬађМЦЪ§ЦїЃЈProgram CounterЃЉдіМгСЫ4ЁЃЖјжЎКѓЕФЯТвЛЬѕжИСюБЛжДааЪБЃЌГЬађМЦЪ§ЦїЛсБЛФкДцжаЕФpage tableЗвыЁЃ

ЫљвдетЬѕжИСюЕФжДааЪБПЬЪЧвЛИіЗЧГЃживЊЕФЪБПЬЁЃвђЮЊећИіЕижЗЗвыДгетЬѕжИСюжЎКѓПЊЪМЩњаЇЃЌжЎКѓЕФУПвЛИіЪЙгУЕФФкДцЕижЗЖМПЩФмЖдгІЕНгыжЎВЛЭЌЕФЮяРэФкДцЕижЗЁЃвђЮЊдкетЬѕжИСюжЎЧАЃЌЮвУЧЪЙгУЕФЖМЪЧЮяРэФкДцЕижЗЃЌетЬѕжИСюжЎКѓpage tableПЊЪМЩњаЇЃЌЫљгаЕФФкДцЕижЗЖМБфГЩСЫСэвЛИіКЌвхЃЌвВОЭЪЧащФтФкДцЕижЗЁЃ

етРяФме§ГЃЙЄзїЕФдвђЪЧжЕЕУзЂвтЕФЁЃвђЮЊЧАвЛЬѕжИСюЛЙЪЧдкЮяРэФкДцжаЃЌЖјКѓвЛЬѕжИСювбОдкащФтФкДцжаСЫЁЃБШШчЃЌЯТвЛЬѕжИСюЕижЗЪЧ0x80001110ОЭЪЧвЛИіащФтФкДцЕижЗЁЃ

ЮЊЪВУДетРяФме§ГЃЙЄзїФиЃПвђЮЊkernel pageЕФгГЩфЙиЯЕжаЃЌащФтЕижЗЕНЮяРэЕижЗЪЧЭъШЋЯрЕШЕФЁЃЫљвдЃЌдкЮвУЧДђПЊащФтЕижЗЗвыгВМўжЎКѓЃЌЕижЗЗвыгВМўЛсНЋвЛИіащФтЕижЗЗвыЕНЯрЭЌЕФЮяРэЕижЗЁЃЫљвдЪЕМЪЩЯЃЌЮвУЧзюжеЛЙЪЧФмЭЈЙ§ФкДцЕижЗжДааЕНе§ШЗЕФжИСюЃЌвђЮЊОЙ§ЕижЗЗвы0x80001110ЛЙЪЧЖдгІ0x80001110ЁЃ

ЙмРэащФтФкДцЕФвЛИіФбЕуЪЧЃЌвЛЕЉжДааСЫРрЫЦгкSATPетбљЕФжИСюЃЌФуЯрЕБгкНЋвЛИіpage tableМгдиЕНСЫSATPМФДцЦїЃЌФуЕФЪРНчЭъШЋИФБфСЫЁЃЯждкУПвЛИіЕижЗЖМЛсБЛФуЩшжУКУЕФpage tableЫљЗвыЁЃФЧУДМйЩшФуЕФpage tableЩшжУДэЮѓСЫЃЌЛсЗЂЩњЪВУДФиЃПгаШЫЯыЛиД№етИіЮЪЬтТ№ЃП

бЇЩњAЛиД№ЃКФуПЩФмЛсИВИЧkernel dataЁЃ

бЇЩњBЛиД№ЃКЛсВњЩњpage faultЁЃ

ЪЧЕФЃЌвђЮЊpage tableУЛгаЩшжУКУЃЌащФтЕижЗПЩФмИљБООЭЗвыВЛСЫЃЌФЧУДФкКЫЛсЭЃжЙдЫааВЂpanicЁЃЫљвдЃЌШчЙћpage tableжагаbugЃЌФуНЋЛсПДЕНЦцЙжЕФДэЮѓКЭБРРЃЃЌетЕМжТСЫpage tableЪЕбщНЋЛсБШНЯФбЁЃШчЙћФуВЛЙЛаЁаФЃЌЛђепФуУЛгаЭъШЋРэНтвЛаЉЯИНкЃЌФуПЩФмЛсЕМжТkernelБРРЃЃЌетНЋЛсЛЈЗбвЛаЉЪБМфКЭОЋСІРДзЗзйБГКѓЕФдвђЁЃЕЋетОЭЪЧЙмРэащФтФкДцЕФвЛВПЗжЃЌвђЮЊЖдгквЛИіетУДЧПДѓЕФЙЄОпЃЌШчЙћГіДэСЫЃЌЯргІЕФФувВЛсЕУЕНбЯжиЕФКѓЙћЁЃЮвВЂВЛЪЧвЊИјФуУЧЦУСЙЫЎЃЌЙўЙўЁЃСэвЛЗНУцЃЌетвВКмгаРжШЄЃЌОЙ§СЫpage tableЪЕбщЃЌФуУЧЛсеце§РэНтащФтФкДцЪЧЪВУДЃЌащФтФкДцФмзіЪВУДЁЃ

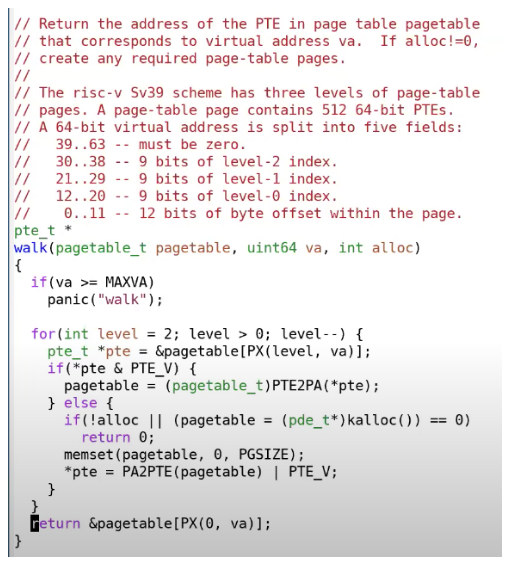

walk КЏЪ§

бЇЩњЬсЮЪЃКЮвЖдгкwalkКЏЪ§гаИіЮЪЬтЃЌДгДњТыПДЫќЗЕЛиСЫзюИпМЖpage tableЕФPTEЃЌЕЋЪЧЫќЪЧдѕУДЙЄзїЕФФиЃПЃЈзЂЃЌгІИУЪЧбЇЩњРэНтгаЮѓЃЌwalkКЏЪ§ФЃФтСЫMMUЃЌЗЕЛиЕФЪЧvaЖдгІЕФзюЕЭМЖpage tableЕФPTEЃЉ

FransНЬЪкЃКетИіКЏЪ§ЛсЗЕЛиpage tableЕФPTEЃЌЖјФкКЫПЩвдЖСаДPTEЁЃЮвРДЛИіЭМЃЌЪзЯШЮвУЧгавЛИіpage directoryЃЌетИіpage directory га512ИіPTEЁЃзюЯТУцЪЧ0ЃЌзюЩЯУцЪЧ511ЁЃ

етИіКЏЪ§ЕФзїгУЪЧЗЕЛиФГвЛИіPTEЕФжИеыЁЃ

етЪЧИіащФтЕижЗЃЌЫќжИЯђСЫетИіPTEЁЃжЎКѓФкКЫПЩвдЭЈЙ§ЯђетИіЕижЗаДЪ§ОнРДВйзнетЬѕPTEжДааЕФЮяРэpageЁЃЕБpage tableБЛМгдиЕНSATPМФДцЦїЃЌетРяЕФИќИФОЭЛсЩњаЇЁЃ

ДгДњТыПДЃЌетИіКЏЪ§Дгlevel2зпЕНlevel1ШЛКѓЕНlevel0ЃЌШчЙћВЮЪ§allocВЛЮЊ0ЃЌЧвФГвЛИіlevelЕФpage tableВЛДцдкЃЌетИіКЏЪ§ЛсДДНЈвЛИіСйЪБЕФpage tableЃЌНЋФкШнГѕЪМЛЏЮЊ0ЃЌВЂМЬајдЫааЁЃЫљвдзюКѓзмЪЧЗЕЛиЕФЪЧзюЕЭвЛМЖЕФpage directoryЕФPTEЁЃ

ШчЙћВЮЪ§allocУЛгаЩшжУЃЌФЧУДдкЕквЛИіPTEЖдгІЕФЯТвЛМЖpage tableВЛДцдкЪБОЭЛсЗЕЛиЁЃ

бЇЩњЬсЮЪЃКЖдгкwalkКЏЪ§ЃЌЮвгавЛИіБШНЯРЇЛѓЕФЕиЗНЃЌдкаДЭъSATPМФДцЦїжЎКѓЃЌФкКЫЛЙФмжБНгЗУЮЪЮяРэЕижЗТ№ЃПдкДњТыРяУцПДЦ№РДЯёЪЧЭЈЙ§page tableНЋащФтЕижЗЗвыГЩСЫЮяРэЕижЗЃЌЕЋЪЧетИіЪБКђSATPвбОБЛЩшжУСЫЃЌЕУЕНЕФЮяРэЕижЗВЛЛсБЛШЯЮЊЪЧащФтЕижЗТ№ЃП

FransНЬЪкЃКШУЮвУЧРДПДkvminithartКЏЪ§ЃЌетРяЕФkernel_page_tableЪЧвЛИіЮяРэЕижЗЃЌВЂаДШыЕНSATPМФДцЦїжаЁЃДгФЧвдКѓЃЌЮвУЧЕФДњТыдЫаадквЛИіЮвУЧЙЙНЈГіРДЕФЕижЗПеМфжаЁЃдкжЎЧАЕФkvminitКЏЪ§жаЃЌkvmmapЛсЖдУПИіЕижЗЛђепУПИіpageЕїгУwalkКЏЪ§ЁЃЫљвдФуЕФЮЪЬтЪЧЪВУДЃП

бЇЩњЃКЮвЯыжЊЕРЃЌдкSATPМФДцЦїЩшжУЭъжЎКѓЃЌwalkЪЧВЛЪЧЛЙЪЧАДееЯрЭЌЕФЗНЪНЙЄзїЃП

FransЃКЪЧЕФЁЃЫќЛЙФмЙЄзїЕФдвђЪЧЃЌФкКЫЩшжУСЫащФтЕижЗЕШгкЮяРэЕижЗЕФгГЩфЙиЯЕЃЌетРяКмживЊЃЌвђЮЊКмЖрЕиЗНФмЙЄзїЕФдвђЖМЪЧвђЮЊФкКЫЩшжУЕФЕижЗгГЩфЙиЯЕЪЧЯрЭЌЕФЁЃ

бЇЩњЃКУПвЛИіНјГЬЕФSATPМФДцЦїДцдкФФЃП

FransЃКУПИіCPUКЫжЛгавЛИіSATPМФДцЦїЃЌЕЋЪЧдкУПИіprocНсЙЙЬхЃЌШчЙћФуВщПДproc.hЃЌРяУцгавЛИіжИЯђpage tableЕФжИеыЃЌетЖдгІСЫНјГЬЕФИљpage tableЮяРэФкДцЕижЗЁЃ

бЇЩњЬсЮЪЃКЮЊЪВУДЭЈЙ§3МЖpage tableЛсБШвЛИіГЌДѓЕФpage tableИќКУФиЃП

FransНЬЪкЃКетЪЧИіКУЮЪЬтЃЌетЕФдвђЪЧЃЌ3МЖpage tableжаЃЌДѓСПЕФPTEЖМПЩвдВЛДцДЂЁЃБШШчЃЌЖдгкзюИпМЖЕФpage tableРяУцЃЌШчЙћвЛИіPTEЮЊПеЃЌФЧУДФуОЭЭъШЋВЛгУДДНЈЫќЖдгІЕФжаМфМЖКЭзюЕзВуpage tableЃЌвдМАРяУцЕФPTEЁЃЫљвдЃЌетОЭЪЧЯёЪЧдкећИіащФтЕижЗПеМфжаЕФвЛДѓЖЮЕижЗЭъШЋВЛашвЊгагГЩфвЛбљЁЃ

бЇЩњЃКЫљвд3МЖpage tableОЭЯёЪЧАДашЗжХфетаЉгГЩфПщЁЃ

FransНЬЪкЃКЪЧЕФЃЌОЭЯёЧАУцЃЈ4.6ЃЉНщЩмЕФвЛбљЁЃзюПЊЪМФужЛга3Иіpage tableЃЌвЛИіЪЧзюИпМЖЃЌвЛИіЪЧжаМфМЖЃЌвЛИіЪЧзюЕЭМЖЕФЁЃЫцзХДњТыЕФдЫааЃЌЮвУЧЛсДДНЈИќЖрЕФpage table diretoryЁЃ