本文主要探讨使用EMIO实现PS端的SPI接口,目前得出的结论是:可以实现,但需要占用两个芯片管脚用于输出片选信号。

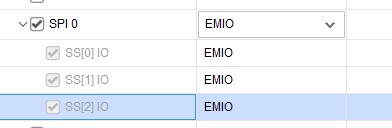

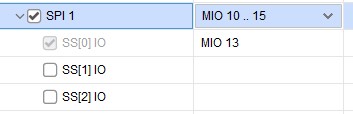

首先在zynq的MIO Configuration配置中可以看到,如果SPI接口配置为MIO实现,则可以选择是否是多设备,但是如果配置为EMIO实现,则无法选择,SS[0],SS[1],SS[2]都强制勾选了。

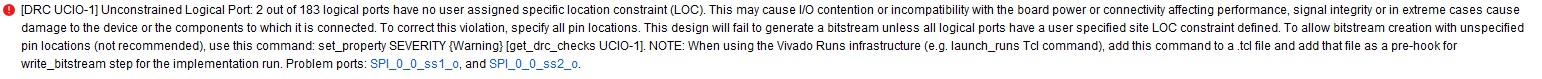

其次,在进行管脚分配时,哪怕不使用片选信号,SPI_0_ 0_ss1_o和SPI_0_ 0_ss2_o必须分配管脚,否则Synthesis和Implement都可以通过,但生成比特流时,会出现如下的管脚未配置错误:

最后,这个问题在Xilinx论坛上有过讨论,但时隔7年依然没有解决:

https://support.xilinx.com/s/question/0D52E00006hpTirSAE/zynq-ps-spi-how-to-constrain-if-ss0ss1ss2-are-not-used?language=en_US

链接中提出了一个跳过这个错误的方法,但是我没有尝试,我最后选择了分配两个用不到的管脚:

If you want to bypass this error, you need to place the following constraints in your xdc file-

set_property SEVERITY {Warning} [get_drc_checks NSTD-1]set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

分配两个原理图上悬空的管脚AC24,AK23,此次生成bitstream成功: