今天调试LCD驱动,LCD驱动是:Sharp LQ104V1DG61

首先要配置一些lcd的时序之类的,比如如下:

vspw, vbpd, vfpd, hspw, hbpd, hfpd...

看了半天lcd的时序图,我也没看懂到底是怎么算的,哪个懂的大侠给提供个思路啊,这些到底怎么配呢?

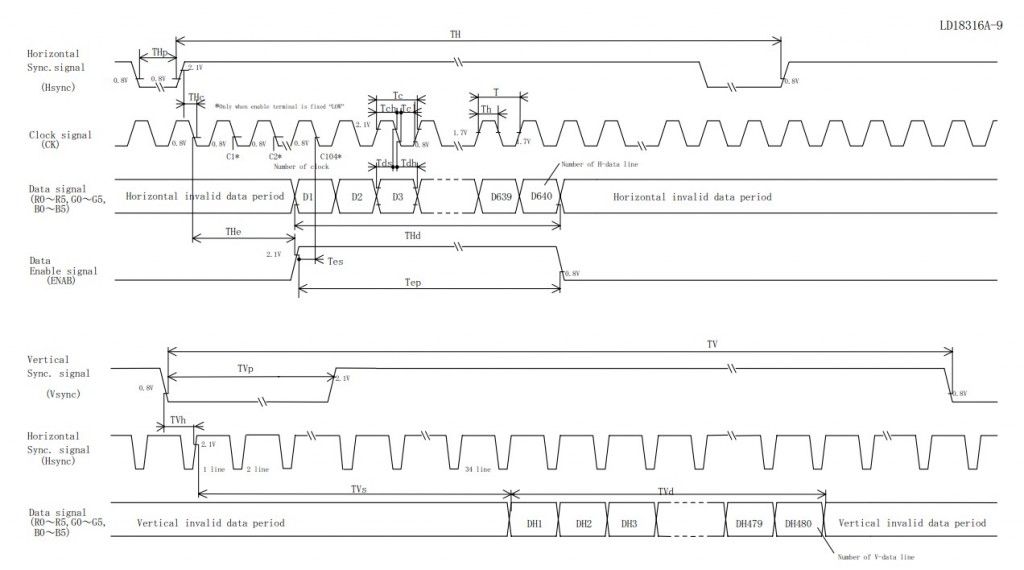

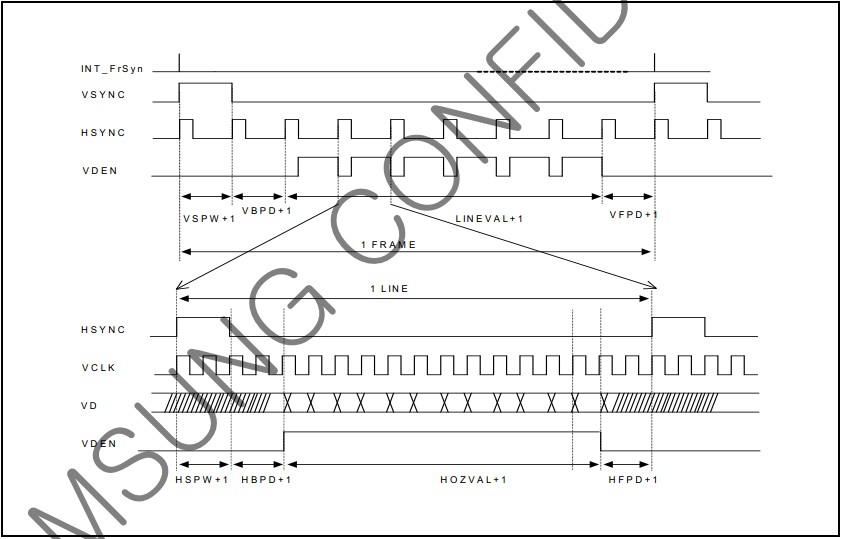

下面是s5pv210的芯片上的lcd控制时序:

lcd时序图如何看

------解决方案--------------------

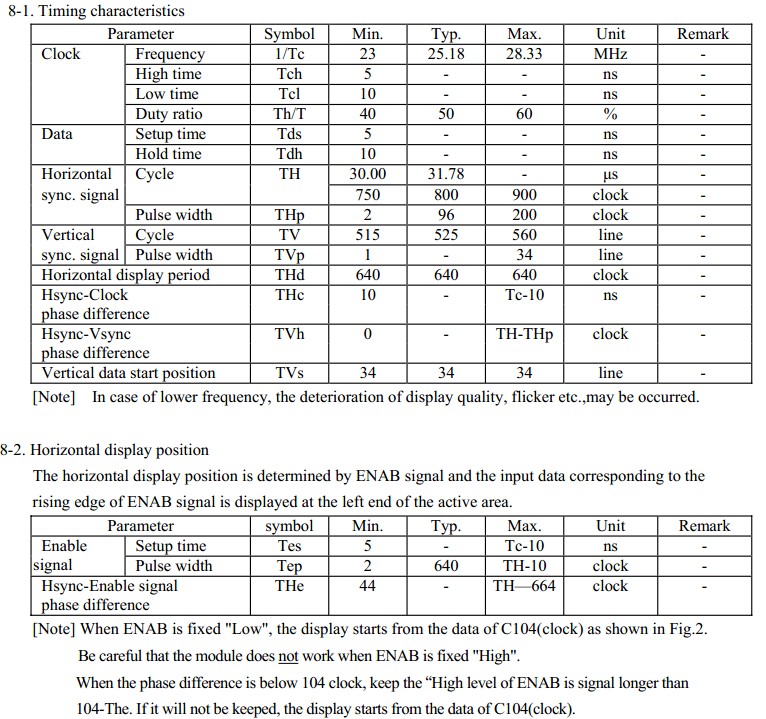

嗯你贴那个LCD屏的时序参数表感觉没什么有用信息啊,手册中是不是还有别的表……

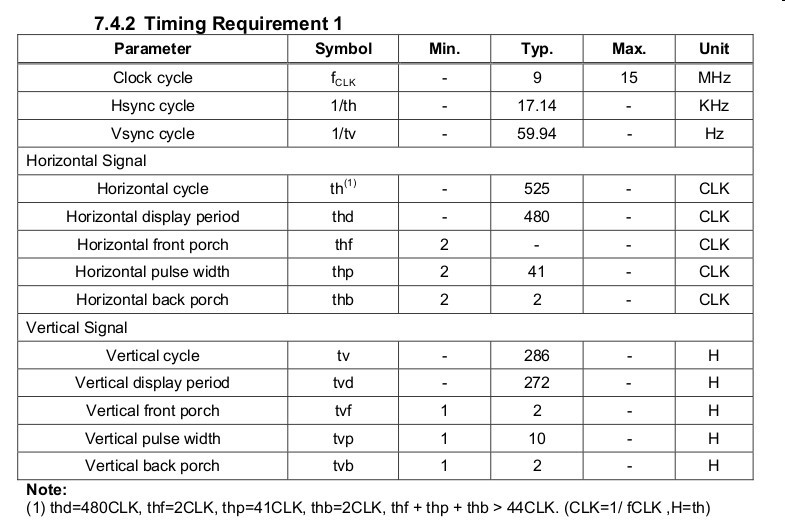

我给你看一下我LCD屏的时序参数表1,还有一个表2和你贴出的那个内容相仿(我未贴出):

以下内容仅供参考,不保证对你有用:

先说说你提到的那些参数,在linux中有一个结构体来描述它们:

//初始化LCD显示器参数,结构体内的数值是以上面图表内容为依据填的

voidinit_res_modes()

{

//init ctfb_res_modes

/*表示从水平同步信号开始到一行的有效数据开始之间的VCLK的个数*/

res_mode->left_margin= 2; // HFPD

/*表示一行的有效数据结束到下一个水平同步信号开始之间的VCLK的个数*/

res_mode->right_margin= 2; // HBPD

/*表示水平同步信号的宽度,用VCLK计算*/

res_mode->hsync_len =41; // HSPW

/*表示在一帧图像开始时,垂直同步信号以后的无效的行数*/

res_mode->upper_margin =2; // VFPD

/*表示在一帧图像结束后,垂直同步信号以前的无效的行数*/

res_mode->lower_margin =2; // VBPD

/*表示垂直同步脉冲的宽度,用行数计算*/

res_mode->vsync_len =10; // VSPW

/*LCD像素尺寸、分辨率*/

res_mode->xres =480;

res_mode->yres =272;

/*DOTCLK = fframe × (X + HBP + HFP+HSPW) × (Y + VBP + VFP+VSPW)(单位:MHz)*/

/*pixclock = 10的12次方/DOTCLK (单位:皮秒)fframe表帧率,一般取60*/

res_mode->pixclock =88800;

res_mode->sync =0;

}

1.定位文件

进入linux源代码目录树中的“/drivers/video”目录:

通过分析Kconfig文件及Makefile文件里的如下行得知我板子使用的驱动文件为"s3c-fb.c"

“obj-$(CONFIG_FB_S3C) += s3c-fb.o”

2.定位代码

打开"s3c-fb.c"文件,查probe函数(通常这些有关设备初始化的东西都在此函数)。一路看下去发现有个函数名为“s3c_fb_set_rgb_timing”推测可能是设置时序的函数(后经分析确实是)进去再看!

3.分析具体代码

static void s3c_fb_set_rgb_timing(struct s3c_fb *sfb)

{

struct fb_videomode *vmode = sfb->pdata->vtiming;

void __iomem *regs = sfb->regs;

int clkdiv;

u32 data;

//"pixclock"是像素时钟,SOC手册上有计算公式

if (!vmode->pixclock)

s3c_fb_missing_pixclock(vmode);

//通过“pixclock”来计算LCD控制器寄存器“CLKVAL_F”的分频值

clkdiv = s3c_fb_calc_pixclk(sfb, vmode->pixclock);

data = sfb->pdata->vidcon0;

data &= ~(VIDCON0_CLKVAL_F_MASK

------解决方案--------------------

VIDCON0_CLKDIR);

//查分频值是否有效,如分频值无效直接使用源时钟频(即不进行分频)

if (clkdiv > 1)

data

------解决方案--------------------

= VIDCON0_CLKVAL_F(clkdiv-1)

------解决方案--------------------

VIDCON0_CLKDIR;

else

data &= ~VIDCON0_CLKDIR; /* 1:1 clock */

if (sfb->variant.is_2443)

data

------解决方案--------------------

= (1 << 5);

writel(data, regs + VIDCON0);

data = VIDTCON0_VBPD(vmode->upper_margin - 1)

------解决方案--------------------

VIDTCON0_VFPD(vmode->lower_margin - 1)

------解决方案--------------------