Ӳ���Ǵ�Ҷ�����Ϥ���豸��һ·��������HDD��SSD����SATA��NVMe����ΪNVMe SSD��ǰ�˽ӿڣ�PCIe�ٴν������ǵ���Ұ����Ϊx86��ϵ�ؼ���һ����PCIe������PCI��PCI-X��PCIe���߹���30��ʱ�⡣����Host����������豸�ķ�ʽȴһ����Ϯ����������������һ��PCIe�豸��һ��ϵͳ������η�������ʵġ�

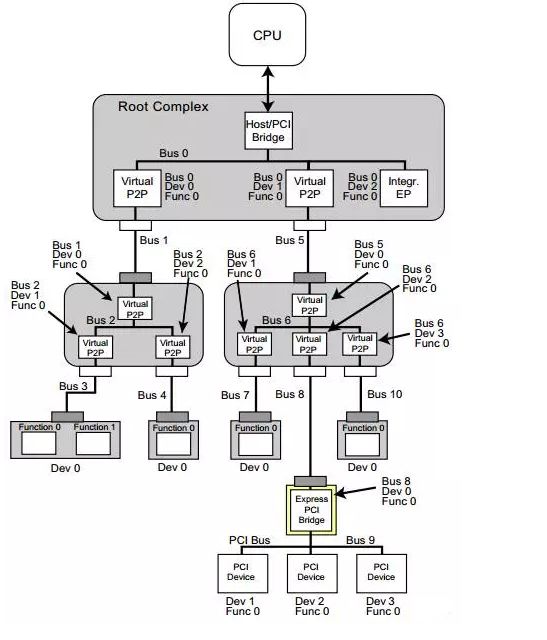

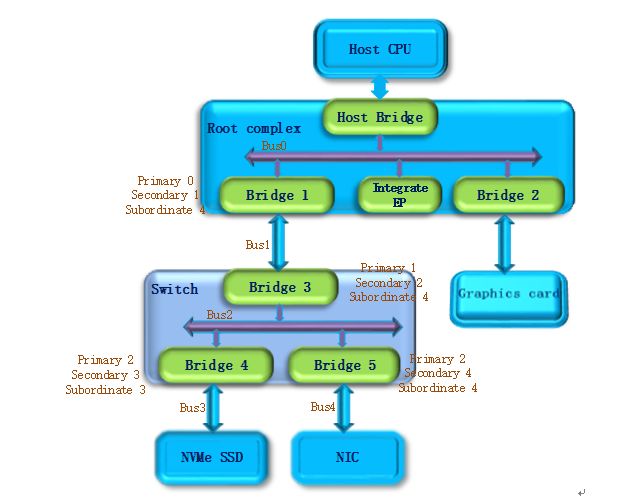

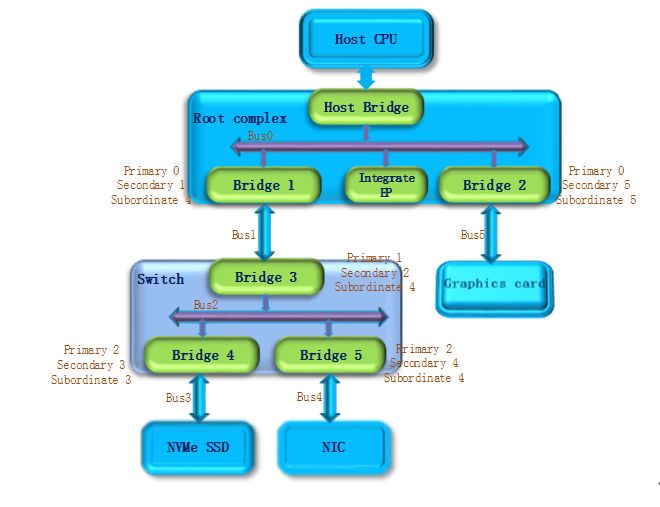

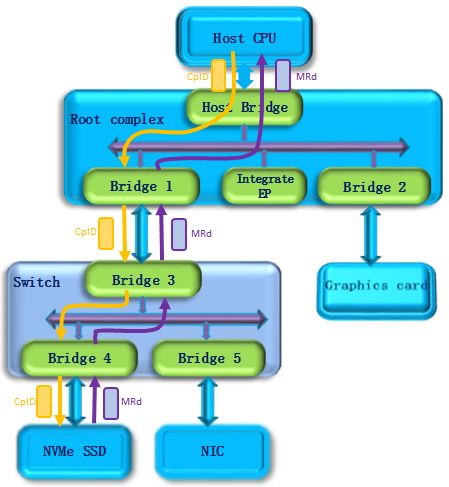

������������һ����x86ϵͳ�У�PCIe��ʲô����һ����ϵ�ܹ�����ͼ��һ��PCIe�����˽ṹʾ��,PCIeЭ��֧��256��Bus, ÿ��Bus���֧��32��Device��ÿ��Device���֧��8��Function��������BDF��Bus��device��function��������ÿ��PCIe�豸�ڵ������֤�š�

PCIe��ϵ�ܹ�һ����root complex��switch��endpoint�����͵�PCIe�豸��ɣ���root complex��switch��ͨ������һЩembeded endpoint(�����豸���ⲻ��PCIe�ӿ�)����ô����豸��CPU������Ҫ��ôȥ�ҵ����ϳ�������? Host��PCIe�豸ɨ���Dz�������������㷨������̼�Ҫ��˵�Ƕ�ÿһ�����ܵķ�֧·�����뵽����������Ϊֹ������ÿ���ڵ�ֻ�ܷ���һ�Ρ�����һ����������ΪPCIe�豸ö�١�ö�ٹ�����hostͨ�����ö����������ȡ�����豸����Ϣ��ͨ������д������������豸�������á�

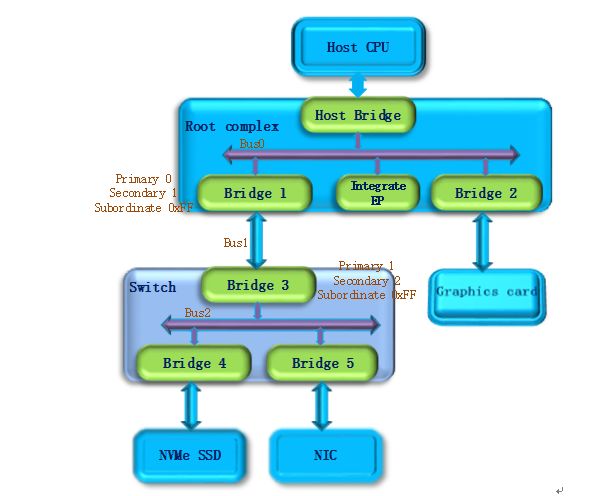

��һ����PCI Host����ɨ��Bus 0�ϵ��豸����һ��������ϵͳ�У�һ�㽫Root complex����Host Bridge�����ӵ�PCI��������ΪPCI Bus 0����ϵͳ���Ȼ����Bus 0�ϵ�embedded EP�Ȳ���ҽ�PCI�ŵ��豸�����ŷ���Bridge 1��Bridge1 �����PCI Bus��Ϊ Bus 1��ϵͳ����ʼ��Bridge 1�����ÿռ䣬�������ŵ�Primary Bus Number �� Secondary Bus Number�Ĵ����ֱ����ó�0��1���Ա���Bridge1 ������������0������������1�����ڻ���ȷ��Bridge1�¹����豸�ľ��������ϵͳ����ʱ��Subordinate Bus Number��Ϊ0xFF��

�ڶ�����ϵͳ��ʼɨ��Bus 1�����ᷢ��Bridge 3������������һ��switch�豸��ϵͳ��Bridge 3�����PCI Bus��ΪBus 2���������ŵ�Primary Bus Number �� Secondary Bus Number�Ĵ����ֱ����ó�1��2������һ��һ����ʱ��Bridge 3 ��Subordinate Bus Number��Ϊ0xFF��

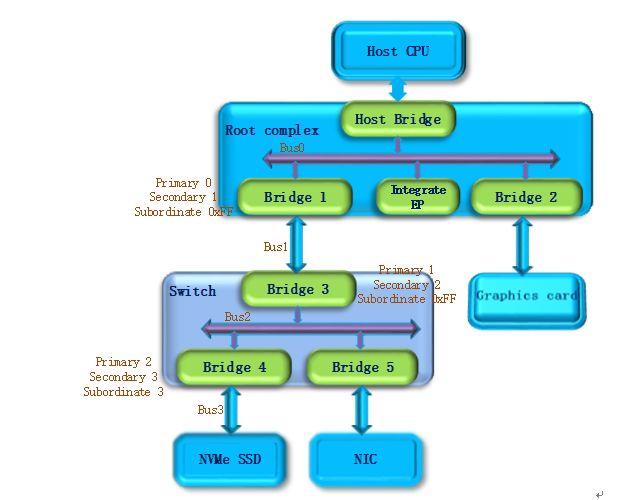

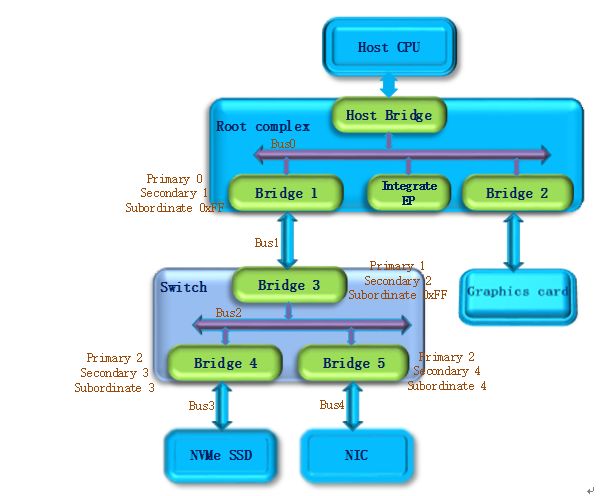

��������ϵͳ����ɨ��Bus 2�����ᷢ��Bridge 4������ɨ�裬ϵͳ�ᷢ��Bridge������ص�NVMe SSD�豸��ϵͳ��Bridge 4�����PCI Bus��ΪBus 3���������ŵ�Primary Bus Number �� Secondary Bus Number�Ĵ����ֱ����ó�2��3����ΪBus3����ҵ��Ƕ˵��豸��Ҷ�ӽڵ㣩�����治���������������ˣ����Bridge 4��Subordinate Bus Number��ֵ����ȷ��Ϊ3��

���IJ������Bus 3��ɨ���ϵͳ���ص�Bus 2����ɨ�裬�ᷢ��Bridge 5������ɨ�裬ϵͳ�ᷢ��������ص�NIC�豸��ϵͳ��Bridge 5�����PCI Bus����ΪBus 4���������ŵ�Primary Bus Number �� Secondary Bus Number�Ĵ����ֱ����ó�2��4����ΪNICͬ���Ƕ˵��豸��Bridge 5��Subordinate Bus Number��ֵ����ȷ��Ϊ4��

���岽������Bridge 4��Bridge 5���⣬Bus2����û�������豸�ˣ���˷��ص�Bridge 3��Bus 4���ҵ��Ĺ��������Bridge�µ����һ��bus�ţ���˽�Bridge 3��Subordinate Bus Number����Ϊ4��Bridge 3�������豸���Ѿ�ɨ����ϣ��������Ϸ��ص�Bridge 1��ͬ����Bridge 1��Subordinate Bus Number����Ϊ4��

��������ϵͳ���ص�Bus0����ɨ�裬�ᷢ��Bridge 2��ϵͳ��Bridge 2�����PCI Bus��ΪBus 5������Bridge 2��Primary Bus Number �� Secondary Bus Number�Ĵ����ֱ����ó�0��5�� Graphics cardҲ�Ƕ˵��豸�����Bridge 2 ��Subordinate Bus Number��ֵ����ȷ��Ϊ5��

���ˣ�����PCIe�����ϵ������豸����ɨ�赽��ö�ٹ��̽�����Hostͨ����һ���̻����һ��������PCIe�豸���˽ṹ��

ϵͳ�ϵ��Ժ�host���Զ�����������豸ö�ٹ��̡���һЩר��ϵͳ�⣬��ͨϵͳֻ���ڿ����ν��н����豸��ɨ�裬�����ɹ���ö�ٹ��̽���������ʹ����һ��PCIe�豸��ϵͳҲ������ȥʶ������

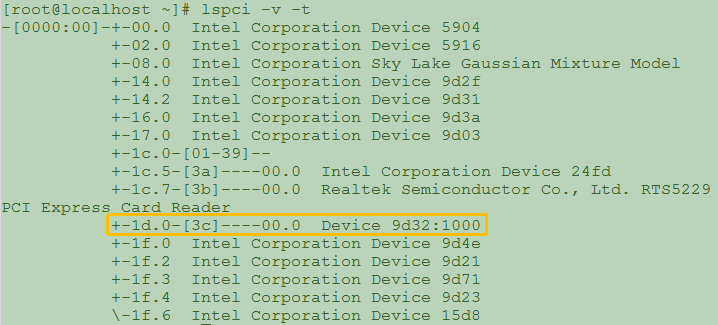

��linux����ϵͳ�У����ǿ���ͨ��lspci �Cv -t��������ѯϵͳ�ϵ��ɨ�赽��PCIe�豸��ִ�н������һ��������ʽ�г�ϵͳ�����е�pcie�豸������ͼ��ʾ�����л�ɫ�����е�PCIe�豸�DZ�����о�Ƽ���˾��Bejing Starblaze Technology Co., LTD.���Ƴ���STAR1000ϵ��NVMe SSD����оƬ��ͼ����ʾ��9d32��Starblaze��PCI-SIG��֯��ע���룬1000���豸ϵ�кš�

STAR1000�豸��BDFҲ���Դ���ͼ���ҳ�������bus��0x3C��device��0x00��function��0x0��BDF��ʾΪ3C:00.0����֮��Ӧ�����ζ˿���00:1d.0��

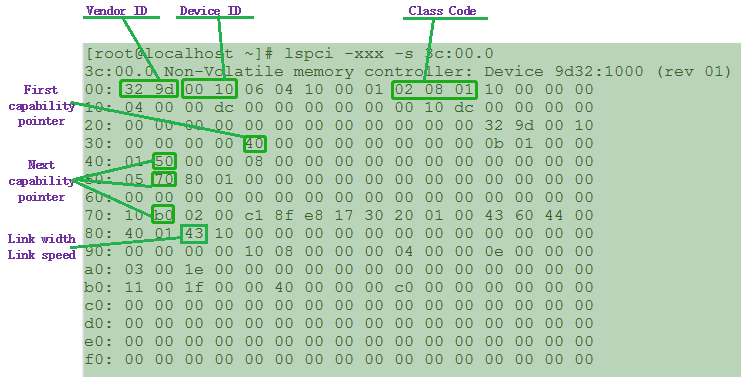

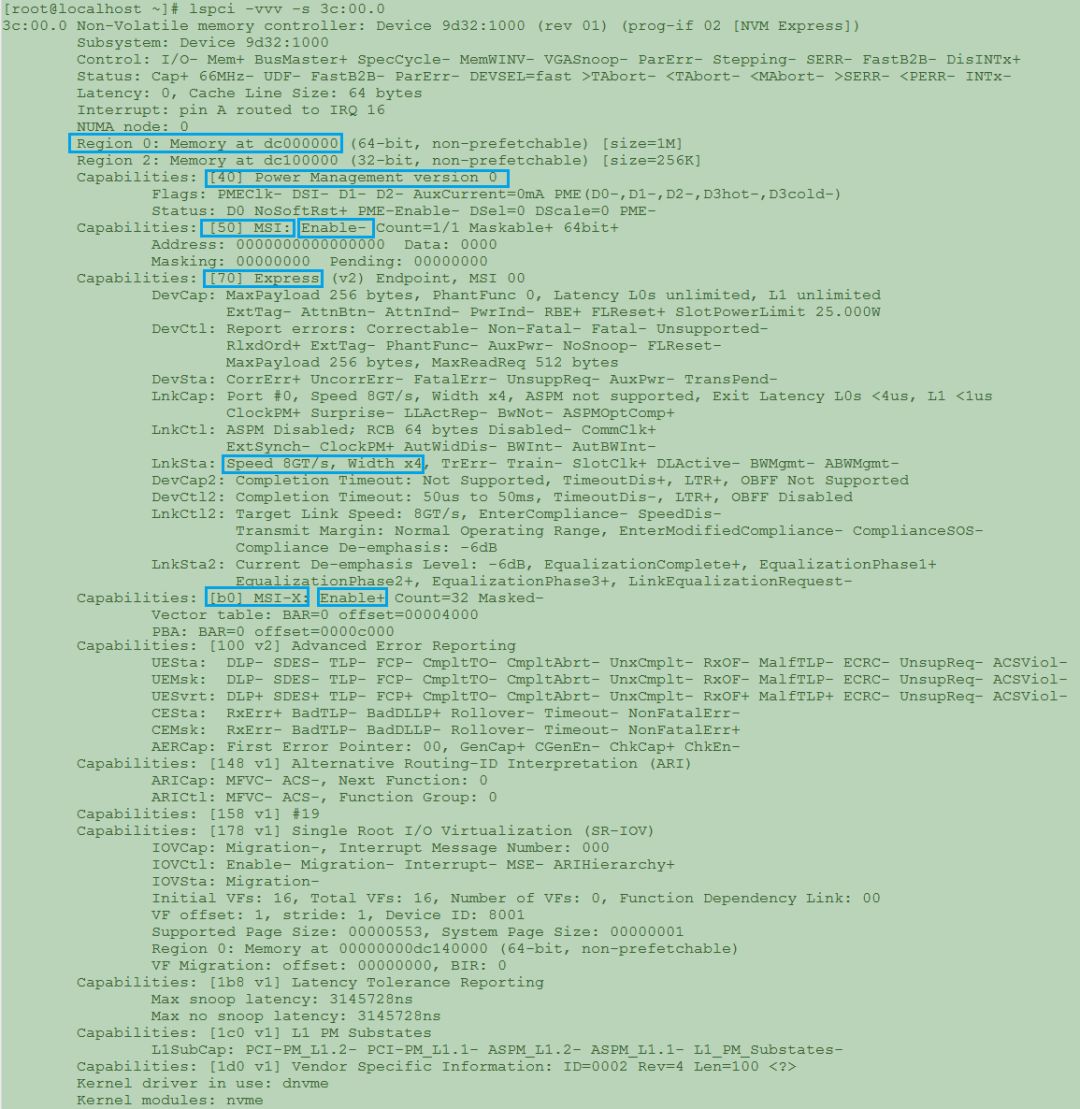

���ǿ���ͨ����lspci �Cxxx �Cs 3C:00.0���������г����豸��PCIe��ϸ��Ϣ(���������ѻ����ֿ����ע�ò���)����Щ���ݴ洢��PCIe���ÿռ䣬������������PCIe���������ԡ�����ͼ��ʾ(��λ��ַ0x00�������)�����Կ�������һ������ʧ�Դ洢��������0x00��ʼ��ַ��PCIe��Vendor ID��Device ID��Class code 0x010802��ʾ����һ��NVMe�洢�豸��0x40�ǵ�һ��capability��ָ�룬�������Ҫ�鿴PCIe�����ԣ�����Ҫ�����λ�ÿ�ʼȥ��ѯ����ÿ��������ͷ�ֶζ��������һ�����Ե���ʼ��ַ����0x40��ַ��ʼ������power management��MSI�жϣ���·������״̬��MSI-X�жϵ������顣����ر��г�����·�����е�һ��0x43�ֶΣ���ʾSTAR1000�豸��һ��x4lane�����ӣ�֧��PCIe Gen3���ʣ�8Gbps����

��ȻҲ����ʹ��lspci �Cvvv �Cs 3C:00.0�������鿴�豸���ԣ���ѧ�߿���������б�Ҳ��һĿ��Ȼ�ˡ�

Host��ö���豸��ͬʱҲ����豸�������ã�ÿ��PCIe�豸����ָ��һ��CPU memory���ʿռ䣬�������ͼ�����ǿ��Կ�������豸֧�����η��ʿռ䣬һ�εĴ�С��1M byte����һ�εĴ�С��256K byte��ϵͳ��ֱ�ָ�����ǵĻ���ַ������ַ��������Ժ�Host�Ϳ���ͨ����ַ����PCIe memory�ռ���з����ˡ�

PCIe memory�ռ��������PCIe�豸�������ܣ�����STAR1000ϵ��оƬ���ԣ�����������NVMe��memory�д�ŵ���NMVe�Ŀ�����״̬��Ϣ������NMVe�Ŀ����Լ�����״̬�Ļ�ȡ������Ҫͨ��memory������ʵ�֡�

������NVMe�����·�Ϊ��������PCIe�豸��memory���ʡ�NVMe�����·��Ļ���������1��Hostдdoorbell�Ĵ�������ʱʹ��PCIe memoryд��������ͼ��ʾ��host����һ��memory write(MWr)��������switch����Ҫ���ʵ�NVMe SSD�豸��

�������ᱻ�˵��豸���ղ�ִ��2)NVMe��ȡ�������������ͼ��ʾ����ʱNVMe SSD��Ϊ�����ߣ�����һ��memory read(MRd)��������Switch����Host��Host��Ϊ����᷵��һ����������(CplD)�������ʽ�����ظ�NVMe SSD��

������һ��NVMe�������·����̾�����ˡ�ͬ����NVMe����������������ֶ��в�������������ɣ����ݴ��䶼��ͨ��PCIe memory���ʵķ�ʽ���еģ��˴�����������

ͨ������������������ܹ���������˽�PCIe���豸ö�ٺ�memory�ռ���ʡ��Ժ���������̽��PCIe���������ݣ�����PCIe��Э��ֲ㣬��·���������Ĺ����ȵȡ�ĿǰPCIeЭ�黹���ڲ��ϵĿ����ݽ��У�2017�귢����PCIe Gen4����ÿ��Serdes֧�ֵ������Ѿ��ﵽ16Gbps��Gen5Ҳ�ڼ����ƶ��У������ʻ��ٷ�һ���ﵽ32Gbps��Starblaze����������ķ�չ���ƣ��ṩ���ʸ��ߣ����ܸ��ø��ȶ���NVMe SSDϵ�в�Ʒ��

���https://mp.weixin.qq.com/s/FlRc2q8r0fUOzxJFWulGfw