Ŀ¼

- ����RISC-V����ˮ�ߴ�����

- RISC-Vָ�

- RV32I

- R-Type

- I-Type

- J-Type

- B-Type

- Load & Store

- �ܽ�

- ���

����RISC-V����ˮ�ߴ�����

RISC-V��һ�����ھ���ָ�ԭ��Ŀ�Դָ��ܹ������ɼ��ݴ�ѧ��������У��David Patterson�����쵼�µ�С����ɣ������ѳ�ΪRISC��������һ��ǿ��������������

����github�����ж������Ļ���RISC-Vָ�����������Ŀ��������������E203��RocketChip�ȣ����������漰��֪ʶ�㼶�����ѧ�ߺ���Ѹ�����֡���CSDN��Ҳû���ҵ����Ƶ�RISC-V����������Ŀ����˱��߾������㿪ʼ���ɻ���ָ�����ʵ��һ�����RISC-Vָ�����������

RISC-Vָ�

ʵ��һ�����������Ҳ������Ҫ�ľ���Ҫȷ����������ָ��ܹ���

RISC-Vָ����Է�Ϊ���¼����Ӽ���

- RV32I��������������������������ָ�LOAD/STORE���Լ�����ָ�RV32Iӵ��32λѰַ�ռ䣬32��32λ�Ĵ�����

- RV32E��ָ����RV32I��ͬ�����ǼĴ���������Ϊ16��������Ƕ��ʽ������

- RV64I������ָ�ӵ��64λѰַ�ռ䣬32��64λ�Ĵ�����

- RV128I������ָ�ӵ��128λѰַ�ռ䣬32��128λ�Ĵ�����

�����Ӽ���RISC-V�Ļ���ָ�����ʵ������У����ǿ��Ը�����Ҫ�������µ���չָ���

- M�����˷��ͳ�����չ�������˳˷��ͳ�����ָ����ѽ�������������Ĵ�����

- A����ԭ��ָ����չ��������ԭ�ӵĶ����ģ��Լ�д�洢����ָ�

- F���������ȸ�����չ�������˸���Ĵ����������ȼ���ָ��Լ������ȵ�LOAD/STOREָ�

- D����˫���ȸ�����չ��ͬ�������˸���Ĵ�������������˫���ȼ���ָ�˫���ȵ�LOAD/STOREָ�

������ΪRISC-V�������֤����չָ��������V/P/T�ȴ��ڲݸ��Ľε���չָ�������Ͳ������ˡ�

RV32I

�ڱ�������У�����Ҫʵ�ֵ��ǻ��������������ָ�����RV32I�����������������Ǵ�RV32I�ľ���ָ���ʽ����

��ͼչʾ��RV32I�Ļ���ָ���ʽ��Ϊ�˼�������̣�Դ�Ĵ�����rs1 �� rs2����Ŀ��Ĵ�����rd����RISC-V ISA ������ָ���ʽ�е�λ�ñ���һ�¡���������ѹ����ָ��������ߵĿ���λ�����Ѿ�����ã��Ӷ�����Ӳ�����Ӷȡ��ر�ģ��������е���������ָ��� 31 λ���Ƿ���λ���������Լ��ٷ�����չ��·��

�������ǽ��Ը����͵�ָ����о���Ľ��͡�

R-Type

R-Type��ָ��Ϊ�Ĵ���-�Ĵ���ָ����ʽ����ͼ��ʾ��R-Typeָ����ص���2��Դ��������Ŀ������������ǼĴ�������ʵ��ִ�й�������Ҫ�����Ĵ�����д�ء�

| Instruction | Description | Format | Comment |

|---|---|---|---|

| ADD | ADD rd, rs1, rs2 | rd = rs1 + rs2�����������������32bit | |

| SUB | SUB rd, rs1, rs2 | rd = rs1 - rs2�����������������32bit | |

| AND | AND rd, rs1, rs2 | rd = rs1 & rs2����� | |

| OR | OR rd, rs1, rs2 | rd = rs1 | rs2����� | |

| XOR | XOR rd, rs1, rs2 | rd = rs1 ^ rs2�� ���� | |

| SLT | set less than | SLT rd, rs1, rs2 | if (rs1 < rs2) rd = 1 else rd = 0 |

| SLTU | set less than unsigned | SLTU rd, rs1, rs2 | if((unsigned)rs1 < (unsigned)rs2) rd = 1 else rd = 0 |

| SLL | shift left logical | SLL rd, rs1, rs2 | rd = rs1 << rs2 [4 : 0]�������ƣ���λ���㣬rs2��lower 5 bits��Ϊƫ���� |

| SRL | shift right logical | SRL rd, rs1, rs2 | rd = rs1 >> rs2 [4 : 0]�������ƣ���λ���㣬rs2��lower 5 bits��Ϊƫ���� |

| SRA | shift rignt arithmetric | SRA rd, rs1, rs2 | rd = rs1 >> rs2 [4 : 0]���������ƣ���λ������λ��rs2��lower 5 bits��Ϊƫ���� |

| NOP | no operation | NOP | �������κβ������൱��ADDI x0, x0, 0 |

I-Type

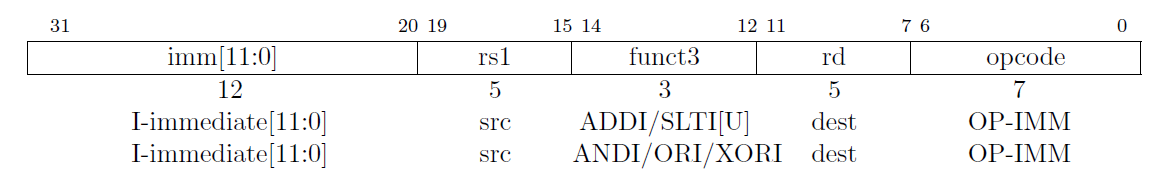

I-Type��ָ��Ϊ�Ĵ���-������ָ���ָ���ʽ����ͼ��ʾ��R-Typeָ����rs2��funct7��λ����I-Typeָ���б�imm�����ָ�����funct3��ȷ������ָ�����͡�

imm��һ��12λ��������������32λ�ļĴ�������������ʱ������з���λ��չ��

| Instruction | Description | Format | Comment |

|---|---|---|---|

| ADDI | add immediate | ADD rd, rs1, imm | rd = rs1 + (sign-extended) imm�����������������32bit |

| ANDI | and immediate | AND rd, rs1, imm | rd = rs1 & (sign-extended) imm����� |

| ORI | or immediate | OR rd, rs1, imm | rd = rs1 | (sign-extended) imm����� |

| XORI | xor immediate | XOR rd, rs1, imm | rd = rs1 ^ (sign-extended) imm�� ���� |

| SLTI | set less than immediate | SLT rd, rs1, imm | if (rs1 < (sign-extended) imm) rd = 1 else rd = 0 |

| SLTIU | set less than unsigned immediate | SLTU rd, rs1, imm | if((unsigned)rs1 < (unsigned)imm) rd = 1 else rd = 0 |

������λָ�ʹ���������ĵ�5λ��Ϊƫ��������7λҲ��Ϊ�жϾ���ָ��IJ����룬����ͼ��ʾ��

| Instruction | Description | Format | Comment |

|---|---|---|---|

| SLLI | shift left logical | SLL rd, rs1, imm | rd = rs1 << rs2 [4 : 0]�������ƣ���λ���� |

| SRLI | shift right logical | SRL rd, rs1, imm | rd = rs1 >> rs2 [4 : 0]�������ƣ���λ���� |

| SRAI | shift rignt arithmetric | SRA rd, rs1, imm | rd = rs1 >> rs2 [4 : 0]���������ƣ���λ������λ |

J-Type

J-Typeָ��Ϊ��������תָ���Ҫ�����Ǹ���PC��ָ���ַ���ô���������һ��ʱ����������ָ���ĵ�ַ��ȡָ�

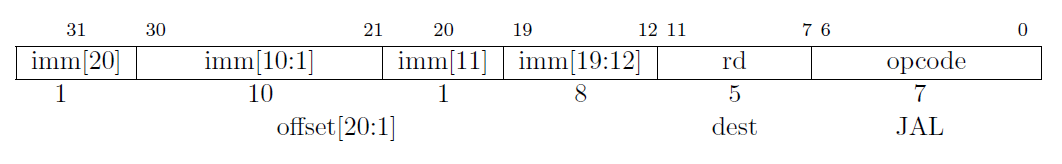

JAL��ָ���ʽ����ͼ��ʾ������JAL��ʹ��һ��20λ���з�����������Ϊƫ������Ŀ���ַΪpc + offset������ԭpc + 4�ĵ�ַ����rd��

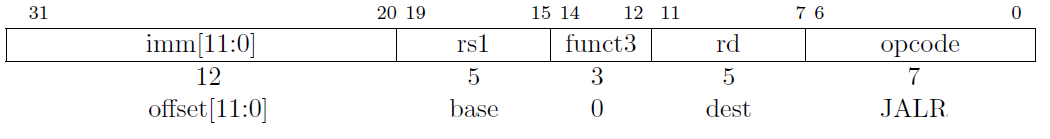

JALR��ָ���ʽ����ͼ��ʾ������JALR����ʹ�õ�ָ���ʽ��I-Type��ָ���ʽ��Ŀ���ַΪpc + offset���LSB��Ϊ0��Ľ��������ԭpc + 4�ĵ�ַ����rd��

�ɴˣ����ǿ���д���±���ָ�

| Instruction | Description | Format | Comment |

|---|---|---|---|

| JAL | jump and link | JAL rd, offset | pc += (sign-extended) offset, rd = pc + 4 |

| JALR | jump and link register | JALR rd, rs1, offset | pc = [rs + (sign-extended) offset] &~ 1, rd = pc + 4 |

| JR | jump register | JR rs1 | pc = rs1 |

B-Type

B-Typeָ��Ϊ������ָ֧�������������������½�����ת����ת��ƫ������һ��12λ����������������ָ���ʽ����ͼ��ʾ��

| Instruction | Description | Format | Comment |

|---|---|---|---|

| BEQ | branch equal | BEQ rs1, rs2, offset | if (rs1 == rs2) pc += (sign-extended) offset |

| BNE | branch not equal | BNE rs1, rs2, offset | if (rs1 != rs2) pc += (sign-extended) offset |

| BLT | branch less than | BLT rs1, rs2, offset | if (rs1 < rs2) pc += (sign-extended) offset |

| BGE | branch bigger than or equal | BGE rs1, rs2, offset | if (rs1 >= rs2) pc += (sign-extended) offset |

| BGEU | branch bigger than or equal unsigned | BGEU rs1, rs2, offset | if((unsigned) rs1 >= (unsigned) rs2) pc += (sign-extended) offset |

Load & Store

��RV32I�У�ֻ��Load & Storeָ��ӵ�з����ڴ��Ȩ�ޡ�RV32I�ṩ32-bit��Ѱַ�ռ䡣

��ͼչʾ��Load & Storeָ��ľ����ʽ������ע���LOADָ��ʹ�õ���I-Typeָ��ĸ�ʽ����STOREָ��ʹ�õ���S-Typeָ��ĸ�ʽ��

Loadָ���Storeָ���Ŀ���ַ��rs1 + ����λ��չ��ƫ������������ָ��ΪLH/LBʱ�����ڴ��ָ����ַ��ȡ��16λ/��8λ�����з���λ��չ�����rd������ָ��ΪLWʱ��ֱ�Ӵ��ڴ���ȡ4�ֽڵ����ݴ���rd��

| Instruction | Description | Format | Comment |

|---|---|---|---|

| LW | load word | LW rd, rs1, offset | rd = mem[rs1 + (sign-extended) offset] [31:0] |

| LH | load half | LH rd, rs1, offset | rd = (sign-extended) mem[rs1 + (sign-extend) offset)] [15:0] |

| LB | load byte | LB rd, rs1, offset | rd = (sign-extended) mem[rs1 + (sign-extend) offset)] [7:0] |

| LBU | load byte unsigned | LBU rd, rs1, offset | rd = (zero-extended) mem[rs1 + (sign-extend) offset)] [7:0] |

| SW | store word | SW rs1, rs2, offset | mem[rs1 + (sign-extend) offset)] = rs2 |

�ܽ�

���ˣ�RV32I�л���ָ���˵����һ���䡣

Ȼ������Щ˵��������������RV32I�л���FENCEָ�Environment Call and Breakpointsָ�HINTָ�����δ�ἰ����Щָ����ڱ��ε������˵���ڸ��ӣ����ڱ������ɵĴ��������������������㼰�洢���ܣ����������ͽ�����Щָ���������ȥ�ˡ�����Ȥ�Ķ��߿���ͨ�������������RISC-V�������ֲᣬ����������Ӣ��ԭ���ֲᣬ������������Ķ���

���

RISC-V��Ϊһ�����˵�RISC�ܹ����ھ����ʵ���в����ڳ������������˶���������RISC�ܹ��ġ�ȡ�侫����ȥ�����ɡ������磬RISC-Vȡ����MIPS-32 ISA�е��ӳٷ�֧�����������ִ��Ѿ��൱�����Ӳ��Ԥ����Ԥ���֧�����ʵ���˼ܹ��;���ʵ�ֵķ��룬ʹ��ָ���оƬ����ʵ�ֵķ����Ϊ���ܡ�

оƬ�̿��Բ���ͳһ�ġ���ѵĿ���ָ������������̿����и��Ե��ڲ�ģ��ʵ�֣�����������ר�����Ա����������ȿ��Թ���ͬһ��������̬ϵͳ���ֱ�����оƬ��ҵ֮��Ķ����ԡ�

���ڱ��߶��ԣ�RISC-V��MIPS����������ָ���и�Ԫ��λ�õı仯���������侫����Ƶġ��Ƶ������ŵľ���ָ��ܹ���ǿ��Ŀ���չ�ԡ�RV32I����rs1��rd֮�����һ��3 bit��funct����I-Type��ָ����ʹ��12λ����16λ�������������Ҳ�Ǵӿ���չ�ԵĽǶȿ��ǵ����Ľ����

����ͬ����Ϊһ��RISC-V�ij�ѧ�ߣ�����ָ��������������©�����ĵط�����ӭ��ҶԱ��ߵ����½�������ָ����Ҳ��ӭ�������߽��н�����