PS2总结

- 概述

- 工作原理

- 通信时序

概述

PS/2是在较早电脑上常见的接口之一,不支持热插拔。在Windows环境下,ps/2鼠标的采样率默认为60次/秒,USB鼠标的采样率为120次/秒。较高的采样率理论上可以提高鼠标的移动精度。

工作原理

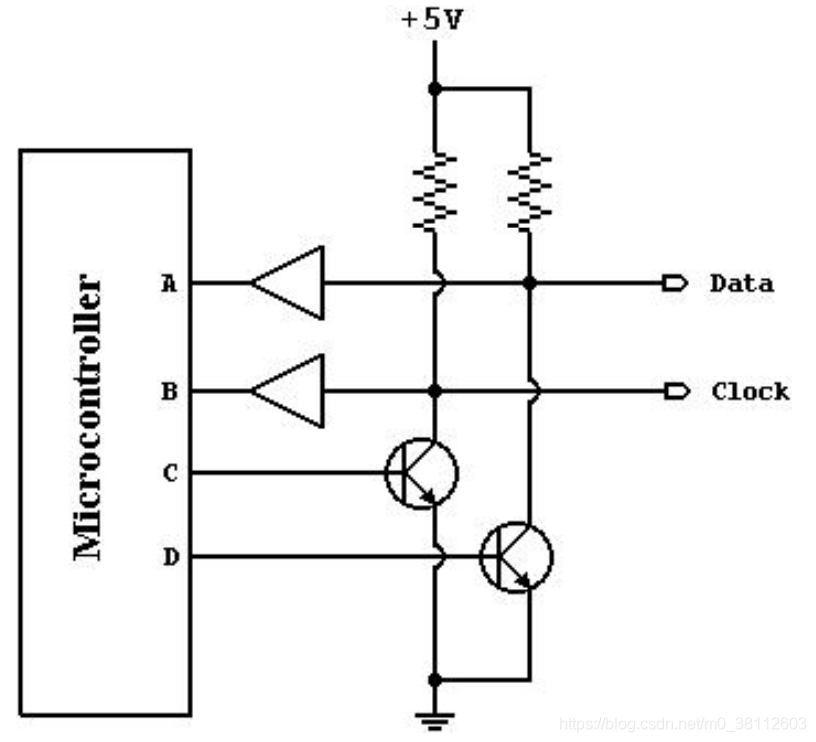

数据和时钟都是集电极开路的,这就意味着它们通常保持高电平而且很容易下拉到地 逻辑 0。 任何你连接到 PS/2 鼠标、键盘或 host 的设备在时钟和数据线上要有一个大的上拉电阻。置 0 就把线拉低 置 1 就让线上浮成高电平。图中数据和时钟线的一般接口结构。(注意如果你打算使用象 PIC 这样的微控制器, 由于它们的 I/O 管脚是双向的,你可以跳过晶体管和缓冲门,并且通用同一个管脚进行输入和输出。在这种组态情况下,要设置管脚为输入就写入 1 使得电阻上拉线上的电平,要改变管脚为输出就写入 0 到那个管脚,把线路下拉到地。)

图 1 数据线和时钟线的集电极开路接口。数据和时钟分别由微控制器的 A 端口和 B端口读入。这两条线通常保持+5V,但可以往端口 C 和 D 写入1 来拉到地。结果是数据是 D 的反相,时钟是 C 的反相。

图 1 数据线和时钟线的集电极开路接口。数据和时钟分别由微控制器的 A 端口和 B端口读入。这两条线通常保持+5V,但可以往端口 C 和 D 写入1 来拉到地。结果是数据是 D 的反相,时钟是 C 的反相。

PS/2 鼠标和键盘履行一种双向同步串行协议。换句话说,每次数据线上发送一位数据并且每在时钟线发一个脉冲就被读入。键盘/鼠标可以发送数据到主机,而主机也可以发送数据到设备,但主机总是在总线上有优先权,它可以在任何时候抑制来自于键盘/鼠标的通讯,只要把时钟拉低即可。

从键盘/鼠标发送到主机的数据在时钟信号的下降沿(当时钟从高变到低的时候)被读取 ;从主机发送到键盘/鼠标的数据在上升沿(当时钟从低变到高的时候)被读取。不管通讯的方向怎样,键盘/鼠标总是产生时钟信号。如果主机要发送数据,它必须首先告诉设备开始产生时钟信号(这个过程在下一章节中被描述)。最大的时钟频率是 33kHz, 而且大多数设备工作在 10~20kHz 。如果你要制作一个 PS/2 设备, 我推荐你把频率控制在 15kHz 左右。 这就意味着时钟应该是高 40 微秒低 40 微秒。

通信时序

协议格式

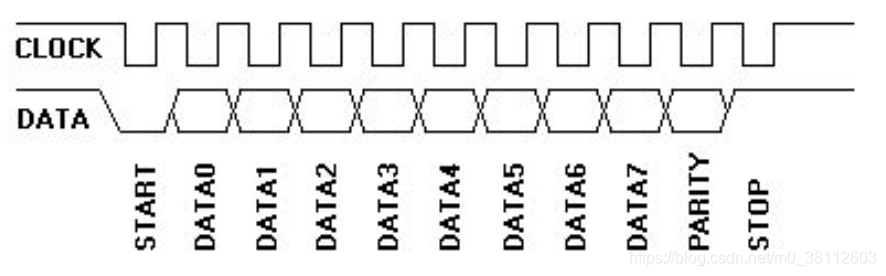

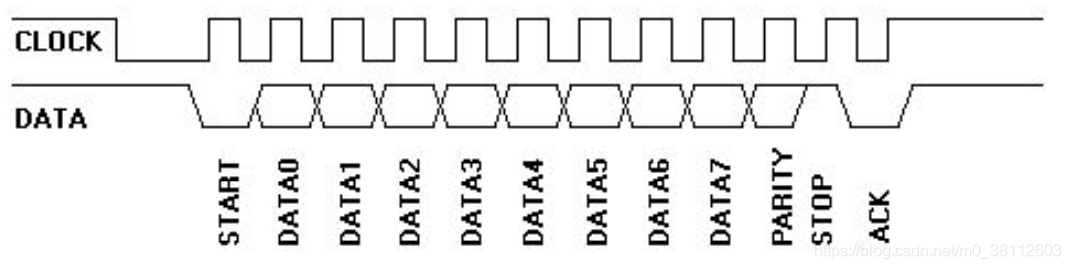

所有数据安排在字节中, 每个字节为一帧 ,包含了 11~12 个位。这些位的含义如下:

| 起始位 | 数据位 | 校验位 | 停止位 | 应答位 |

|---|---|---|---|---|

| 1 bit | 8bit | 1bit | 1bit | 1bit |

| 0 | LSB | 奇校验 | 1 | 仅在主机对设备的通讯中 |

如果数据位中包含偶数个 1, 校验位就会置 1; 如果数据位中包含奇数个 1 ,校验位就会置 0 。数据位中1 的个数加上校验位总是为奇数 (这就是奇校验 )。这是用来进行错误检测的。

当主机发送数据给键盘/鼠标时, 设备回送一个握手信号来应答数据包已经收到。 这个位不会出现在设

备发送数据到主机的过程中。

设备到主机

数据和时钟线都是集电极开路结构(正常保持高电平)当键盘或鼠标等待发送数据时, 它首先检查时钟以确认它是否是高电平。 如果不是, 那么是主机抑制了通讯, 设备必须缓冲任何要发送的数据直到重新获得总线的控制权(键盘有 16 字节的缓冲区 ,而鼠标的缓冲区仅存储最后一个要发送的数据包)。 如果时钟线是高电平, 设备就可以开始传送数据。每位在时钟的下降沿被主机读入。

设备到主机的通讯 当时钟为高 数据线改变状态 在时钟信号的下降沿数据被锁存

设备到主机的通讯 当时钟为高 数据线改变状态 在时钟信号的下降沿数据被锁存

我推荐下面的过程发送一个单一字节从仿真键盘/鼠标到主机:

- 等待 Clock = high

- 延时 50 微秒

- Clock s 仍旧为 high? No―到第 1 步

- Data = high? No―放弃 (并且从主机读取字节)

- 延迟 20 毫秒 (=40 微秒 to the time Clock is pulled low in sending the start bit.)

- 输出起始位 (0)

- 输出 8 个数据位

- 输出校验位

- 输出停止位 (1)

- 延迟 30 毫秒 (=50 微秒 from the time Clock is released in sending the stop bit)

按如下的过程发送单个位:

- 设置/复位数据

- 延迟 20 微秒

- 把时钟拉低

- 延迟 40 微秒

- 释放时钟

- 延迟 20 微秒

主机到设备

首先 PS/2 设备总是产生时钟信号 。如果主机要发送数据, 它必须首先把时钟和数据线设置为“请求发送“”状态,如下示:

- 通过下拉时钟线至少 100 微秒来抑制通讯。

- 通过下拉数据线来应用“请求发送”,然后释放时钟

设备应该在不超过 10 毫秒的间隔内就要检查这个状态。 当设备检测到这个状态, 它将开始产生时钟信号, 并且时钟脉冲标记下输入八个数据位和一个停止位 。主机仅当时钟线为低的时候改变数据线, 而数据在时钟脉冲的上升沿被锁存。 当发生在设备到主机通讯的过程中时正好相反。

在停止位发送后 ,设备要应答接收到的字节, 就把数据线拉低并产生最后一个时钟脉冲 。如果主机在第11 个时钟脉冲后不释放数据线, 设备将继续产生时钟脉冲直到数据线被释放(然后设备将产生一个错误)。

主机可以在第 11 个时钟脉冲(应答位)前中止一次传送, 只要下拉时钟线至少 100 微秒。

要使得这个过程易于理解 ,主机必须按下面的步骤发送数据到 PS/2 设备:

- 把时钟线拉低至少 100 微秒

- 把数据线拉低

- 释放数据线

- 等待设备把时钟线拉低

- 发送第一个数据位

- 等待设备把时钟拉高

- 等待设备把时钟拉低

- 重复 5-7 步 发送剩下的 7 个数据位和校验位

- 释放数据线

- 等待设备把数据线拉低

- 等待设备把时钟线拉低

- 等待设备释放数据线和时钟线

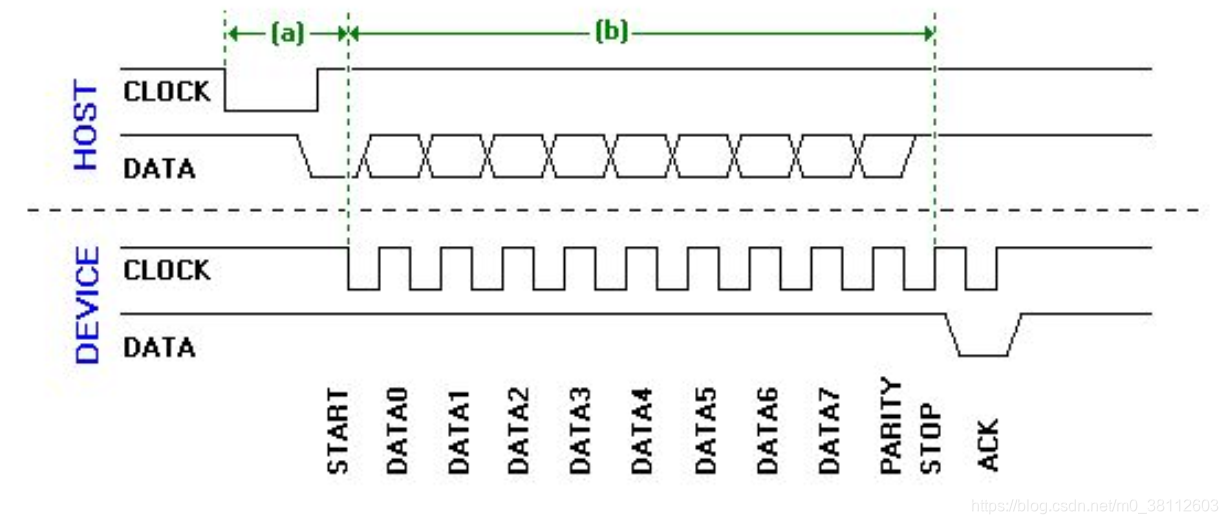

单独的时序表示了由主机产生的信号及由 PS/2 设备产生的信号。注意应答位时序的改变 ― 数据的改变发生在时钟线为高的时候 不同于其它 11 位是当它为低的时候。

上图描述了两个重要的定时条件:a 和 b。 a 在主机最初把数据线拉低后 ,设备开始产生时钟脉冲的时间 ,必须不大于 15ms, b 数据包被发送的时间必须不大于 2ms。 如果这两个条件不满足 ,主机将产生一个错误。 在包收到后 ,主机为了处理数据立刻把时钟线拉低来抑制通讯。 如果主机发送的命令要求有一个回应, 这个回应必须在主机释放时钟线后 20ms 之内被收到 。如果没有收到 ,则主机产生一个错误 。在设备到主机通讯的情况中, 时钟改变后的 5 微秒内不应该发生数据改变的情况。

上图描述了两个重要的定时条件:a 和 b。 a 在主机最初把数据线拉低后 ,设备开始产生时钟脉冲的时间 ,必须不大于 15ms, b 数据包被发送的时间必须不大于 2ms。 如果这两个条件不满足 ,主机将产生一个错误。 在包收到后 ,主机为了处理数据立刻把时钟线拉低来抑制通讯。 如果主机发送的命令要求有一个回应, 这个回应必须在主机释放时钟线后 20ms 之内被收到 。如果没有收到 ,则主机产生一个错误 。在设备到主机通讯的情况中, 时钟改变后的 5 微秒内不应该发生数据改变的情况。

如果你要仿真一个鼠标或键盘 ,我推荐你按如下的过程从主机读入数据:

在你的主程序中, 至少每 10 毫秒检测数据线是否为低。如果数据线已被主机拉低, 则从主机读取一个字节。

- 等待时钟线为高

- 数据线仍然为低吗?不,有错误发生;放弃

- 读入 8 个数据位

- 读入校验位

- 读入停止位

- 数据线仍旧为 0 吗?是―保持时钟直到数据 1,然后产生一个错误

- 输出应答位

- 检查校验位,如果校验位不正确则产生一个错误

- 延迟 45 微秒 ,给主机时间抑制下次的传送

按如下次序读取每位 8 个数据位 检验位和停止位:

- 延迟 20 微秒

- 把时钟拉低

- 延迟 40 微秒

- 释放时钟

- 延迟 20 微秒

- 读数据线

按如下次序发送应答位:

- 延迟 15 微秒

- 把数据线拉低

- 延迟 5 微秒

- 把时钟线拉低

- 延迟 40 微秒

- 释放时钟线

- 延迟 5 微秒