概述

随着宽带数据业务的飞速普及,数据产品的端口速率及端口密度也大大提升,于是以太网的MAC与PHY层之间的媒介无关接口(MII)也在不断简化,推陈出新,多种多样,基于此,本文简要介绍了以太网的PHY与MAC层之间的各种接口特征,包括RMII、SMII、SSMII、S3MII、GMII、RGMII、SGMII、TBI、RTBI等多种以太网接口。

MII

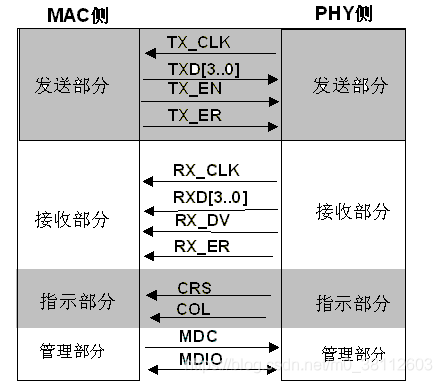

MII接口兼容10/100M以太网,由于占用管脚数太多,主要应用早期的设备接口中,在一般的高密度(8口)端口PHY以及MAC/switch 芯片中已经很少使用。

MII接口用4根数据线来传送数据,在传送100M数据时,时钟为25M,而在传送10M数据时,时钟降低到2.5M,这样实现了10M/100M的兼容。

| 信号 | I/O(以MAC侧为主) | 描述 | 备注 |

|---|---|---|---|

| TX_CLK | I | 发送时钟,100Mbps时为25MHz,10Mbps时为2.5MHz | |

| TX_ER | O | 发送错误,指示发送的数据是错误的phy可以将其丢弃 | |

| TX_EN | O | 发送使能,表示当该信号有效时发送的数据是有效的 | |

| TX_D[3:0] | O | 发送数据 | |

| RX_CLK | I | 接收时钟,100Mbps时为25MHz,10Mbps时为2.5MHz | |

| RX_ER | I | 接收错误,指示发送的数据是错误的phy可以将其丢弃 | |

| RX_DV | I | 接收数据有效 | |

| RXD[3:0] | I | 接收数据 | |

| CRS | I | 载体检测, 未处于IDEL状态则为高电平 | |

| COL | I | 冲突检测,检测到冲突时,COL被断言为高 |

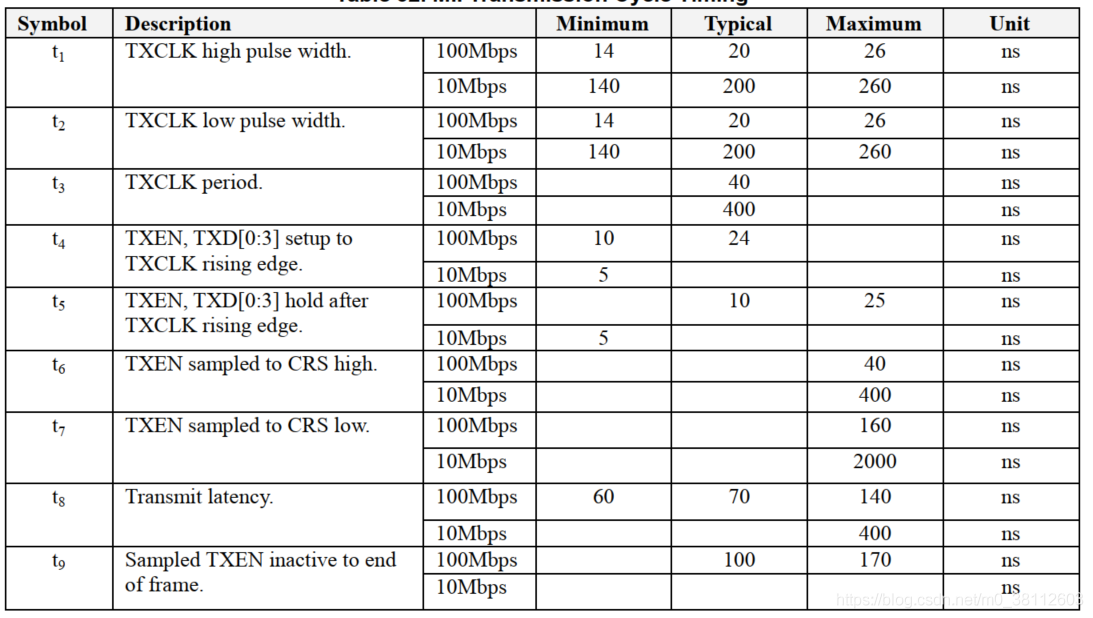

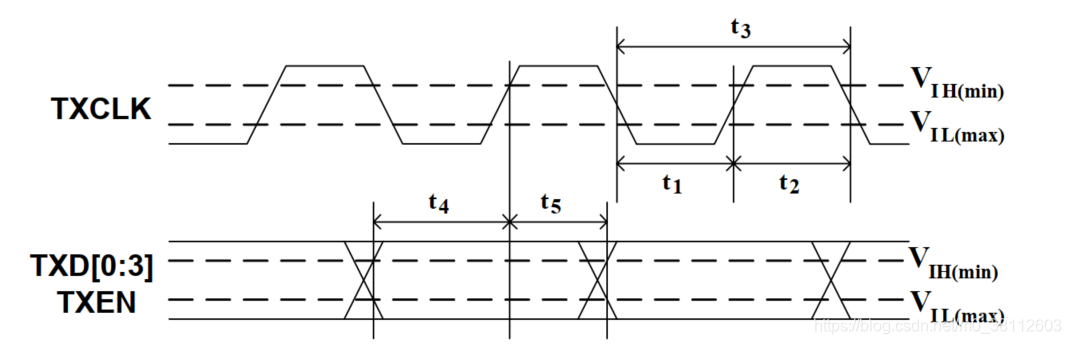

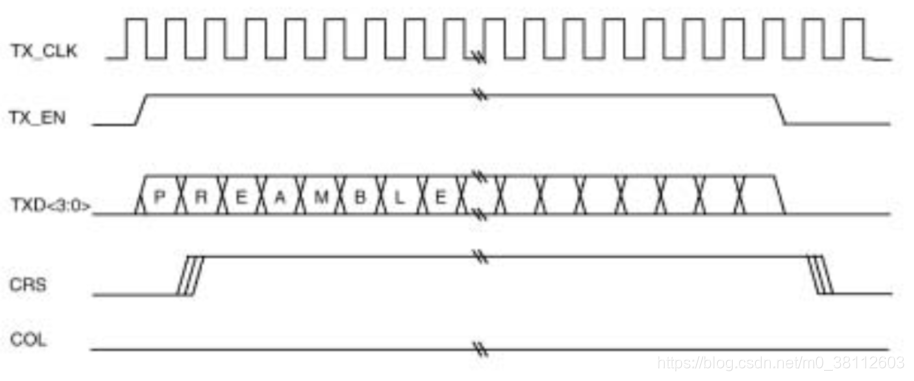

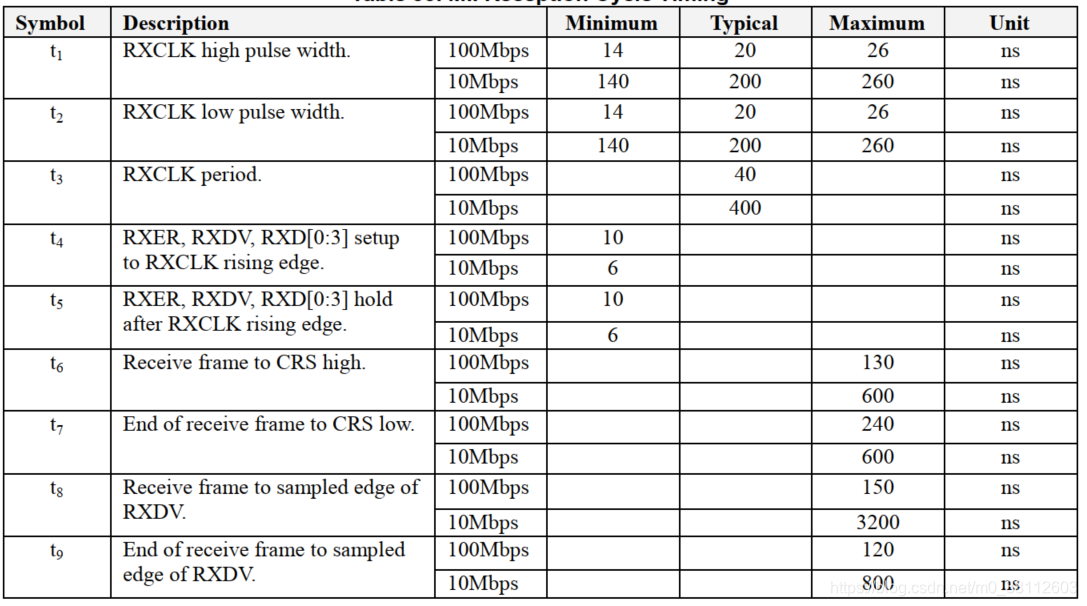

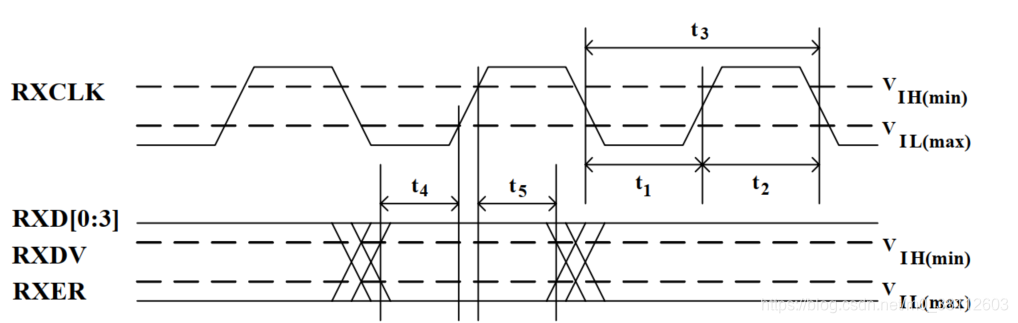

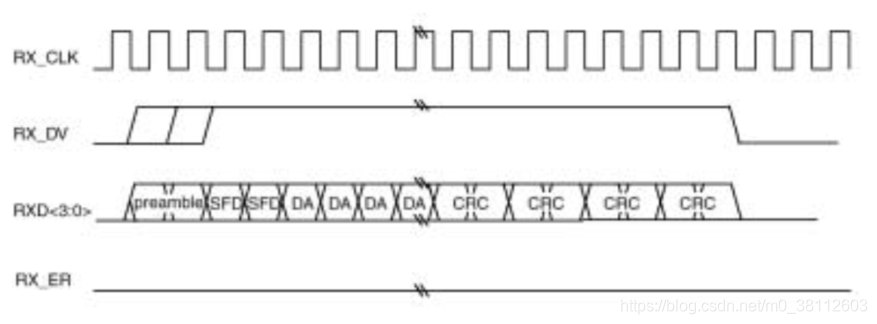

MII时序关系如下所示在:

- 发送

- 接收

注:以上时序图均为参考RTL8201芯片资料

注:以上时序图均为参考RTL8201芯片资料

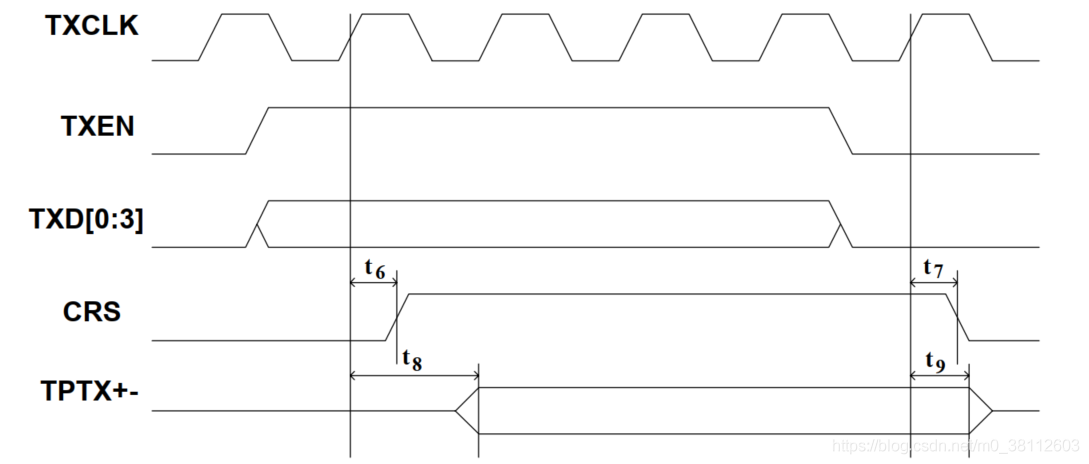

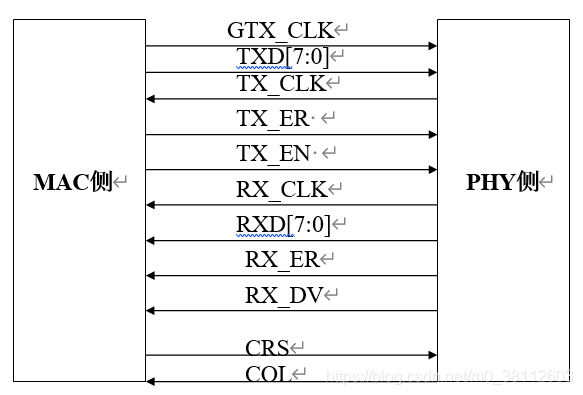

GMII

GMII(Gigabit MII)GMII接口都可以向下兼容MII 接口,数据位宽8bit,共使用了24个管脚,类似于FE接口中的MII,在高密器件中一般不会使用。GMII接口是1000M速率接口。

| 信号 | I/O(以MAC侧为主) | 描述 | 备注 |

|---|---|---|---|

| GTX_CLK | O | GMII接口发送时钟,125MHz,同步发送数据与控制信号,MII不使用 | 可选 |

| TX_CLK | I | 发送时钟,MII为25MHz,10M MII为2.5MHz,GMII不使用 | 可选 |

| TX_ER | O | 发送错误,指示发送的数据是错误的phy可以将其丢弃 | |

| TX_EN | O | 发送使能,表示当该信号有效时发送的数据是有效的 | |

| TX_D[7:0] | O | 发送数据,MII只使用[3:0] | |

| RX_CLK | I | 接收时钟,GMII为125MHz,FE MII为25MHz,10M MII为2.5MHz | |

| RX_ER | I | 接收错误,指示发送的数据是错误的phy可以将其丢弃 | |

| RX_DV | I | 接收数据有效 | |

| RXD[7:0] | I | 接收数据,MII只使用[3:0] | |

| CRS | I | 载体检测, 未处于IDEL状态则为高电平 | |

| COL | I | 冲突检测,检测到冲突时,COL被断言为高 |

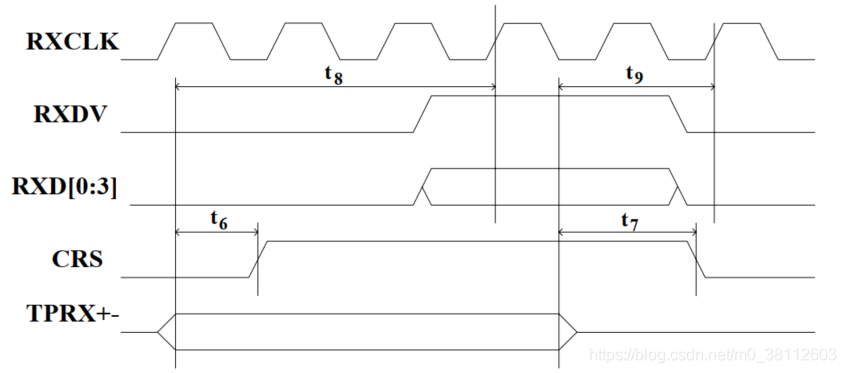

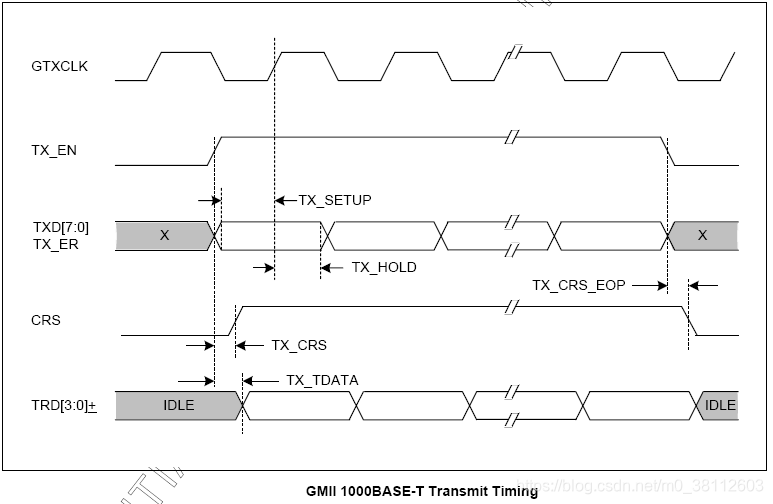

注:以上时序图均为参考BCM5464芯片资料

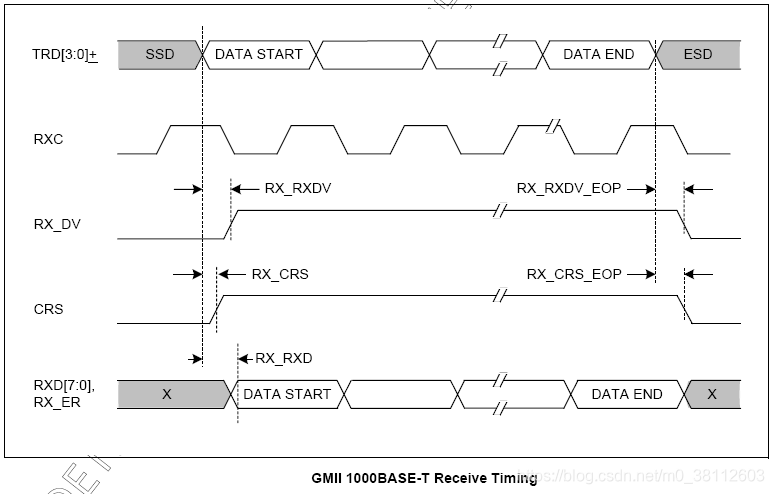

注:以上时序图均为参考BCM5464芯片资料