以太网详解(一)-MAC/PHY/MII/RMII/GMII/RGMII基本介绍-转载

sternlycore

2019-04-07 21:16:25

13881

13881

收藏

163

收藏

163

13881

13881

收藏

163

收藏

163

分类专栏:硬件接口

</div></div><div class="up-time" style="left: 121.828px; display: none;"><span>最后发布:2019-04-07 21:16:25</span><span>首发:2019-04-07 21:16:25</span></div><div class="slide-content-box"><div class="all-tags-box"></div><div class="article-copyright"><div class="creativecommons"><a rel="license" href="http://creativecommons.org/licenses/by-sa/4.0/"></a></div><div class="creativecommons">版权声明:本文为博主原创文章,遵循<a href="http://creativecommons.org/licenses/by-sa/4.0/" target="_blank" rel="noopener"> CC 4.0 BY-SA </a>版权协议,转载请附上原文出处链接和本声明。 </div><div class="article-source-link">本文链接:<a href="https://blog.csdn.net/sternlycore/article/details/89065789">https://blog.csdn.net/sternlycore/article/details/89065789</a></div></div></div><div class="operating"><a class="href-article-edit slide-toggle">版权</a></div></div></div>

</div>

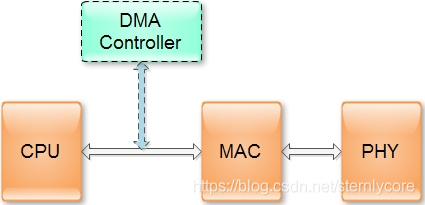

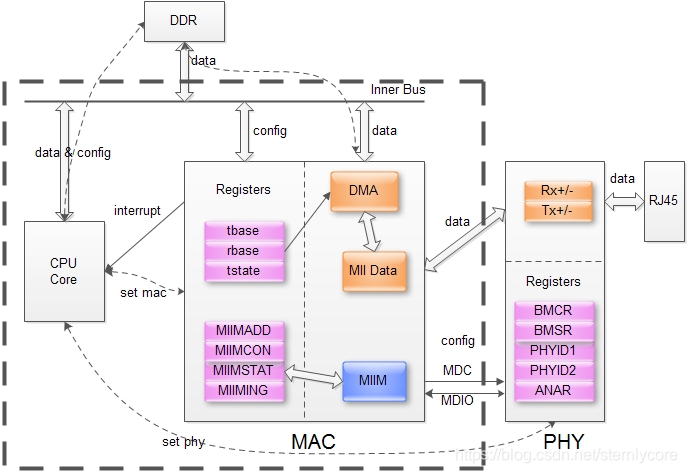

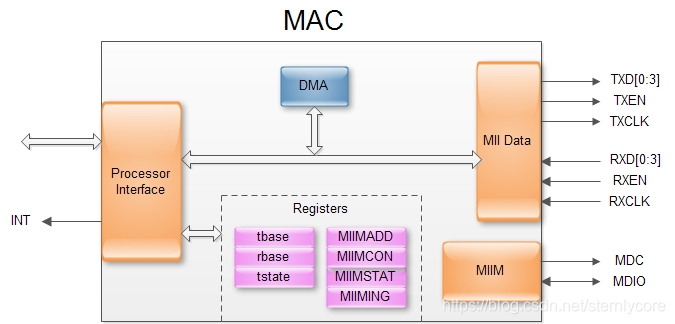

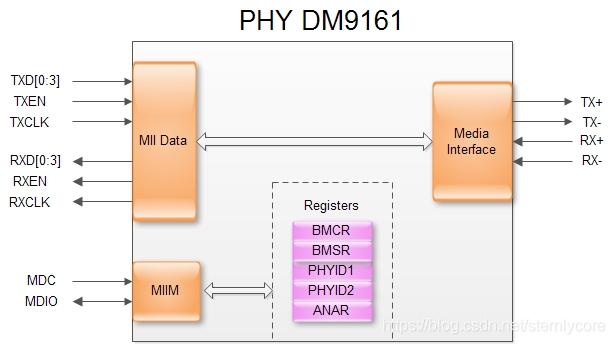

<!--python安装手册结束--><article class="baidu_pl"><div id="article_content" class="article_content clearfix"><link rel="stylesheet" href="https://csdnimg.cn/release/phoenix/template/css/ck_htmledit_views-211130ba7a.css"><div id="content_views" class="markdown_views prism-atom-one-light"><!-- flowchart 箭头图标 勿删 --><svg xmlns="http://www.w3.org/2000/svg" style="display: none;"><path stroke-linecap="round" d="M5,0 0,2.5 5,5z" id="raphael-marker-block" style="-webkit-tap-highlight-color: rgba(0, 0, 0, 0);"></path></svg><p>网络设备中肯定离开不MAC和PHY,本篇文章将详细介绍下以太网中一些常见术语与接口。</p>