基于RISC架构的32位CPU,经典5级流水线

AZ Processor框架图:

(1)组成部分:IF阶段、ID阶段、EX阶段、MEM阶段、cpu通用寄存器(gpr)、CPU控制单元、CPU直接访问的专用存储器SPM。

虚线中的WB阶段,实际在结果写回通用寄存器或CPU控制单元实现,本身这个模块并不存在。

(2)IF阶段和MEM阶段通过总线与内存和I/O相连。需要每个周期都向流水线提供指令或数据。因此设置了可以高速访问的CPU专用SPM。SPM与缓存类似,但分配有地址空间的存储器。

(3)分支的判定在ID阶段进行。采用延迟分支机制,分支的下条指令被作为延迟间隙执行,以规避控制冒险。EX和MEM阶段的处理结果可以直通到ID阶段,一次规避数据冒险。

(4)寄存器停滞与刷新和流水线的控制等操作由控制单元负责。控制单元还可以接收来自外部信号的中断请求,中断检测是在EX阶段进行的。

///

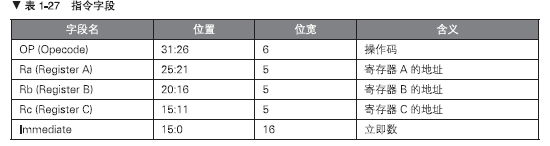

AZ Processor 的指令集架构