本篇文章对Vivado HLS以及OpenCV HLS进行简要介绍,并且利用OpenCV HLS的函数,hls::Sobel,编写边缘检测算法,仿真测试,创建IP,最后在vivado里测试Sobel IP

关于HLS详细内容请参考官方文献ug902-vivado-high-level-synthesis

*本文主要参考文献:

how_to_accelerate_opencv_applications_using_vivado_hls

xapp890-zynq-sobel-vivado-hls*

*本文所使用的开发板是Miz702(兼容zedboard)

PC 开发环境版本:Vivado 2015.2 Xilinx SDK 2015.2*

需要准备HDMI显示器和串口线一条

HLS简介

HLS(High Level Synthesis)即高层次综合,不同于以往的FPGA逻辑开发,是用HDL编写的,开发周期长、难度大。而HLS可以使用C,C++,SystemC以及OPenCL等编写,通过高层次综合,可以把软件代码转化为硬件描述语言,可以大大加快开发速度,使软件工程师也可以编写硬件语言。

HLS OpenCV简介

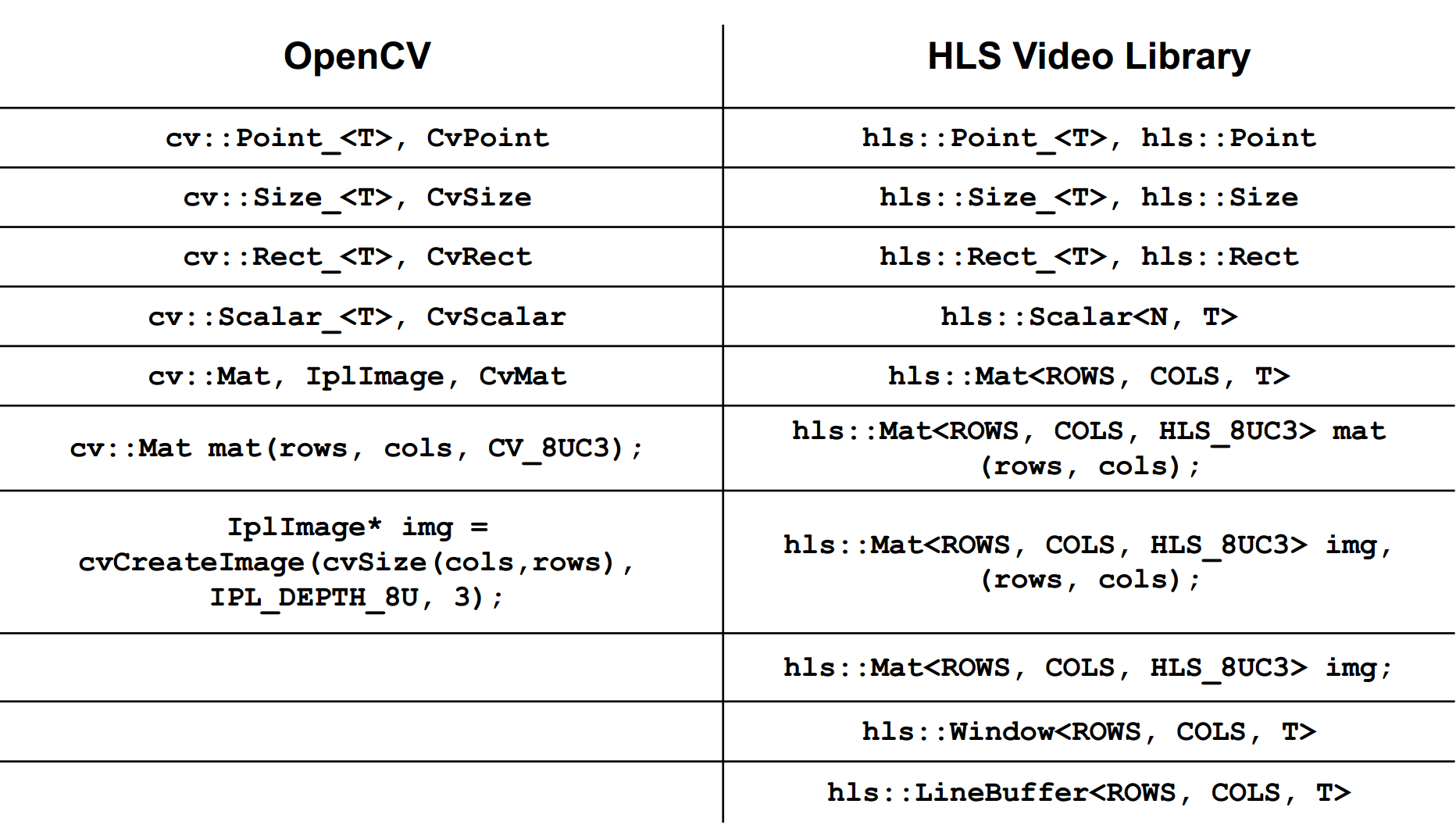

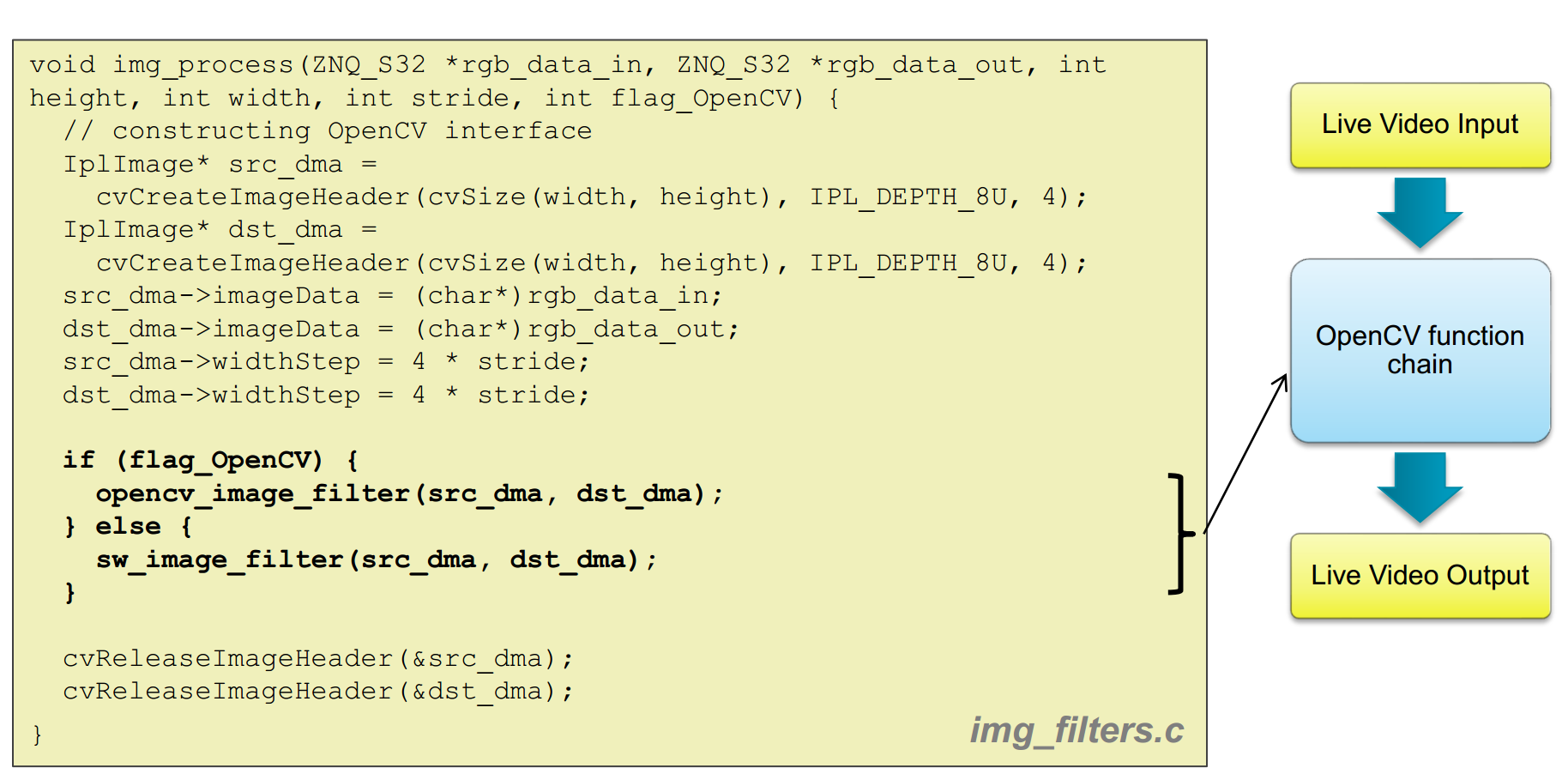

OpenCV是开源的图像处理和计算机视觉库,它支持多种操作系统、包含多种计算机语言的接口。HLS Opencv是HLS里带有的可综合成HDL的OpenCV库函数,换句话说,由于HDL和C++的特性(例如动态内存分配不可以综合成HDL)并不是所有的OpenCV库函数都可以综合成HDL,当然目前Xilinx提供了较多的HLS OpenCV库函数,可以满足一定的需求,相信以后会越来越多的。

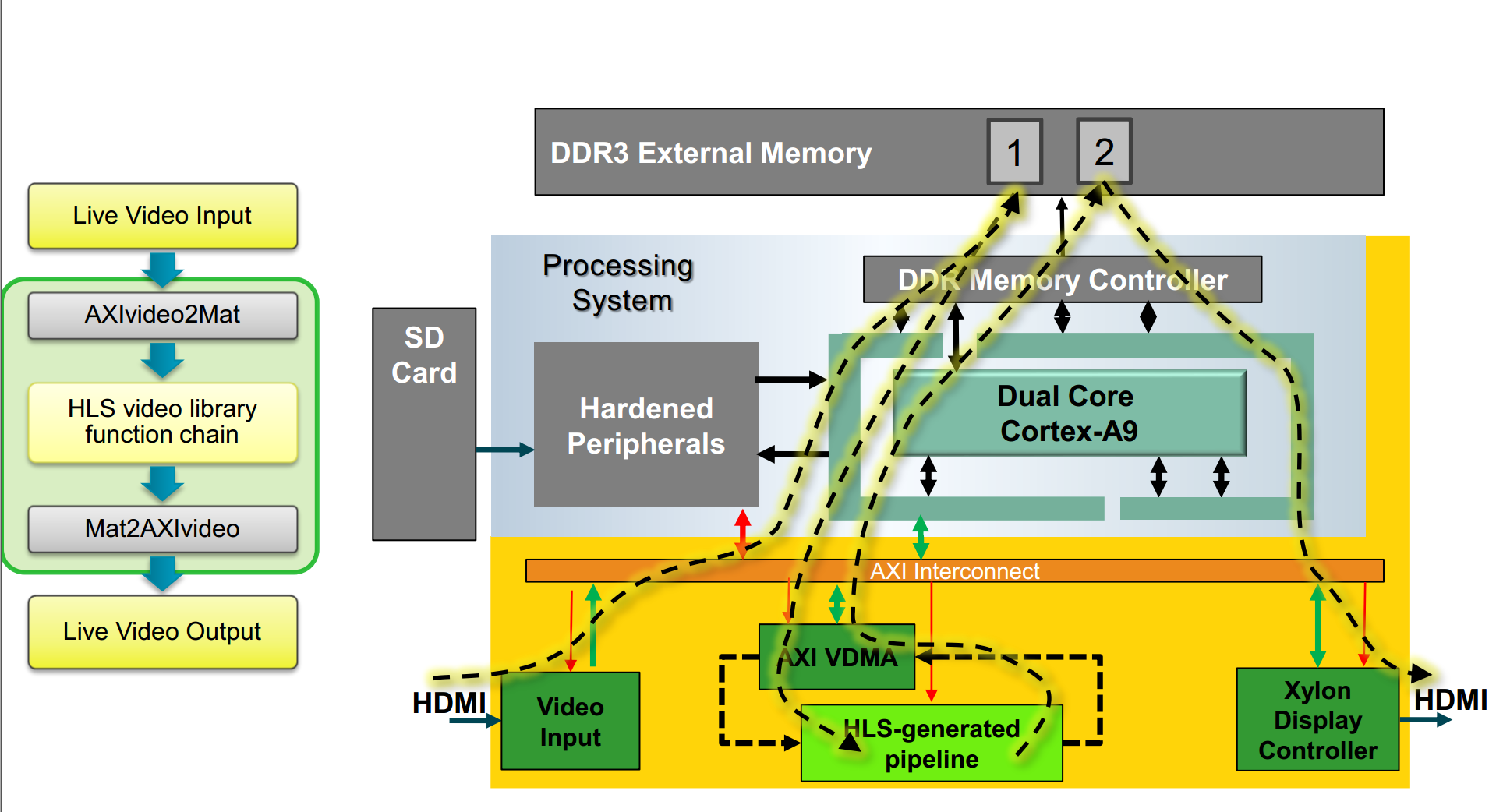

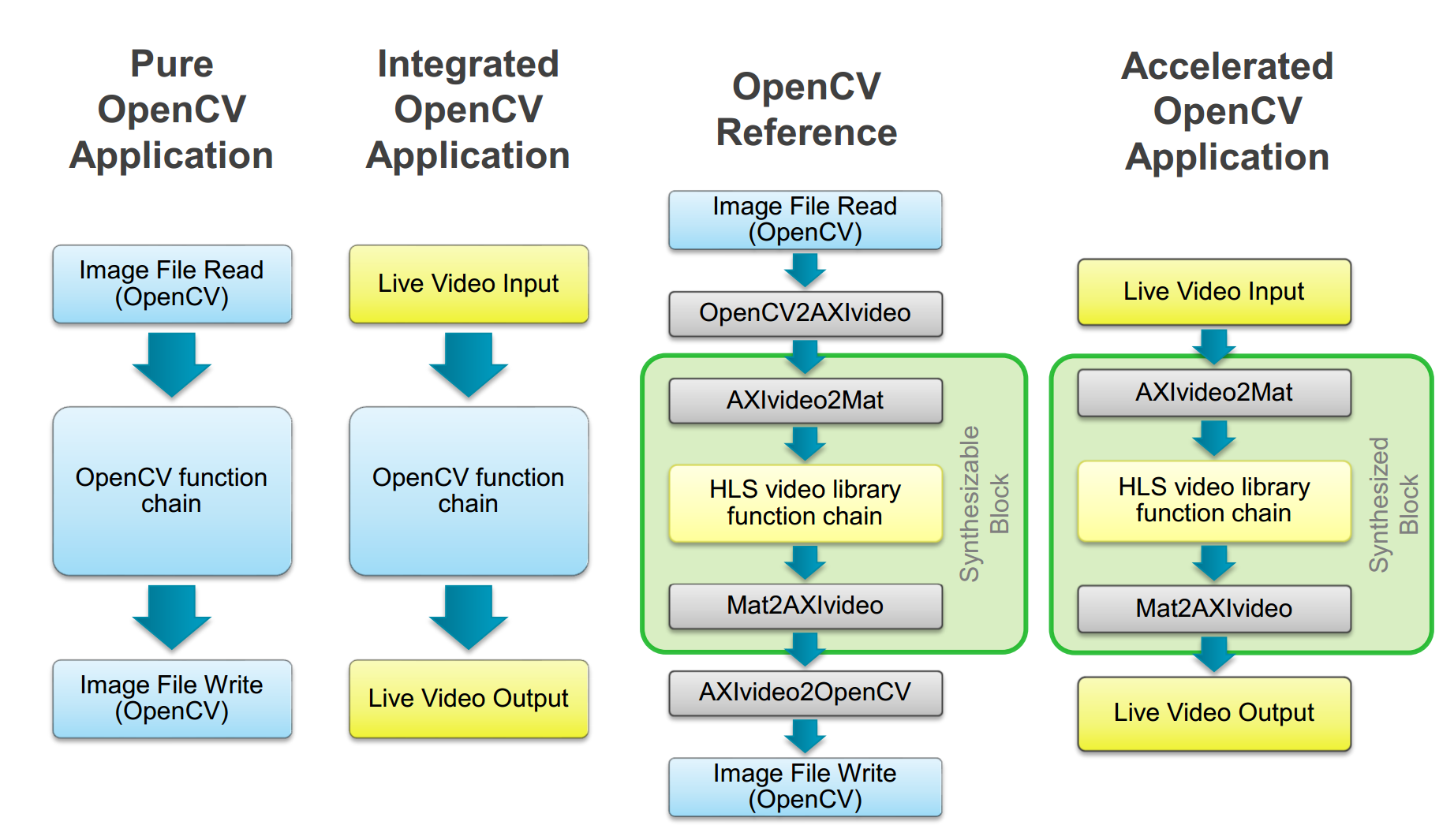

HLS加速模型

HLS OpenCV和OpenCV有着相似的书写风格

OpenCV library : cvScale(src, dst, scale, shift);

HLS video library : hls::Scale<…>(src, dst, scale, shift);

可综合的代码可以在ARM上直接运行!

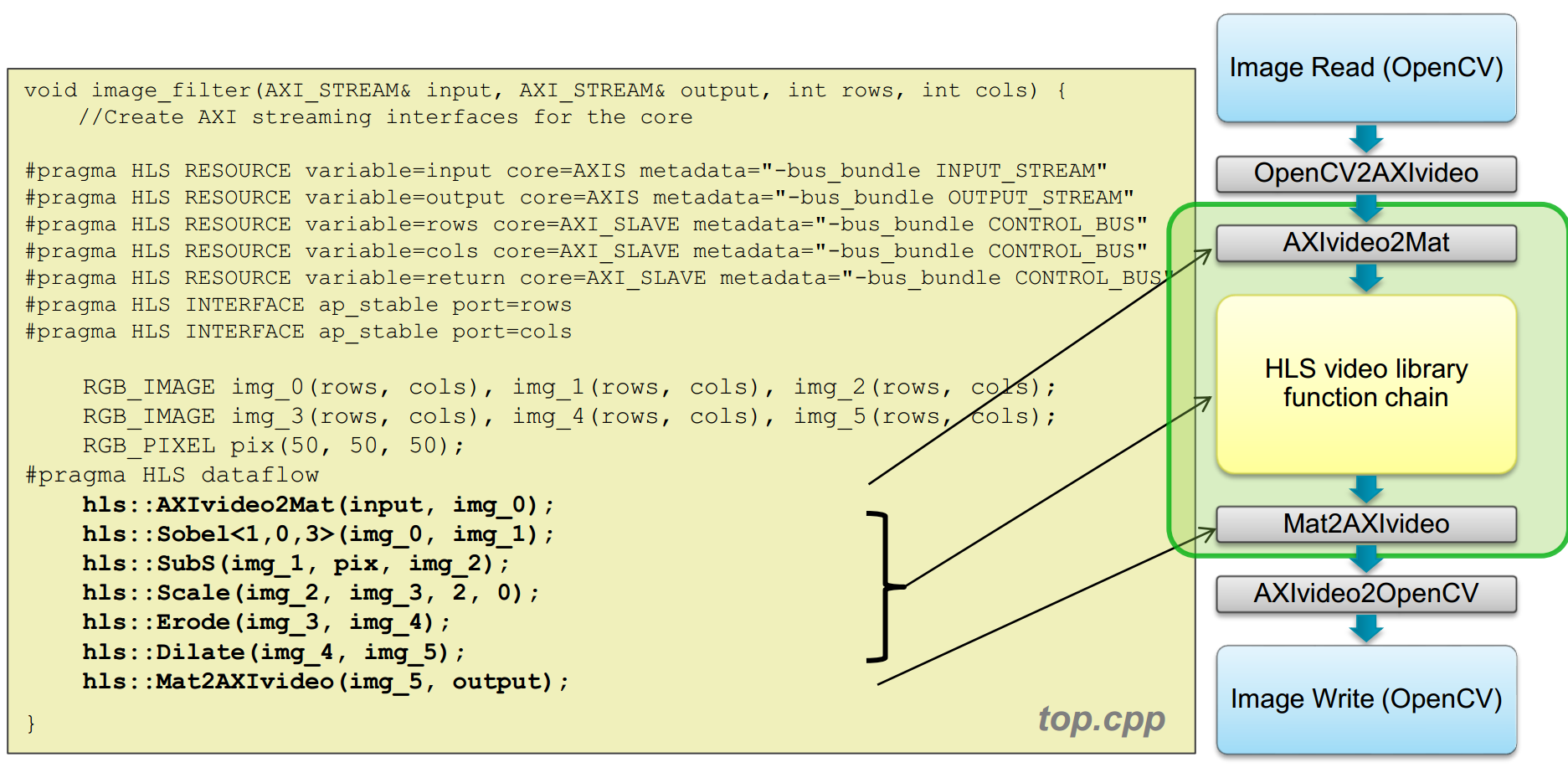

可以在代码里直接添加AXI接口,在vivado里互连很方便

HLS里对视频接口的约束如下

HLS Directives for Video Processing

#pragma HLS RESOURCE variable=input core=AXIS metadata="-bus_bundle INPUT_STREAM"

#pragma HLS RESOURCE variable=rows core=AXI_SLAVE metadata="-bus_bundle CONTROL_BUS"

#pragma HLS INTERFACE ap_stable port=rows

#pragma HLS dataflow