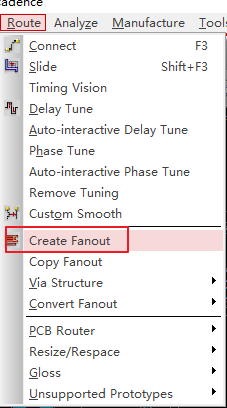

1.菜单栏选择 Route -- Create Fanout

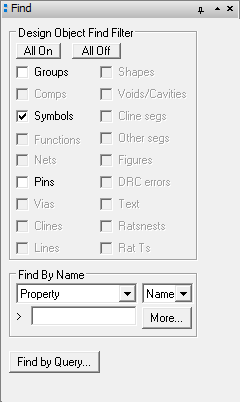

2.Find栏目中选择Symbols

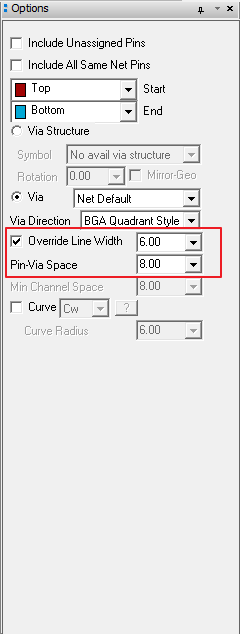

3.Options中via Direction选择BGA Quadrant Style。勾选上override line width。填上合适的线宽

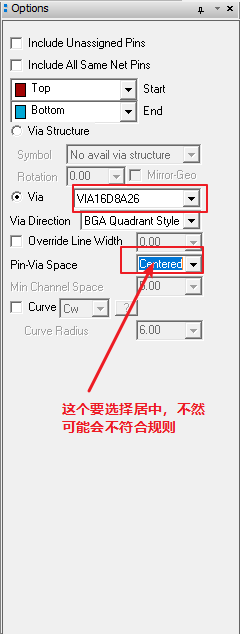

或者不勾选override line width,而是选择合适的焊盘即可

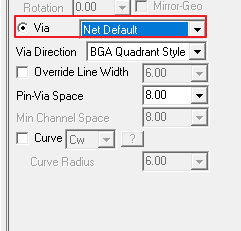

注意:Allegro一开始的时候via是Net default的,并没有焊盘给你选择,如下图

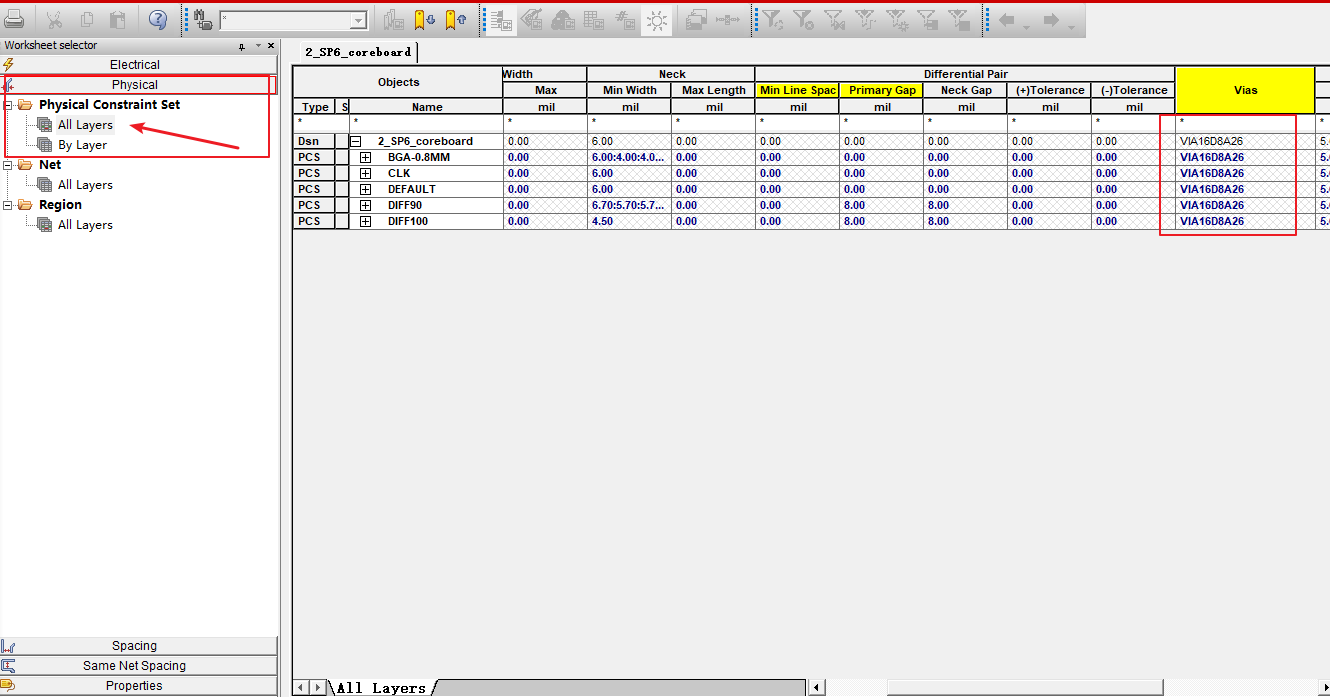

这个需要在规则中设置一下焊盘,打开约束管理器

选择Constraint Manager-->Physical -->Physical Constraint Set-->All layers,找到vias选项,给他对应的焊盘即可。

4.点击需要扇出的BGA器件即可

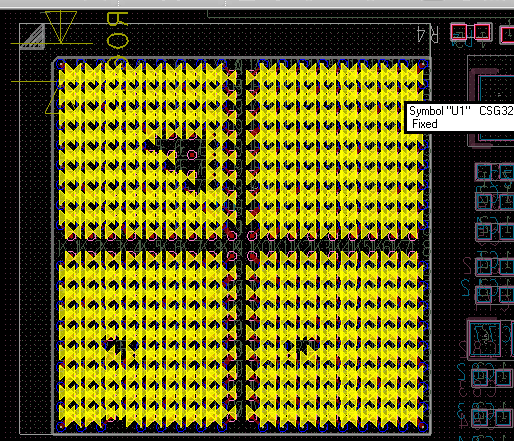

BGA器件扇出如果Pin-Via Space不选择Centered的话,可能是会报错的,比如是这样的

满满的都是DRC Mark,提示你出错了。

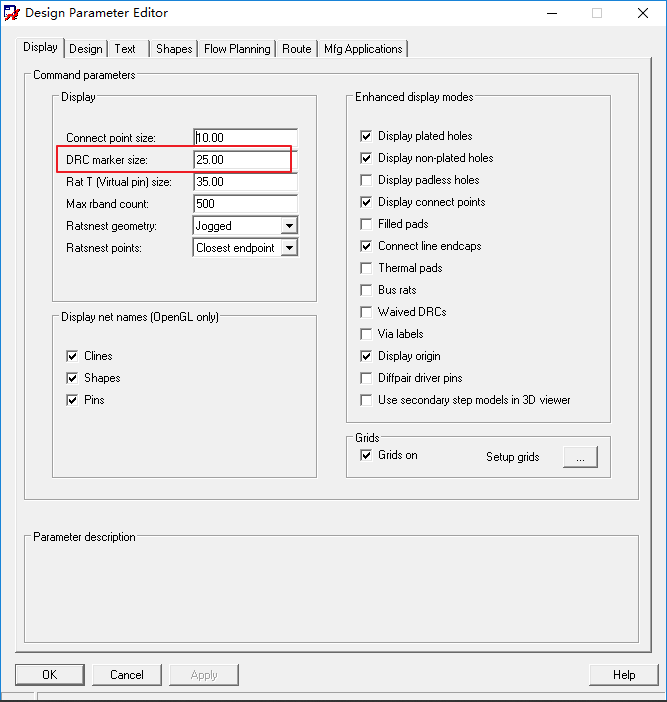

(DRC Mark点原本是很大的,可以改小一点,方便查看.点击Setup -- Design Parameters)

去修改他的DRC Mark Size.

要解决这个问题,就需要去修改Allegro BGA区域规则。将BGA这块区域允许的最小间距给他缩小一些。建议Pin-via Space选择Centered。不用修改规则不会报错。