基于TimeQuest Timing Analyzer的时序分析笔记(一)

首先声明英文来自ug-qpp-timing-analyzer(Intel? Quartus? Prime Pro Edition User Guide–Timing Analyzer)文档,非专业翻译,如有错误,自行解决。文档下载链接

一.简单介绍时序分析

Comprehensive timing analysis of your design allows you to validate circuit performance, identify timing violations, and drive the Fitter’s placement of logic to meet your timing goals.

译文: 对您的设计进行全面的时序分析,使您能够验证电路性能,识别时序违规,并驱动Fitter的逻辑位置,以满足您的时序目标。

The Timing Analyzer verifies that required timing relationships are met for your design to correctly function, and confirms actual signal arrival times against the constraints that you specify

译文: 时序分析器验证所需的时序关系是否满足您的设计以正确的功能,并根据您指定的约束确认实际信号到达时间。

其他来源:

时序分析:目的是通过分析FPGA设计中各个寄存器之间的数据和传输路径,分析数据延迟和时钟延迟之间的关系。一个设计ok的系统,必然能够保证整个系统中所有的寄存器都能够正确的寄存数据。

时序约束:

1.告知eda软件,该设计需要达到怎样的时序指标,然后eda软件会根据时序约束的各个参数,尽力优化布局布线,以达到约束的指标。

2.协助eda软件进行分析设计的时序路径,以产生相应的时序报告。

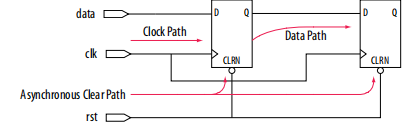

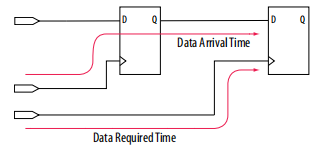

二、 时序分析仪分析常用典型路径

除了在设计中识别各种路径外,时序分析器还分析时钟特性,以计算单个寄存器到寄存器中任意两个寄存器之间的最坏情况需求 路径。 在分析时钟特性之前,必须对设计中的所有时钟进行约束。

数据到达时间与数据需要到达时间关系图

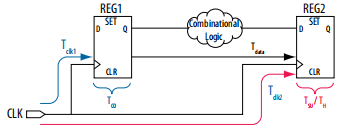

寄存器到寄存器之间路径关系图

上面三个图由浅入深介绍时序分析中重点时序路径

三、建立时间保持时间

Setup Time:即建立时间,在时钟上升沿之前数据必须稳定的最短时间。若不满足setup time,数据无法进入寄存器

Setup Time:即建立时间,在时钟上升沿之前数据必须稳定的最短时间。若不满足setup time,数据无法进入寄存器

Hold Time:即保持时间,在时钟上升沿之后数据必须稳定的最短时间。若不满足hold time,数据无法进入寄存器:Th < Tco。Th 限制了数据传输的速度。如果Tco延时太短导致上一级寄存器锁存的数据侵占了下一级寄存器正在锁存数据的保持时间,那么下一级寄存器就无法有效的锁存数据,系统时序也就无法达到要求。

发射沿与锁存沿

Launch Edge:启动沿,前级寄存器发送数据对应的时钟沿,是时序分析的起点。

Latch Edge:锁存沿,后级寄存器捕获数据对应的时钟沿,是时序分析的终点。相对于launch edge通常为一个时钟周期,但不绝对,如多周期约束。

四、公式建立与分析

基于寄存器到寄存器之间路径关系图分析

对于上图公式减去了setup uncertainty,即考虑最坏的情况仍需满足data required time (setup)。我们先忽略setup uncertainty,后面介绍

那么我们可以知道要满足建立时间时序要求应达到

Tclk1+Tco+Tdata<=Tclk+Tclk2-Tsu

即Tclk+Tclk2-Tsu-(Tclk1+Tco+Tdata)>=0

Tclk+(Tclk2-Tclk1)-Tsu-Tco-Tdata>=0

Tclk+Tskew-Tsu-Tco-Tdata>=0

即建立时间余量(如下图)

Slack=Tclk+Tskew-Tsu-Tco-Tdata

Slack>0:目的寄存器能够正确的接收源寄存器发射过来的数据

Tclk+Tclk2-Tsu:数据需求时间

Tclk1+Tco+Tdata:数据实际到达时间

Slack:数据需求时间与数据实际到达时间的差值,如果为正值说明数据能被目的寄存器正确接收;如果为负值说明数据不能被目的寄存器正确接收

Tco:时钟上升沿到达D触发器 到 数据输出到Q端的延迟

Tsu:建立时间,目的寄存器自身的特性决定,在时钟上升沿来临之前,数据输入端数据必须稳定的最小时间。

Tclk1:时钟信号从时钟源端口出发,到达源寄存器时钟端口时间

Tdata:数据从源寄存器Q端出发,到达目的寄存器D端时间

Tclk:时钟周期(Latch edge-launch edg)

Tclk2:时钟信号从时钟源端口出发,到达目的寄存器时钟端口时间

Tskew:时钟信号从时钟源端口出发,到达源寄存器和目的寄存器时钟端口的时间差值

时钟偏斜(skew):时钟从源端口出发,到达目的寄存器和源寄存器时间差值

本文暂时介绍建立时间相关知识一般分析,保持时间后续再出,下一篇介绍基于TimeQuest Timing Analyzer工具分析实际工具中涉及到的建立时间相关知识