����TimeQuest Timing Analyzer��ʱ������ʼǣ��壩

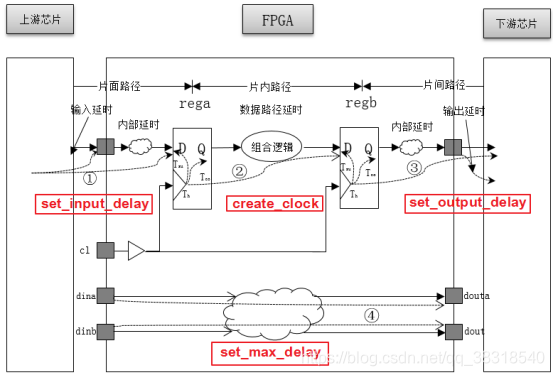

�ڸ���ϵͳ�� FPGA ʱ��Լ����ֹ�����ڲ�ʱ��Լ������Ӧ���������� IO ʱ��Լ����ʱ������Լ������ʵ�� PCB �弶��ʱ����������ˣ� FPGA ʱ��Լ���� IO ��ʱ��Լ��Ҳ��һ���ص㡣ֻ��Լ����ȷ�����ڸ�������±�֤ FPGA ���ⲿ����ͨ����ȷ�����Ķ�ioԼ�����м��ܡ�

һ������ʱ��·����ʶ

TimeQuest ��̬ʱ������Ķ���������Ĵ����ͼĴ���֮���·����I/O ֮�䡢I/O �ͼĴ���֮���·�����첽��λ�ͼĴ���֮���·����TimeQuest ����Data Arrival Time ��Data Required Time �����ʱ��������Slack������ʱ������Ϊ��ֵʱ���ͷ�����ʱ��Υ�棨Timing Violation������Ҫ�ر�ָ����һ���ǣ�����ʱ����������ʱ�������ĵ�·���еģ����Է����Ķ���һ���ǡ��Ĵ���-�Ĵ������ԡ��ڷ����漰��I/O ��ʱ���ϵ��ʱ������ȱ��һ���Ĵ��������������ɡ��Ĵ���-�Ĵ����� �ԣ���ʵ�Ǵ���FPGA ��I/O ���ţ���FPGA �ⲿ������һ���Ĵ�����Ϊ��������

���ȶ���ͼ��һ������ʶ������������·�����Խ���ʱ��Լ������2��ΪFPGA�ڲ���ǰ�漸ƪ�����Ѿ����ܹ������Ķ�ioԼ����������

����FPGA �������

���� IO ��ʱ��Լ������������ڵ�·������ϵͳ����ʱ����������� FPGA ��Ҫ��Ϊһ��������������а��� FPGA �Ľ���ʱ�䡢 ����ʱ���Լ�������ʱ�� ��ͳ�Ľ���ʱ�䡢����ʱ���Լ�������ʱ������ԼĴ�����ʽ�ķ����� �����������ϵͳ FPGA �Ľ���ʱ�䱣��ʱ����Լ�

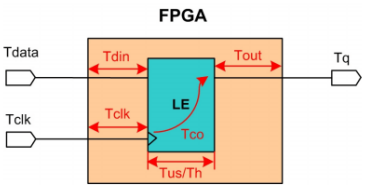

����ͼ ��ʾ��Ϊ�ֽ�� FPGA �ڲ��Ĵ��������ܲ�����

��1�� Tdin Ϊ�� FPGA �� IO �ڵ� FPGA �ڲ��Ĵ�������˵���ʱ��

��2�� Tclk Ϊ�� FPGA �� IO �ڵ� FPGA �ڲ��Ĵ���ʱ�Ӷ˵���ʱ��

��3�� Tus/Th Ϊ FPGA �ڲ��Ĵ����Ľ���ʱ��ͱ���ʱ�䣻

��4�� Tco Ϊ FPGA �ڲ��Ĵ�������ʱ�䣻

��5�� Tout Ϊ�� FPGA �Ĵ�������� IO ���������ʱ��

���Ϸ����� FPGA ��Ϊһ��ϵͳ�ɽ��� IO ʱ�������

����Դ�Ĵ�����Ŀ�ļĴ�������һ������ FPGA �ڲ�������£�����Լ�� FPGA��ʱ�������� EDA ������������·�����з�����

��ʱ��Լ����Ҫ���Ǹ���EDA���������ʱ���źŵ�Ƶ�ʡ�

IOԼ������ͨ����֪ EDA ����һЩIO����·���е���֪ʱ����������� EDA �������벢���� FPGA �ڲ��ĸ���·�������ӳ٣�ʹ���ܵ�·���ܹ����㽨��ʱ������Ϊ����Ŀ�ġ�

����IOʱ�������Ϊϵͳͬ����Դͬ����������

ϵͳͬ��

����ͬһʱ��Դ����ϵͳͬ�����������䴫����ʱ��ȷ�����������ڸ������ݴ��䣬��Ҫ�˽�����в������֪ʶ

Դͬ��

ʹ�öԶ˵�ʱ���ź���Ϊ�����źţ�ʱ���źź������źű���ȷ������λ��ϵ��Դͬ��������ź���ʱ�Ӻ������źţ����ʱ������fpga�����ģ��������ʱ���ж��ֲ�����ʽ�����磺

�����뿴�ò���

���ĵķ����Ե�һ��������н���

1��ͨ��fpga������������ʱ�ӣ�

2��ͨ��fpga��ALTDDIO IP�˲������ʱ�ӣ�

3��ͨ��״̬�����Ʋ������ʱ�ӣ�

4�����������ݵ�ʱ��ֱ�������

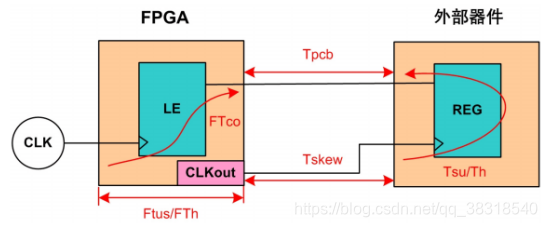

�ġ�Դͬ������

����Դͬ���־���·����1����input delay���ͣ�3����output delay�����֣����²����������Ըò��Ķ�������С÷��Ŀ�

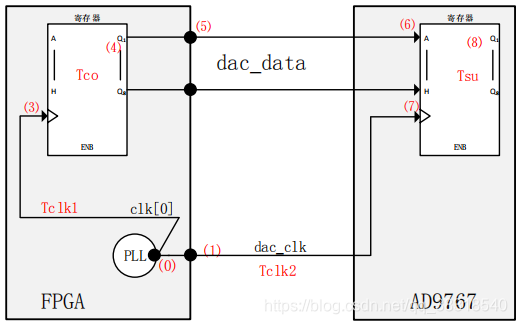

��ͼ��ʾ��·����3�����ݺ�ʱ�Ӷ��Ǵ�FPGA���ⲿ��������ģ�����ͼʾ��ADV7123������Ƭ���SDRAM������һ�ࡣ

0-3��Tclk1----PLL����ʱ���źŵ�Դ�Ĵ�����ʱ����ʱ����ʹ����ȫ��ʱ����·��һ��ʱ��С���DZ�Ȼ���ڡ�

---- ֵ��֪��������TimeQuest Timing Analyzer��������֪����EDA��������һ���̶ȿ�����ֵ��С

3-4��Tco-----D����������Ĵ����Ľ���ʱ���ǰ���£���ʱ�Ӷ˿������ص�������Դ�Ĵ�����������ȶ�����������Ҫ��ʱ�䡣�ⲿ���� ʱ���������������ģ���������������Ż���

-----ֵ��֪����������һ�����е�������������ֵTTA��EDA����Ҳ֪��

4-5��Tout(Tdata_int)�����ݴӼĴ���Q�˿ڲ�������IO�ڣ���FPGA�ڲ����������ѵ�ʱ�䡣

-----ֵ��֪��������TTA��������֪����EDA��������һ���̶ȿ�����ֵ��С

5-6��Tdata_PCB�����ݴ�FPGA�����Ŀ�ļĴ�������PCB���ߴ��仨�ѵ�ʱ�䡣�����Լ���ģ�5555mil/ns���������������ʱ�������Ϊʱһ����֪����

Tsu����֪��ֵ

0-1��Tclk2_int�����ʱ�ӵ���FPGA���ŵ���ʱ

-----ֵ��֪��������TTA��������֪����EDA��������һ���̶ȿ�����ֵ��С

1-7��Tclk2_ext----���ʱ�ӵ����ⲿ������������ʱ

-----�����Լ���ģ�5555mil/ns���������������ʱ�������Ϊʱһ����֪����

ʱ��������£�

��ʽ�Ƶ�

��ʽ�Ƶ�

Setup��

data arrive=launch edge+Tclk1+Tco+Tdata(int)+Tdata(PCB)

data require=latch edge+Tclk2(int)+Tclk2(PCB)-Tsu

slack(Tu)=data require-data arrive>=0

����ã�

Latch edge+Tclk2(int)+Tclk2(PCB)-Tsu �C [launch edge+Tclk1+Tco+Tdata(int)+Tdata(PCB)]>=0

����ã���֪������ߣ���������ص�δ֪��/FPGA����ͨ���Ż����ֲ��߶��ı�������ұߡ�����Ҳ��һ�µģ�����������

(Latch edge-launch edge) - [Tdata(PCB) +Tsu -Tclk2(PCB)]>=Tdata(int) +Tco+Tclk1-Tclk2(int)

�������ʱ�����ݾ������Ĵ�����ʱ��Ȼ�ܹ������ⲿĿ�ļĴ����Ľ���ʱ��

Output delay max = [ Tdata(PCB) +Tsu -Tclk2(PCB) ]

Hold��

data arrive= launch edge+Tclk1+Tco+Tdata(int)+Tdata(PCB)

data require= latch edge+Tclk2(int)+Tclk2(PCB) + Th

slack(Th)= data arrive - data require >=0;

=[launch edge+Tclk1+Tco+Tdata(int)+Tdata(PCB)] - [latch edge + Tclk2(int)+Tclk2(PCB)+Th] >=0

=launch edge - Latch edge + [Tdata(PCB) �C Th �CTclk2(PCB)] >= Tclk2(int)-[Tdata(int) +Tco+Tclk1]

��С������ʱ��֤���ݾ�����С�Ĵ����ӳٵ���Ŀ�ļĴ����������ܹ�����Ŀ�ļĴ����ı���ʱ�䡣

Output delay min= [Tdata(PCB) �C Th �CTclk2(PCB)]

ע�⣺���Ϸ����ж���FPGA���ⲿ����֮���pcb����һ����Լ�����������Tdata(PCB)��Tclk2(PCB)�ȳ�ʱ�����ǻᷢ���ַ·�ص��ڲ��Ĵ������Ĵ����ķ�����

Output delay max = Tsu

Output delay min= �C Th

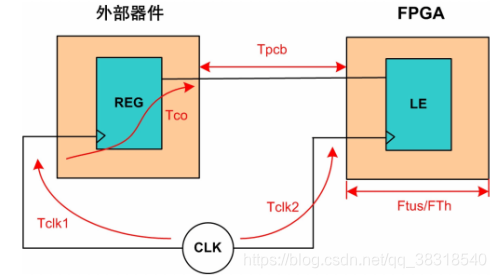

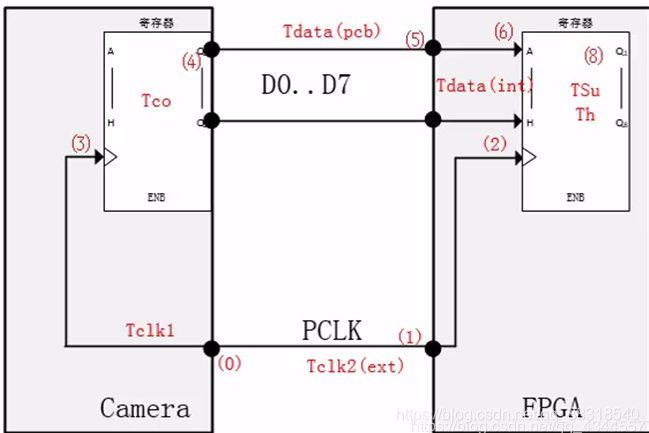

·����1����ͼ��ʾ��ʱ���źź����ݶ��Ǵ��ⲿ��FPGA����ġ������ⲿ����ͷ�ɼ���ͼ��������Ҫ����FPGA�ڲ����д����ȡ�������ʽ��������һ�µġ�

Tclk1��δ֪����TcoҲ�Ǹ�δ֪����

���ǡ�Tck1��Tco ��ֵһ���ֲ��������������� Tco

Tclk2��ext���ǿ���ͨ��PCB���߳��ȼ�������ģ�5555ml/ns����

Tdata��pcb���ǿ���ͨ��PcB ���߳��ȼ�������ģ�5555ml/ns������

Tdata��int����֪��������EDA��������ͨ������������֪��������һ���̶��Ͽ��Ƹ�·�����ӳ١�

Tsu�ò�֪�������� EDA ��������ͨ������������֪����

Tck2(int)��֪��������EOA��������ͨ������������֪��������һ���̶��Ͽ��Ƹ�·�����ӳ١�

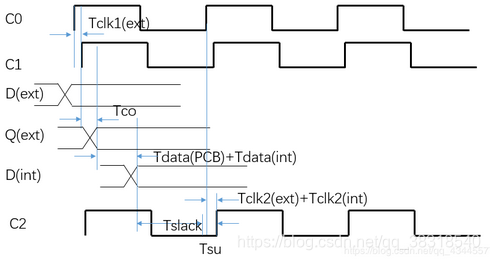

ʱ��ͼ������ʾ��

Setup time

data require = latch edge + Tclk2(ext)+Tclk2(int) �CTsu

data arrive = launch edge + Tclk1 +Tco + Tdata(PCB)+Tdata(int)

slack(Tu) = data require - data arrive

= latch edge + Tclk2(ext)+Tclk2(int) �CTsu �C [ launch edge + Tclk1 +Tco + Tdata(PCB)+Tdata(int) ] >=0

�����

latch edge - launch edge + Tclk2(ext) - Tco - Tclk1 -Tdata(PCB) >= Tsu + Tdata(int) - Tclk2(int)

�ⲿ�����ֲ��г�����Tco + Tclk1 ͳ��Ϊ Tco�����

latch edge - launch edge �C[ Tco - Tclk2(ext) + Tdata(PCB) ]>= Tsu + Tdata(int) - Tclk2(int)

���������ʱ�����ݾ��������ⲿ����·���ӳ٣�����FPGA�ļĴ���ʱ�����ܹ�����üĴ����Ľ���ʱ��

Input delay max = Tco��max�� - Tclk2(ext) + Tdata(PCB)

Hold time

data arrive = launch edge + Tclk1 +Tco + Tdata(PCB)+Tdata(int)

data require = latch edge + Tclk2(ext)+Tclk2(int) +Th

slack(Th) = data arrive -data require

= launch edge + Tclk1 +Tco + Tdata(PCB)+Tdata(int) �C [ latch edge + Tclk2(ext)+Tclk2(int) +Th ] >=0

�����

launch edge - latch edge + Tco + Tdata(PCB) - Tclk2(ext) >= Tclk2(int) - Tdata(int) + Th

��С������ʱ�����ݾ�����С���ⲿ����·���ӳ٣�����FPGa�ļĴ���ʱ�����ܹ����ƻ��üĴ�������ǰһ��ʱ�����ⲿ������������ݡ�Ҫ�ܹ�����üĴ����ı���ʱ�䡣

Input delay min = Tco��min�� + Tdata(PCB) - Tclk2(ext)

ֵ��ע����ǣ���ȻInput delay max ��Input delay min �ı���ʽһ�������Ƿ���ģ�Ͳ�ͬ������delay max��ʱ������Tco�����ܵĴ�min��ʱ���෴��

Input delay max = Tco��max�� - Tclk2(ext)��min�� + Tdata(PCB)��max��

Input delay min = Tco��min�� - Tclk2(ext)��max�� + Tdata(PCB)��min��

��PCBʱ����� Tdata(PCB) = Tclk2(ext) ��ģ�ͽ���Ϊ����Tco��