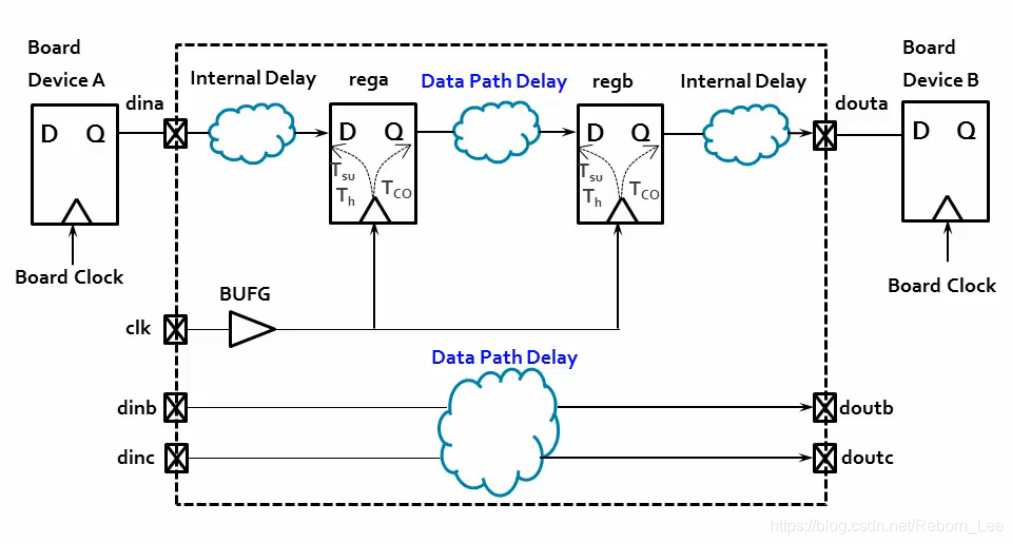

如下,经典的时序分析模型:

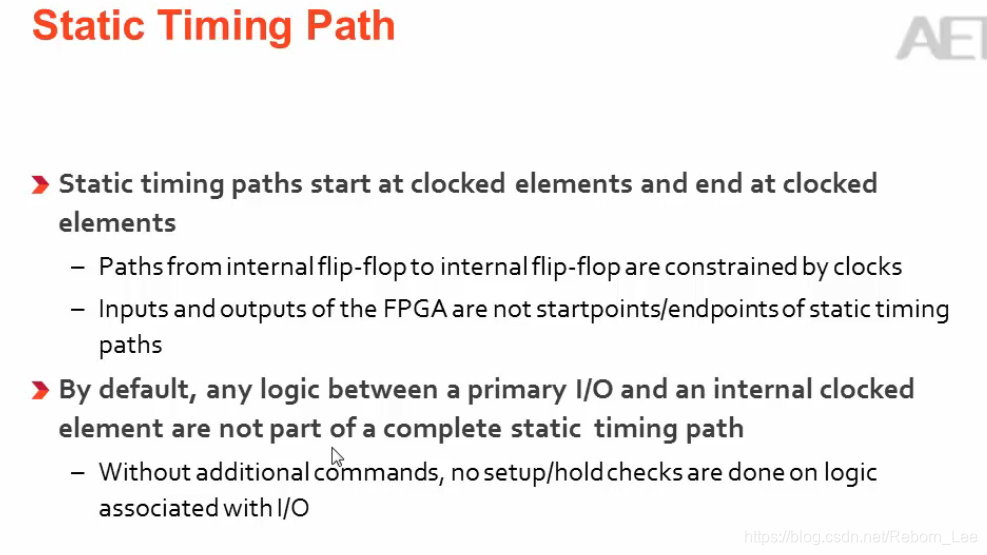

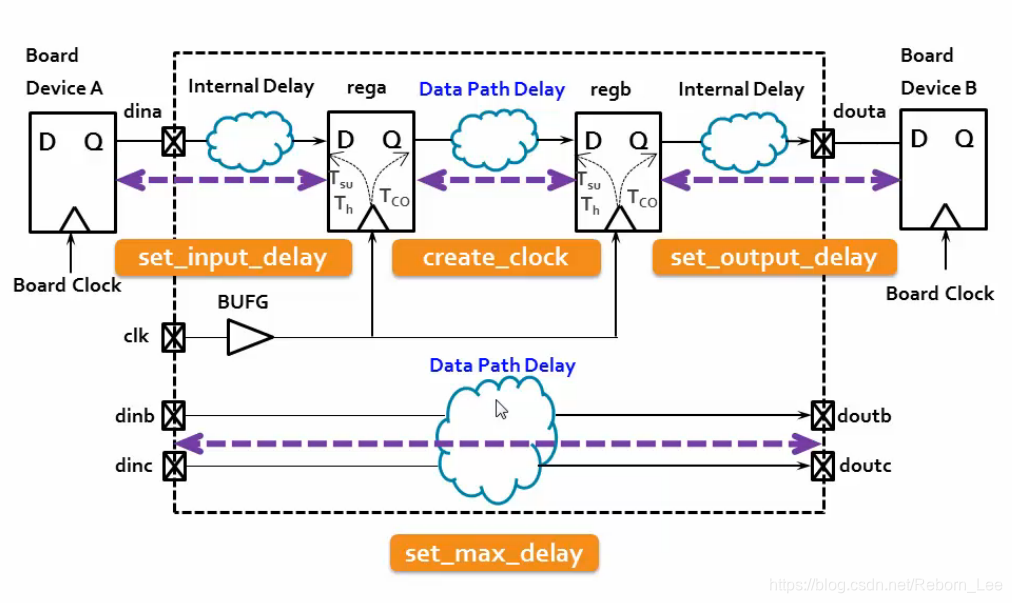

不同的路径使用不同的约束:

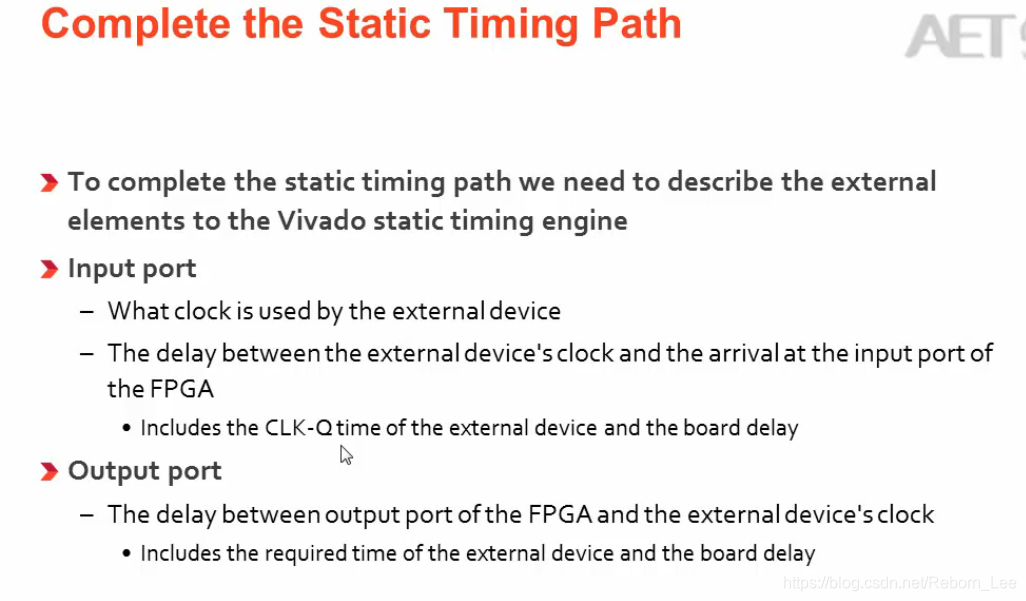

上游芯片到FPGA内部第一级触发器的路径使用set_input_delay来约束;

FGPA内部的触发器之间使用create_clock来约束;

FPGA末级触发器到下游芯片的时序元件之间用set_output_delay来约束;

最后一个路径是纯粹的组合逻辑用set_max_delay来设置约束。

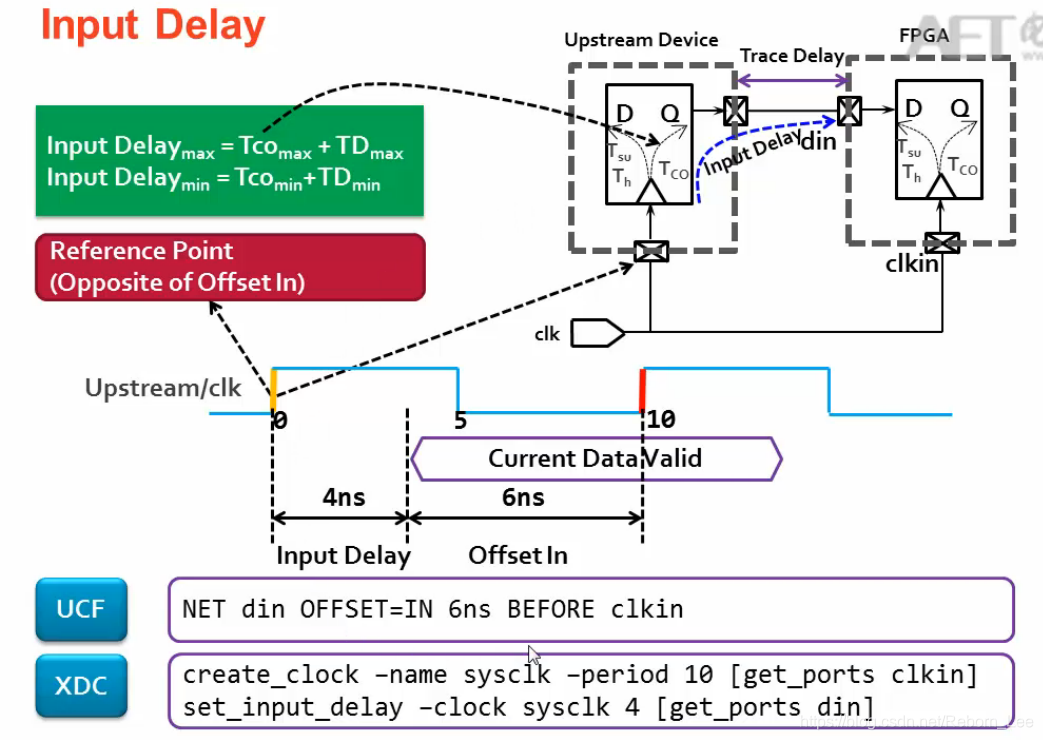

Input Delay

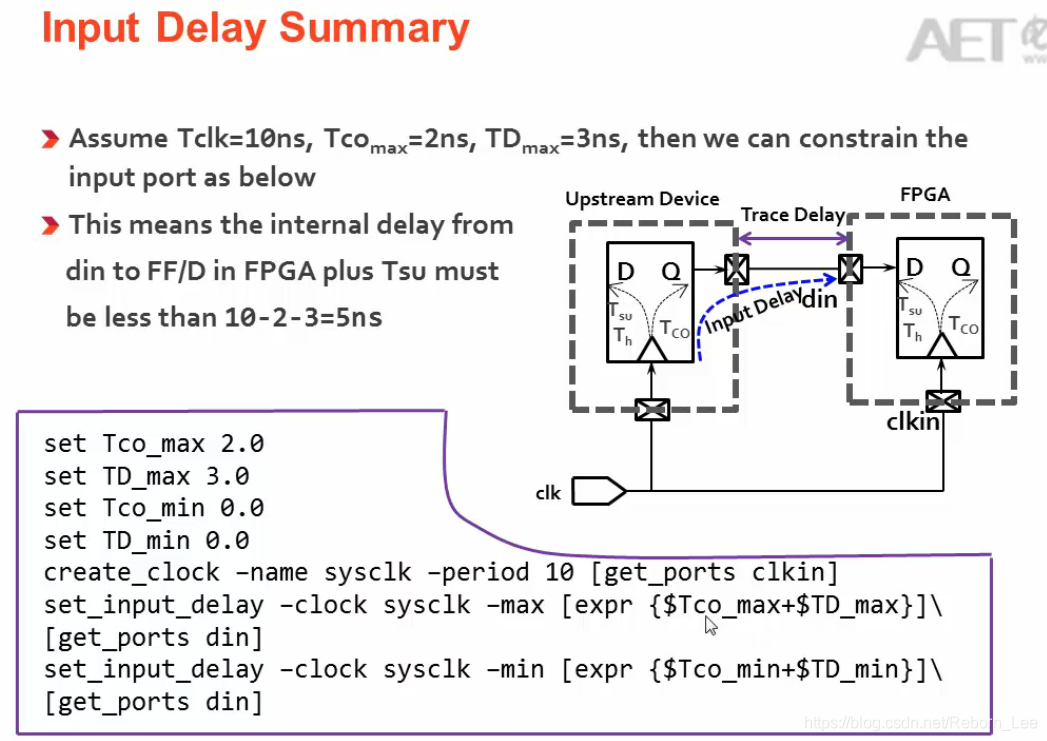

由上图可以看出Input Delay是以上游芯片的时钟发送沿为参考,发送数据到达FPGA的外部端口之间的延迟。

输入延迟(input delay)包括Tco和Trace Delay(板间延迟),其中Trace delay又叫Board delay。

上图还给得出了ISE中UCE文件的Offset In和Vivado中XDC中的set_input_delay之间的区别,二者是由很大的区别的。

XDC文件中,input delay是以时钟发送沿为参考,到达FPGA端口的延迟时间;而UCF文件中是以捕获沿为参考,它之前的一段时间内,数据有效。

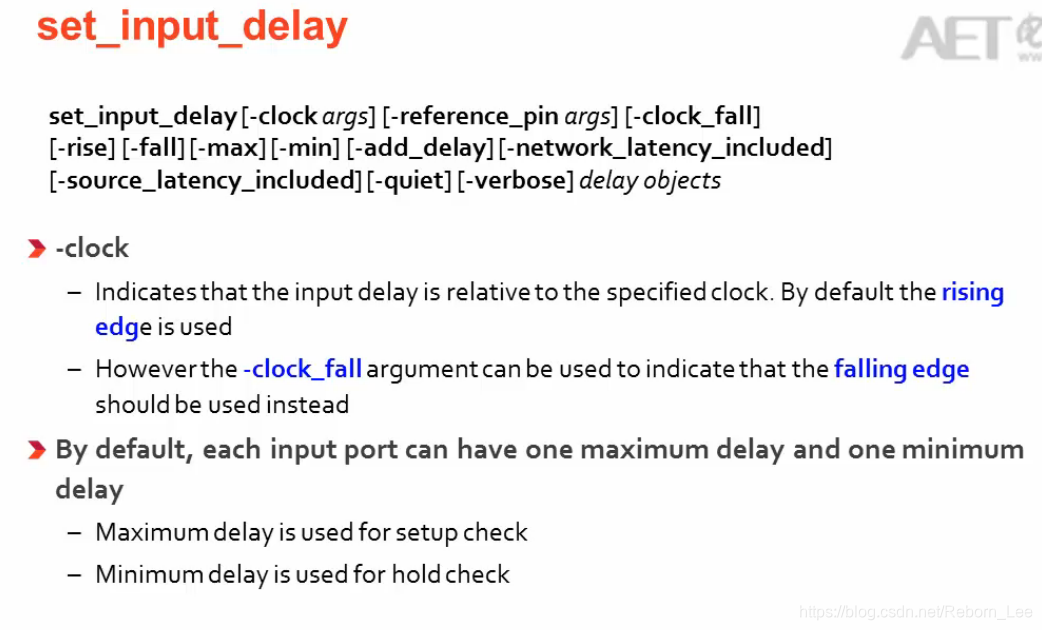

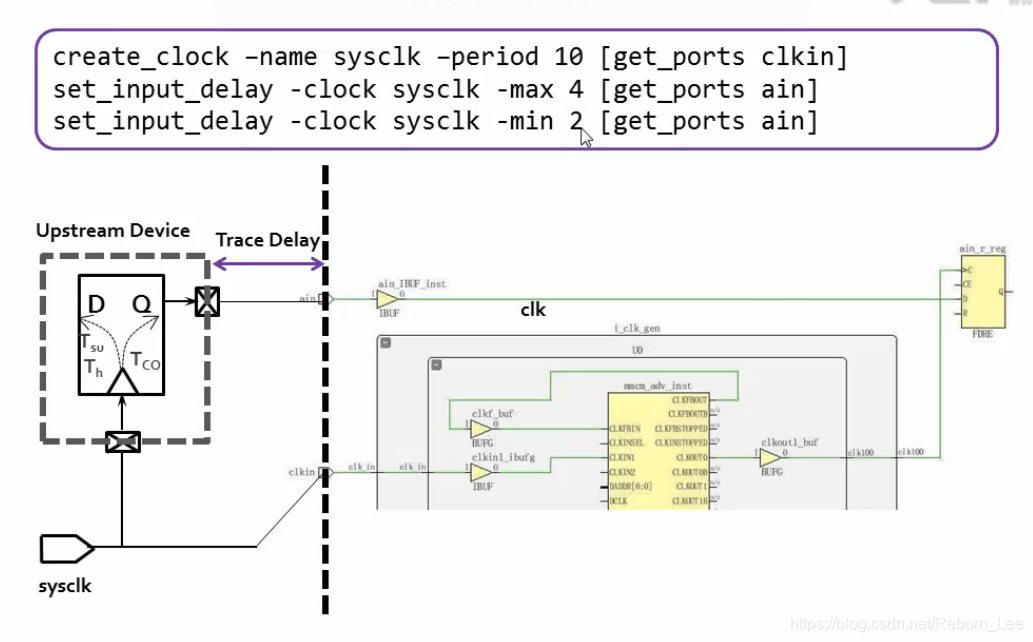

输入延迟命令选项:

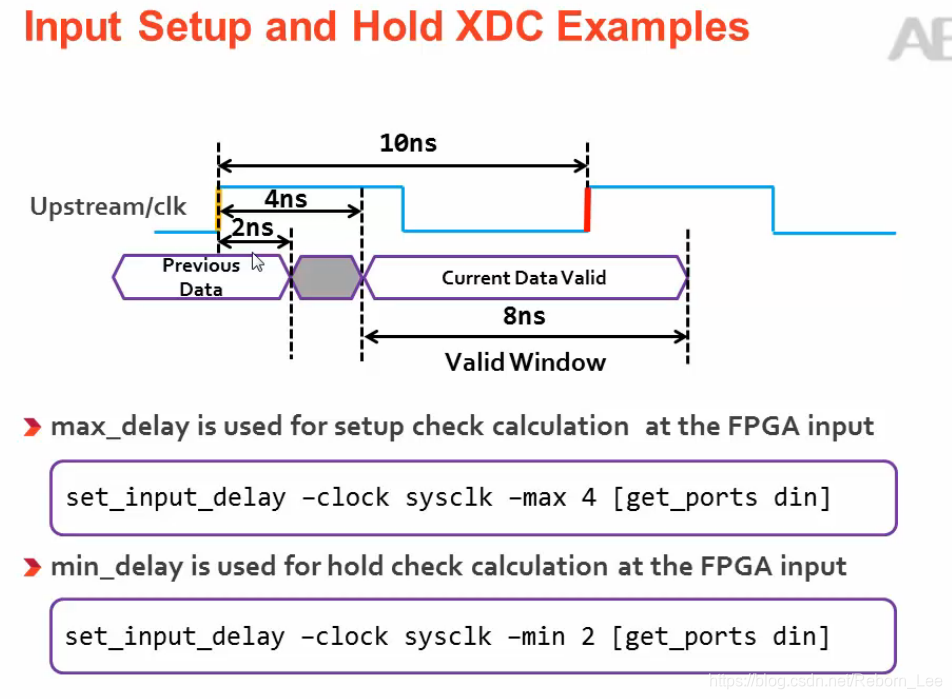

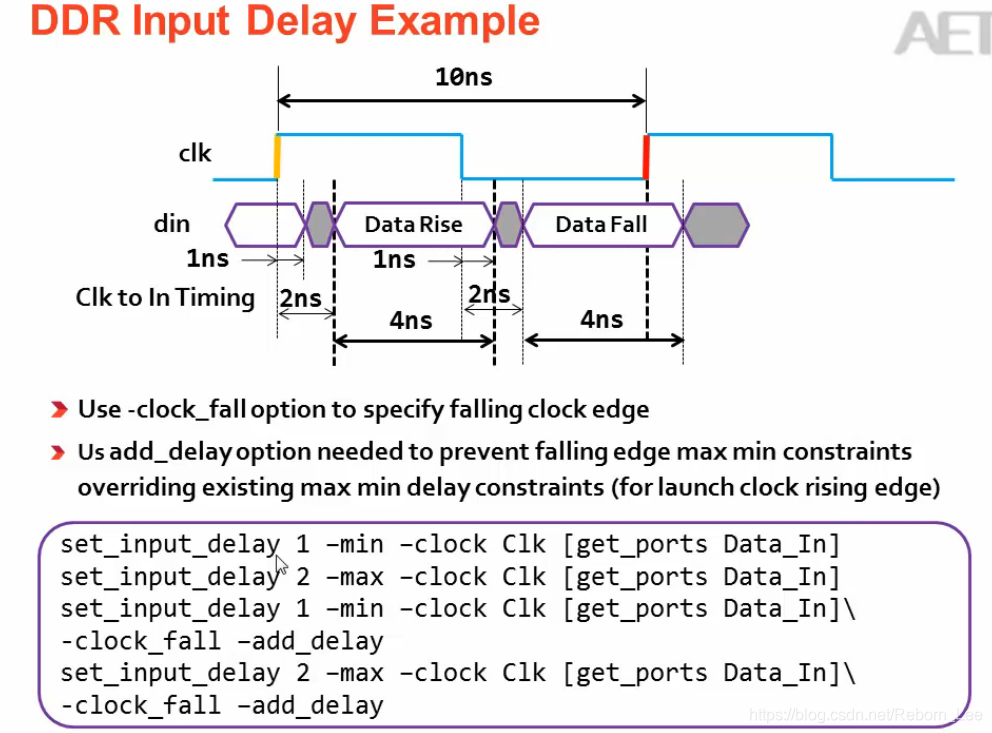

最小和最大输入延迟命令选项,“-min”和“-max”选项,为下面指定不同的值:

(1)最小延迟分析(保持/去除);

(2)最大延迟分析(建立/恢复)。

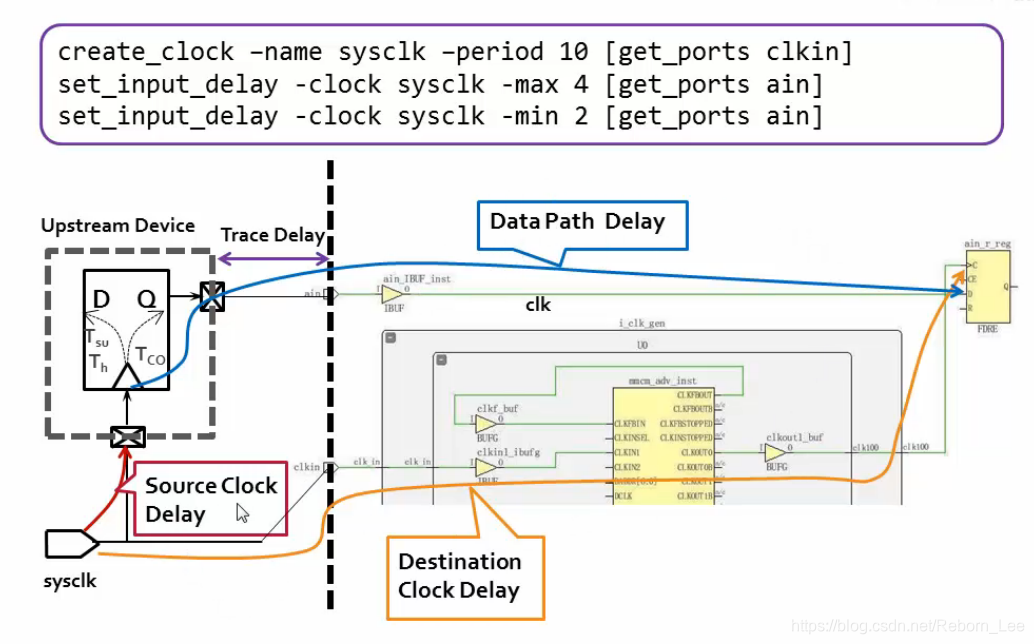

将FPGA展开分析如下图:

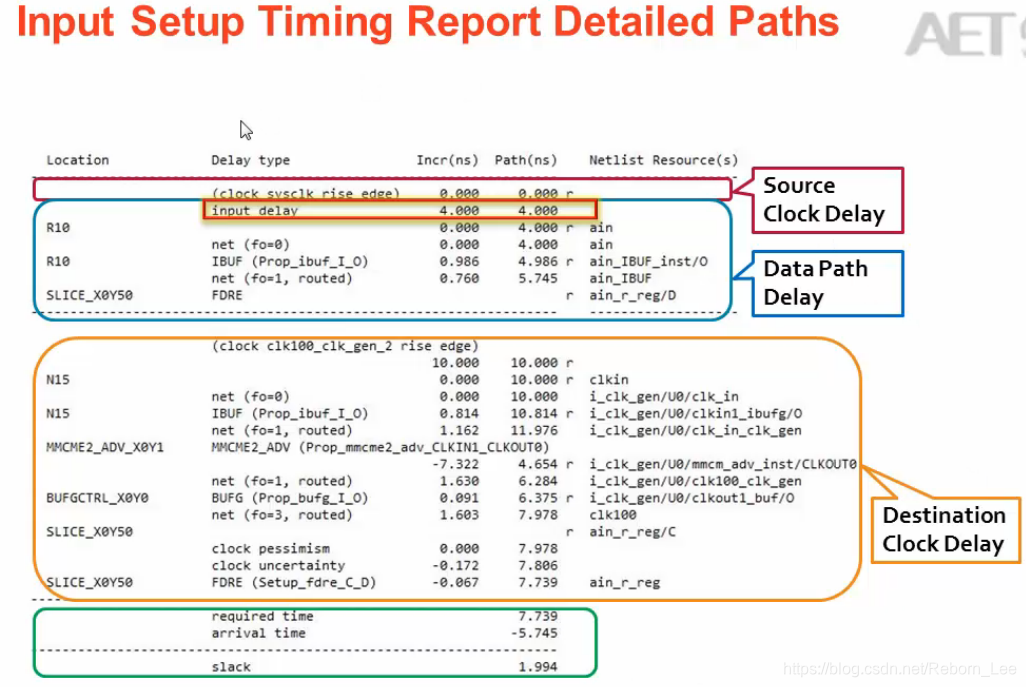

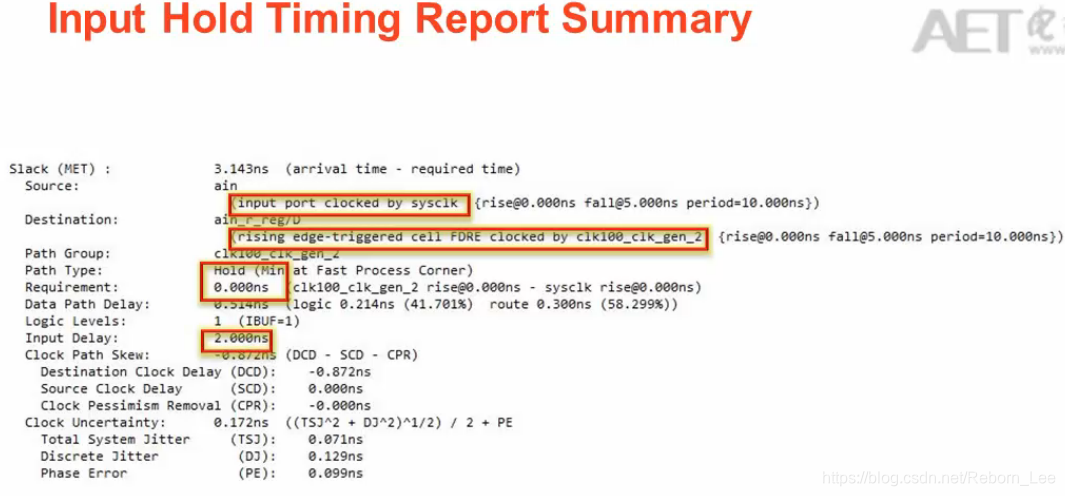

在时序报告中上述三个路径延迟都会有显示:

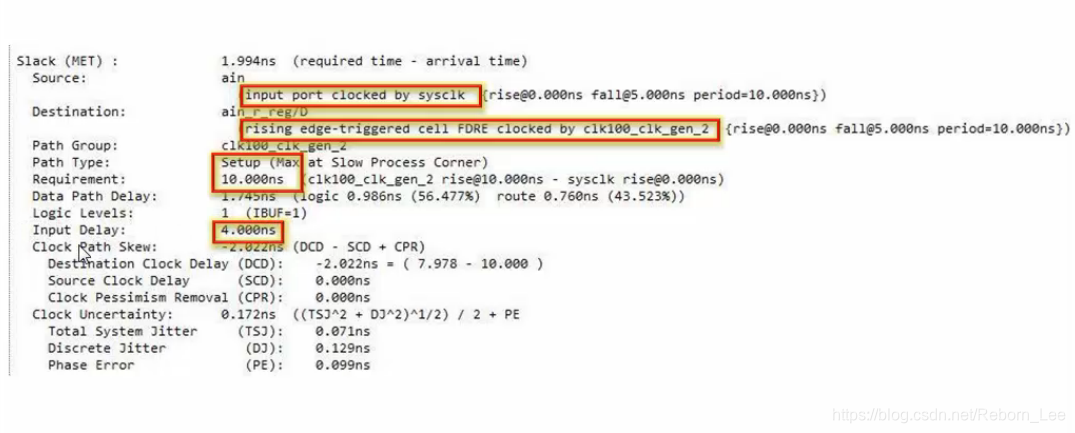

如下输入建立时间报告:

可见,source的时钟为sysclk,destination的时钟为第一级触发器的时钟,也就是mmcm产生的时钟。

setup Timing也就是最大的输入延迟“max”,时钟周期为10ns,输入延迟为4ns。

更加详细的时序路径分析:

设置输入延迟的语法规则: