目录

抛砖引玉

使用CASEZ来解决

写在最后

抛砖引玉

优先级编码器是一种组合电路,当给定输入位向量时,输出该向量中第一个1位的位置。 例如,给定输入8'b10010000的8位优先级编码器将输出3'd4,因为bit [4]是高的第一位。

构建一个4位优先级编码器。 对于此问题,如果所有输入位都不为高(即输入为零),则输出零。 请注意,一个4位数字具有16种可能的组合。

如何设计这样的一个优先编码器,我们首先应该能够想到的是使用语法case,然后也很容易惯性思维,列出每一种情况,然后对应的输出是多少?

例如:

//伪代码

case(input)

4'b0001: output = 1;

.......

4'b1111:output = 1;

default: output = 0;

endcase

如果真是这样写的话, 那么8位优先编码器?更多位的优先编码器呢?那组合岂不多了去了,像本人师弟说的,感觉这样做很傻?哈哈,确实如此,有更简单的方法,思维要灵活,我们这里既不用casex也不用casez,也能把这个优先编码器安排的稳稳当当。

// synthesis verilog_input_version verilog_2001

module top_module (input [3:0] in,output reg [1:0] pos );always@(*) begincase(1)in[0]: pos = 0;in[1]: pos = 1;in[2]: pos = 2;in[3]: pos = 3;default: pos = 0;endcaseendendmodule

这样的话,N位编码器都只需要N个case分支即可。

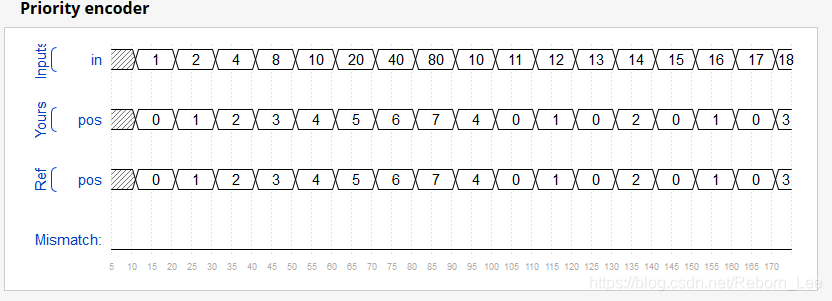

代入到HDLBits验证:

使用CASEZ来解决

为8位输入构建优先级编码器。 给定一个8位向量,输出应报告向量中的第一位,即1。如果输入向量没有高位,则报告为零。 例如,输入8'b10010000应该输出3'd4,因为bit [4]是高的第一位。

根据上一个练习(always_case2),case语句中将有256个案例。 如果case语句中支持的case项目无关紧要,我们可以减少这种情况(减少到9个case)。 这就是casez的目的:在比较中,将值z的位视为无关位。

例如,这将实现上一个练习中的4输入优先级编码器:

always @(*) begincasez (in[3:0])4'bzzz1: out = 0; // in[3:1] can be anything4'bzz1z: out = 1;4'bz1zz: out = 2;4'b1zzz: out = 3;default: out = 0;endcase end

一个case语句的行为就好像每个项目都被顺序检查一样(实际上,它的作用更像是生成一个巨大的真值表,然后进行门操作)。 请注意,如何有某些输入(例如4'b1111)可以匹配多个案例项目。 选择第一个匹配项(因此4'b1111匹配第一个项,out = 0,但不匹配任何后续项)。

- 还有一个类似的casex,将x和z都视为无关位。 我认为在casez上使用它的目的不大。

- 符号? 是z的同义词。 所以2'bz0与2'b?0相同

8位的优先编码器可以如下设计:

// synthesis verilog_input_version verilog_2001

module top_module (input [7:0] in,output reg [2:0] pos );always@(*) begincasez(in)8'bzzzz_zzz1: pos = 0;8'bzzzz_zz1z: pos = 1;8'bzzzz_z1zz: pos = 2;8'bzzzz_1zzz: pos = 3;8'bzzz1_zzzz: pos = 4;8'bzz1z_zzzz: pos = 5;8'bz1zz_zzzz: pos = 6;8'b1zzz_zzzz: pos = 7;default: pos = 0;endcaseendendmodule

代入HDLBits:

写在最后

最后说一句,上述优先编码器都可以使用如下方式来写,且甚至复杂度更低:

// synthesis verilog_input_version verilog_2001

module top_module (input [7:0] in,output reg [2:0] pos );always@(*) begincasez(1)in[0]: pos = 0;in[1]: pos = 1;in[2]: pos = 2;in[3]: pos = 3;in[4]: pos = 4;in[5]: pos = 5;in[6]: pos = 6;in[7]: pos = 7;default: pos = 0;endcaseendendmodule