ǰ��

�������ԣ�FPGA����ƻعˣ�10��DDR/DDR2/DDR3�е�ʱ������ĺ���

��ƪ���£�FPGA����ƻعˣ�9��DDR��ǰ�������Լ��ݱ�����еļ����������ᵽ�������̻���һϵ�������ۺŸ����������������洢ʱ������5-5-5-5��7-10-10-10�ȣ��� CAS�ӳ�ʼ������Щ�����еĵ�һ�����֡�

�������������أ���ƪ���»ὲ��Щ���ִ����ĺ��彲�������

�ڴ������ʶ����

DDR��DDR2��DDR3�ڴ��Ǹ����乤��������ٶȺ�ʱ��������ģ�ʱ����3-4-4-8��5-5-5-15��7-7-7-21��9-9-9-24�����֣�Խ��Խ�á����������Щ���ֵĺ��塣

DDR��DDR2��DDR3�ڴ���ѭDDRxxx/PCyyyy���ࡣ

��һ������xxx��ʾ���ڴ�оƬ֧�ֵ����ʱ���ٶȡ����磬DDR400�ڴ����߹���Ƶ��Ϊ400MHz��DDR2-800����߹���Ƶ��Ϊ800MHz��DDR3-1333����߹���Ƶ��Ϊ1,333MHz����Ҫע����ǣ��Ⲣ�����ڴ����ʵʱ���ٶȡ�DDR��DDR2��DDR3�ڴ��ʵ��ʱ���DZ�עʱ���ٶȵ�һ�롣���DDR400�ڴ�Ĺ���Ƶ��Ϊ200MHz��DDR2-800�ڴ�Ĺ���Ƶ��Ϊ400MHz��DDR3-1333�ڴ�Ĺ���Ƶ��Ϊ666MHz��

�ڶ������ֱ�ʾ���ڴ�ﵽ����������ʣ���λΪMB/s��DDR400�ڴ洫�����ݵ��ٶ����Ϊ3,200MB/s����˱����ΪPC3200��DDR2-800�ڴ洫�����ݵ��ٶ�Ϊ6400MB/s�����DZ���עΪPC2-6400����DDR3-1333�ڴ������10664MB/s���ٶȴ������ݣ����DZ���עΪPC3-10600��PC3-10666���������������ģ������� "DDR "�� "PC "���������� "2 "�� "3 "����ʾ����˵����DDR2��DDR3�ڴ棬������DDR��

��һ�����࣬DDRxxx�������������ڴ�оƬ�ı������ڶ������࣬PCyyyy�������������ڴ�ģ��ı���

������һƪ������Ҳ˵�ˣ�

�������Ͻ���������ϵͳDDRx-yyyy������x�Ǽ���������yyyy��DDRʱ�����ʣ������ڴ洢оƬ���ڴ�ģ�飨���ں����ڴ�оƬ��Сӡˢ��·�壩ʹ�ò�ͬ������ϵͳ��PCx-zzzz������x�Ǽ������ţ�zzzz��������۴������ʣ��ֳ�����������

��ͼ�У����Կ���һ��PC3-10666�ڴ�ģ�飬��ʹ�õ���DDR3-1333�ڴ�оƬ��ע��ʱ��7-7-7-18���͵�ѹ��1.5V����

�洢��ģ�����������ʿ���ͨ�����¹�ʽ���㡣

- ������۴����� = ʱ�� x λ�� / 8

����DIMMģ��һ�δ���64λ������ "λ�� "����64λ������64 / 8 = 8�����ǿ��Խ������ʽ��Ϊ��

- ������۴����� = ʱ�� x 8 ��

������ڴ�ģ�鰲װ���ڴ������Խϵ͵�ʱ���������е�ϵͳ�ϣ��ڴ�ģ��ʵ�ֵ���������ʽ������������ϵ���������ʡ�ʵ���ϣ�����һ���dz����������С�

����˵��������һ��DDR3-2133/PC3-17000�ڴ档�������DZ���עΪDDR3-2133�������Dz��������ϵͳ����2133MHz���ٶ��Զ����С���������֧�ֵ����ʱ�����ʣ��������������е�ʱ�����ʡ�����㽫����װ��֧��DDR3�ڴ����ͨPCϵͳ�ϣ����ǿ��ܻ���1,333 MHz(DDR3-1333)���ٶ����ШC����DDR3����߱��ٶȨCʵ��10,664 MB/s����������ʡ����ԣ����Dz����Զ�������2,133 MHz��Ҳ�����Զ��ﵽ17,000 MB/�������ʡ�

��ô��Ϊʲô���˻�����Щģ�飿���˻������ǵij�Ƶ�����������̱�֤��Щģ�齫���е�2,133�գ���֪�����������ڴ�����ʱ�ӵ�1,066�գ���ʵ�ָ��ߵ�����������ϵͳ�����ǣ�����������֧�����ֳ�Ƶ����ˣ�������������ϵͳ���г�Ƶ����ô�����ʾʱ��Ƶ�ʸ���ϵͳ֧�ֵ��ڴ�ģ����û���õġ�

������ͨ�û���˵�����������Ҫ֪���Ĺ���DDR��DDR2��DDR3�ڴ��һ�С����ڸ��û���˵��������һ���ص㣺�ڴ��ʱ����ӳ١�

�ڴ�ʱ���������

����ʱ���ԭ�����������������������ͬ���ڴ�ģ����Դﵽ��ͬ������ˮƽ��Ϊʲô����������ͬ��ʱ���������е�����»�������������

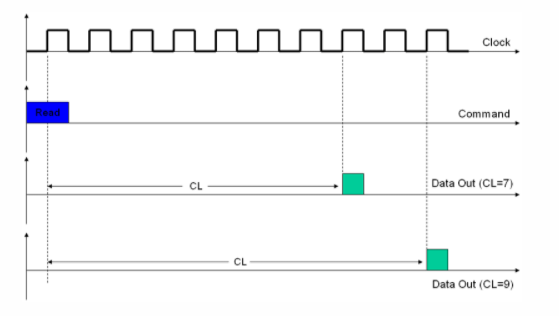

ʱ����������ڴ�оƬ���ڲ���ij�µ��ӳ�ʱ�䡣������һ�����ӡ����ǵ��������IJ�����������ΪCAS Latency����CL�� ������ʱ�䡱������ѡͨ�ӳ١����������������ڴ�ģ���ڷ���CPU���������ʱ���ӳٶ��ٸ�ʱ�����ڡ�һ��CLΪ9���ڴ�ģ�齫�ӳ�9��ʱ���������ṩ��������ݣ���һ��CLΪ7���ڴ�ģ�齫�ӳ�7��ʱ���������ṩ���ݡ���Ȼ������ģ���������ͬ��ʱ���������У����ڶ���ģ����ٶȻ���죬��Ϊ�����ȵ�һ��ģ�����ؽ�������.������ⱻ��Ϊ ���ӳ١�������������ͼ�п����ģ������ģ���CLΪ7��

�ڴ�ʱ����ͨ��һϵ�����ָ����ģ����磬4-4-4-8,5-5-5-15,7-7-7-21��9-9-9-24����Щ���ֱ�ʾ�ڴ�ִ��ij����������ʱ��������������ԽС���ڴ���ٶ�Խ�졣��ͼ�����ڴ�ģ���ʱ��Ϊ7-7-7-18����ͼ�������ڴ�ģ���ʱ��Ϊ8-8-8-24��

��Щ��������ʾ�IJ������¡�CL -tRCD -tRP -tRAS -CMD��Ҫ�������ǣ����ס���洢�����ڲ���֯��һ���������ݴ洢���к��еĽ��㴦��

CAS�ӳ�(CL)

CAS Latency(CL)�����������ڴ�����������������ڴ潫�ӳٶ��ٸ�ʱ����������������������ݣ�һ��CL=7���ڴ潫�ӳ�7��ʱ���������������ݣ���CL=9���ڴ潫�ӳ�9��ʱ��������ִ��ͬ���IJ�������ˣ���������ͬʱ���������е������ڴ�ģ����˵��CLֵ��͵��Ǹ�ģ�����졣

��ע�⣬�����ʱ���������ڴ�ģ������ʱ��ʵ��ʱ�����ʣ����ʱ�����ʵ�һ�롣����DDR��DDR2��DDR3�ڴ���ÿ��ʱ�������ڿ����ṩ�������ݣ�������ǵĶʱ��������ʵ��ʱ�����ʵ�������

��ͼ�У����Կ���CL�Ĺ���ԭ�������Ǿ����������ӣ�һ����CL=7���ڴ�ģ�飬һ����CL=9���ڴ�ģ�顣��ɫ�������һ�� "�� "�����

���ǵ���������ͬ��ʱ�����������У�CL=7���ڴ潫��CL=9���ڴ��ӳ����22.2%��

���������Լ�����ڴ��ӳٵ���ʼ�������ݵ�ʱ�䣬ÿ��ʱ�����ڵ����ڿ���ͨ����ʽ���ɼ��������

T = 1 / f

��ˣ�DDR3-1333�ڴ���1333 MHz��666.66 MHzʱ�ӣ������е�ÿ��ʱ�����ڵ�����Ϊ1.5 ns��ns=���룻1 ns=0.000000001 s�������ԣ����DDR3-1333�ڴ����CL=7�Ļ������ӳ�10.5 ns��ʼ�������ݣ����CL=9�Ļ������ӳ�13.5 ns��

RAS��CAS�ӳ�(tRCD)

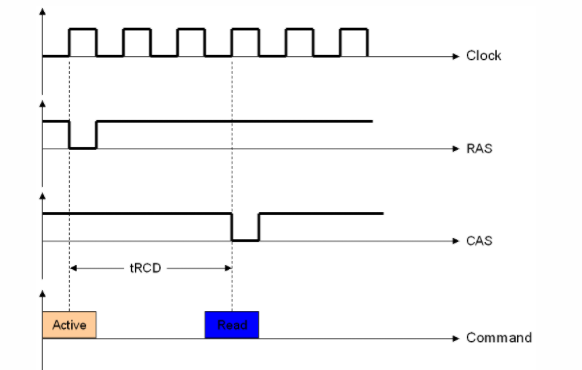

ÿ���洢оƬ�ڲ������Ծ������ʽ��֯�ġ���ÿһ�к�ÿһ�еĽ���㣬������һ��С���ݣ�����洢 "0 "�� ��1���C���ݡ��ڴ洢���ڲ������ʴ洢���ݵĹ�����ͨ���ȼ����У��ټ���������ɵġ����ּ�����ͨ�����������ź�����ɵģ��������źű���ΪRAS(Row AddressStrobe)��CAS(Column Address Strobe)���������ź�֮���ʱ����Խ��Խ�ã���Ϊ���ݻᱻ����ض�ȡ��RAS��CAS�ӳٻ�tRCD�������ʱ�䡣����ͼ������˵������һ�㣬��ʾ��һ���ڴ棬RCD=3��

�������������ģ�RAS��CAS�ӳ�Ҳ�� "� "����� "�� "�� "д "����֮���ʱ����������

��CAS Latencyһ����RAS��CAS Delay�Ĺ���ԭ�����ڴ�ʵ��ʱ�ӣ��DZ��ʱ�ӵ�һ�룩���ò���Խ�ͣ��ڴ��ٶ�Խ�죬��Ϊ��������ؿ�ʼ��ȡ��д�����ݡ�

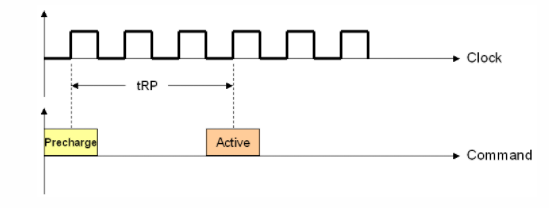

RASԤ���(tRP)

���ڴ���ȡ�����ݺ���Ҫ����һ����ΪPrecharge������ر�����ʹ�õ��ڴ��У������µ��б����RASԤ���ʱ��(tRP)��ָ��Precharge�����һ��Active������Է�����ʱ�䡣����֮ǰ���˽�ģ�Active����������һ������д���ڡ�

��ͼ�У�������tRP=3�Ĵ洢��Ϊ����

����������һ����RASԤ������ڴ�ʵ��ʱ�ӣ��DZ�עʱ�ӵ�һ�룩һ�������������Խ�ͣ��ڴ���ٶȾ�Խ�죬��Ϊ�������ط���Active���

����������������һ�У��ӷ���Precharge���ʵ�ʵõ�����֮���ʱ�佫��tRP + tRCD + CL��

��������

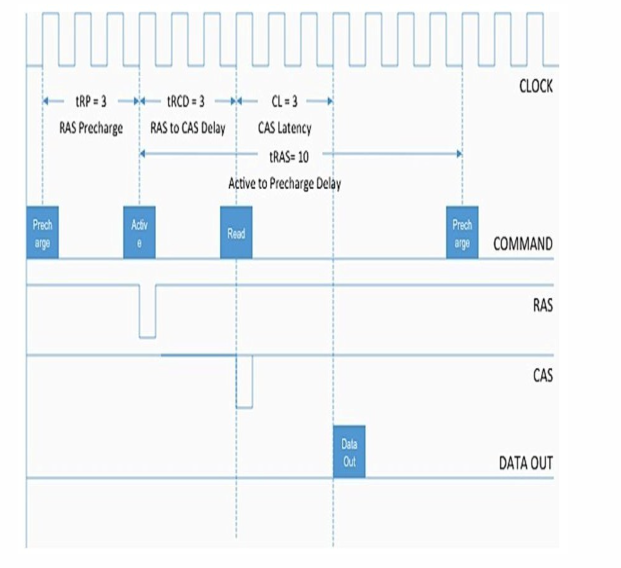

��������������������������Active to Precharge Delay��tRAS����Command Rate��CMD��������������һ�����������������ڴ�ʵ��ʱ�ӣ����ڴ��ʾʱ�ӵ�һ�룩�йء���Щ����Խ�ͣ��ڴ���ٶȾ�Խ�졣

Active��Ԥ����ӳ٣�tRAS��������һ��Active�������tRAS������ܷ�����һ��Precharge������ԣ���������������ڴ��ʱ���Կ�ʼ��ȡ����д�룩��ͬ���С�

�������ʣ�CMD��������ָ�ڴ�оƬ�ӱ����ͨ��CS-оƬѡ��-���ţ����������ڴ淢���κ����������ʱ�䡣�ò���������ĸ ��T�������ܵ�ֵ��1T��2T���ֱ��ʾһ��ʱ�����ڻ�����ʱ�����ڡ�

Ϊ�˸��õ����⣬��ͼΪʱ�����Ϊ3-3-3-10�����裩�Ĵ洢����ʱ��ͼ��

�����µ�������ǿ��Խ�ʱ������ܽ����¡�

-

CAS�ӳ�(CL)��ָ����ȷ�����Ѿ�������£���DRAM�ж�ȡ��һ���ڴ�λ�����ʱ�䡣

-

��û���κλ�е�����£���DDR�ж�ȡ��һ���ڴ�λ��ʱ��ΪtRCD+CL��

-

��һ��û�л�е�DRAM�ж�ȡ��һ���ڴ�λ��ʱ����tRP + tRCD + CL��

-

�ӷ��� "� "������� "Ԥ��� "���������ʱ��������ΪtRAS��

��Щ��Ϣ�����Դ���ͼ�еõ���