FPGA――NIOS-II开发入门

-

- 一、硬件部分设计

-

- 1.1 创建工程

- 1.2 进入Qsys 中进行软核的设计

-

-

- 1.2.1 点击 `Tools->Qsys`,进入`Qsys`

- 1.2.2 `File->save`,保存为`kernel.qsys`

- 1.2.3 双击`clk_0`,设置clock时钟为50M

- 1.2.4 添加CPU和外围器件

- 1.2.5 完成 Qsys 设计的后续工作

- 1.2.6 加入 Quartus II IP File 文件

- 1.2.7 进行逻辑连接和生成管脚

-

实验内容

使用 FPGA 资源搭建一个简单 Nios II 处理器系统,具体包括:

(1) 在 Quartus Prime中建立一个工程;

(2) 使用 PD 建立并生成一个简单的基于 Nios II 的硬件系统;

(3) 在 Quartus Prime工程中编译基于 Nios II 的硬件系统并生成配置文件.sof;

(4) 在 Nios II SBT 中建立对应硬件系统的用户C/C++工程,编写一简单用户程序,在 Nios II SBT 中编译程序生成可执行文件.elf;

(5) 将配置文件.sof和可执行文件.elf 都下载到 FPGA 进行调试运行

一、硬件部分设计

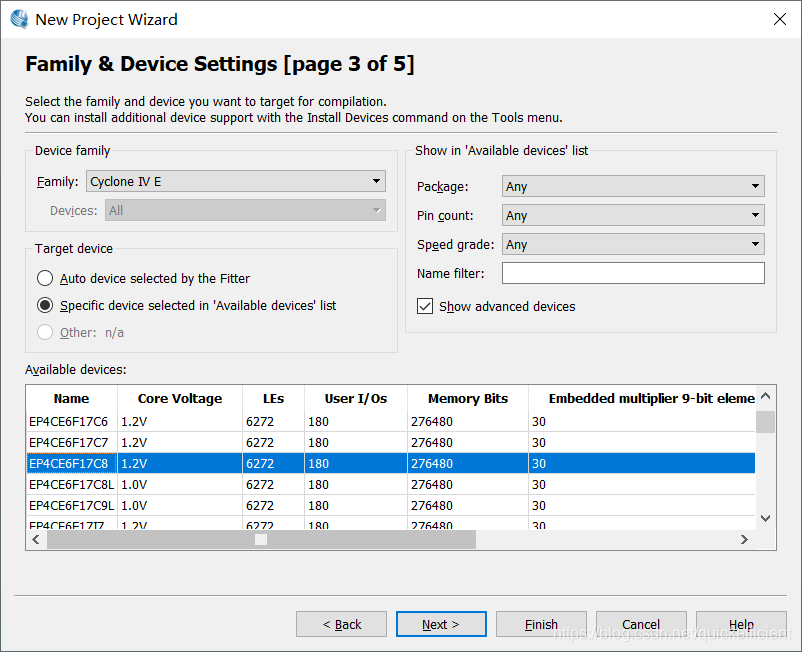

1.1 创建工程

详细步骤请参照另一篇博客:Quartus使用基础――D触发器仿真与时序波形验证

1.2 进入Qsys 中进行软核的设计

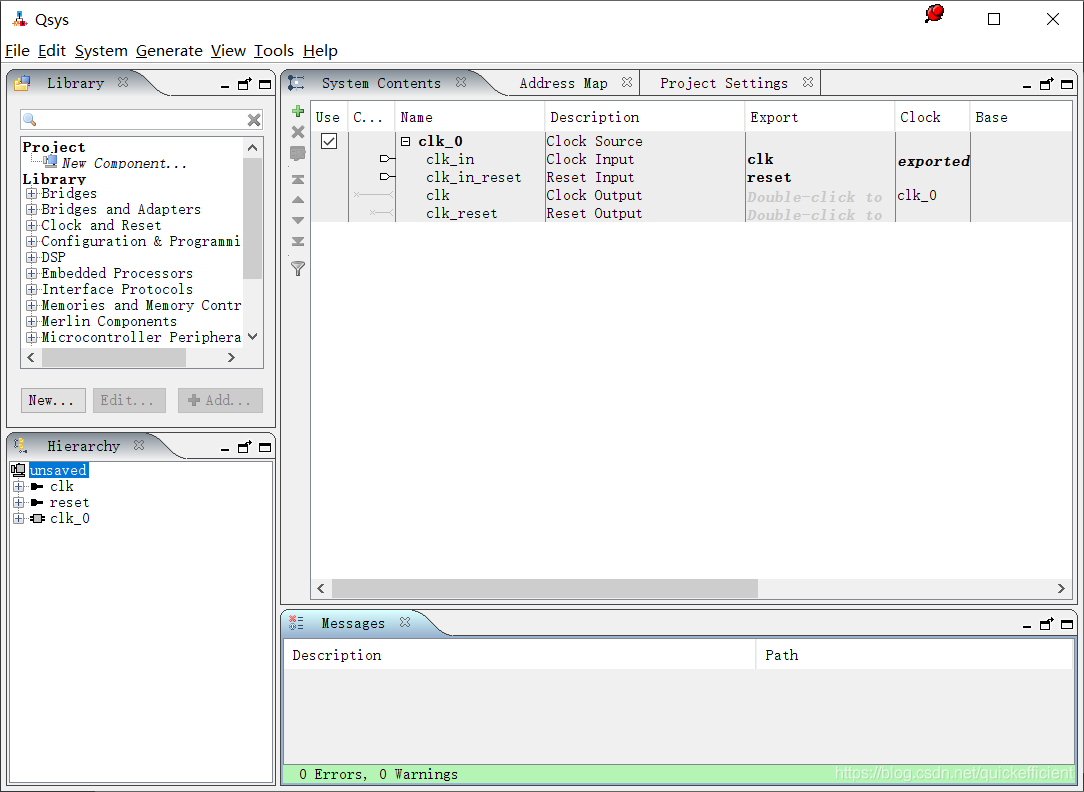

1.2.1 点击 Tools->Qsys,进入Qsys

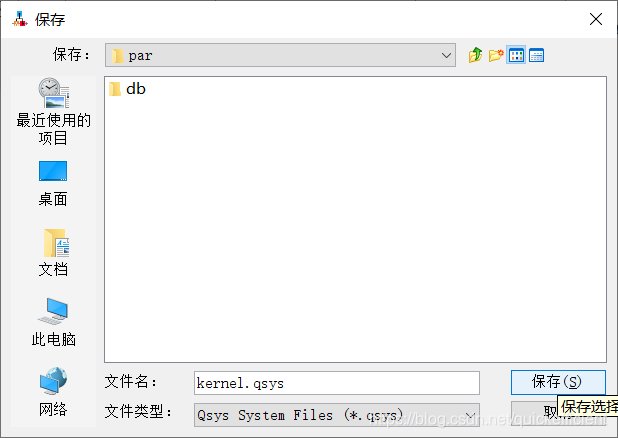

1.2.2 File->save,保存为kernel.qsys

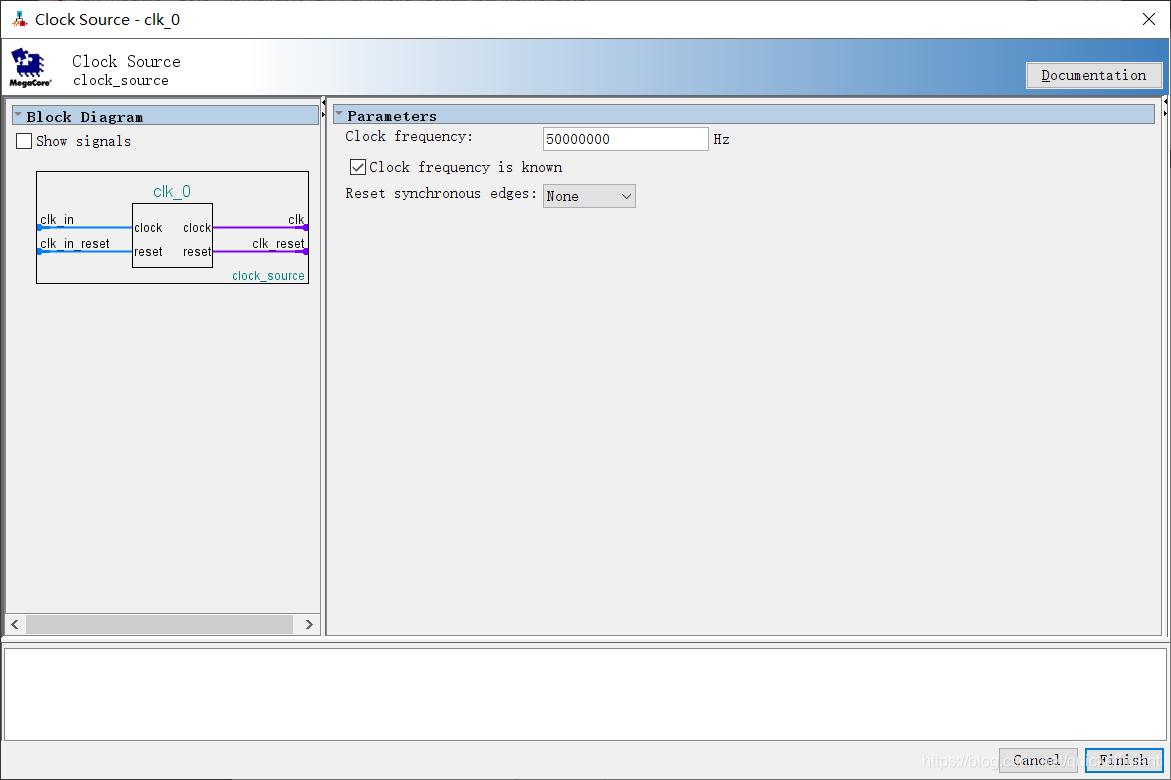

1.2.3 双击clk_0,设置clock时钟为50M

1.2.4 添加CPU和外围器件

4.1 添加 Nios II 32-bit CPU

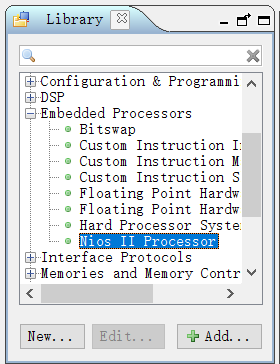

a 选择如下Nios II Processor,Add

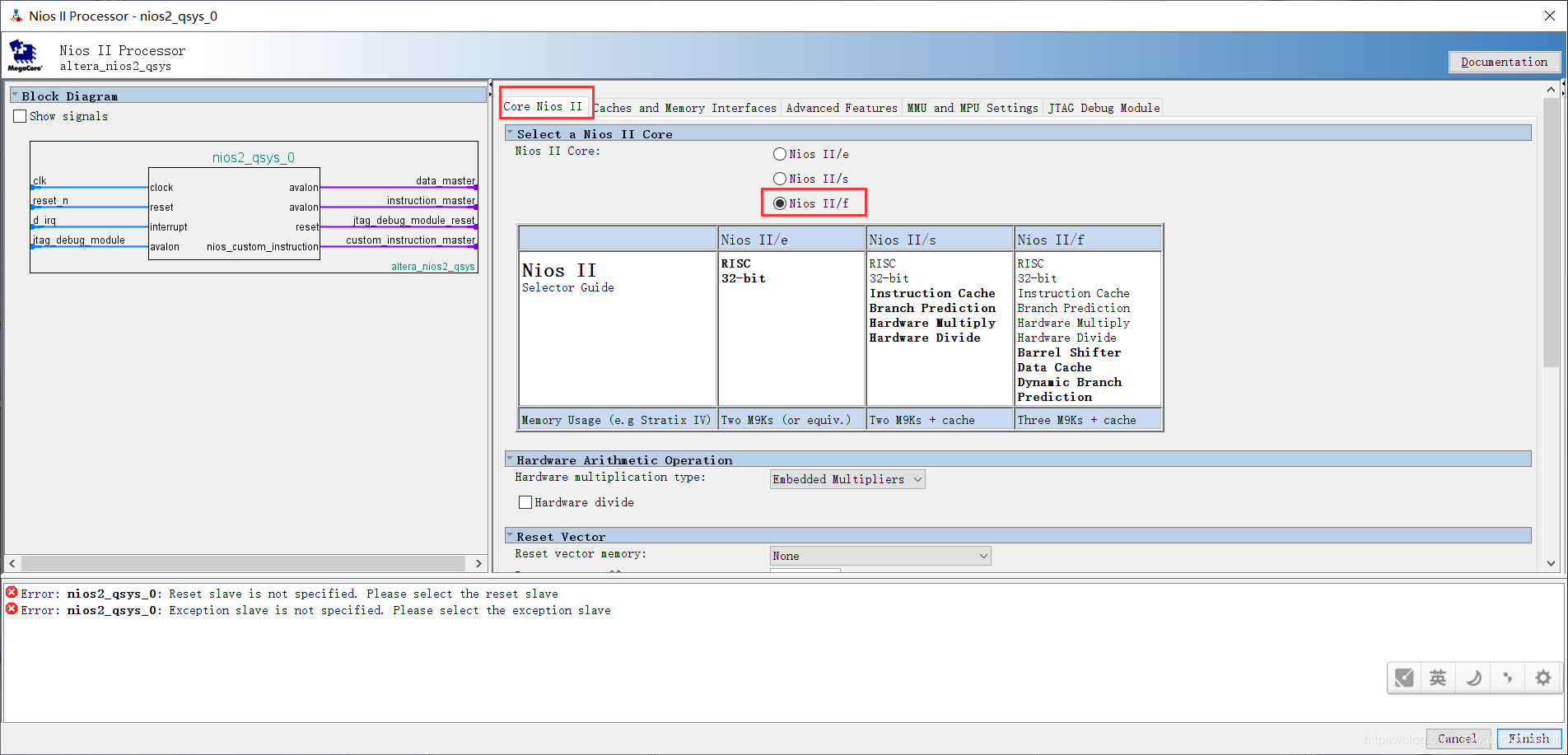

b 在 Core Nios 栏中选择 Nios II/f 选项,其他保持默认选项

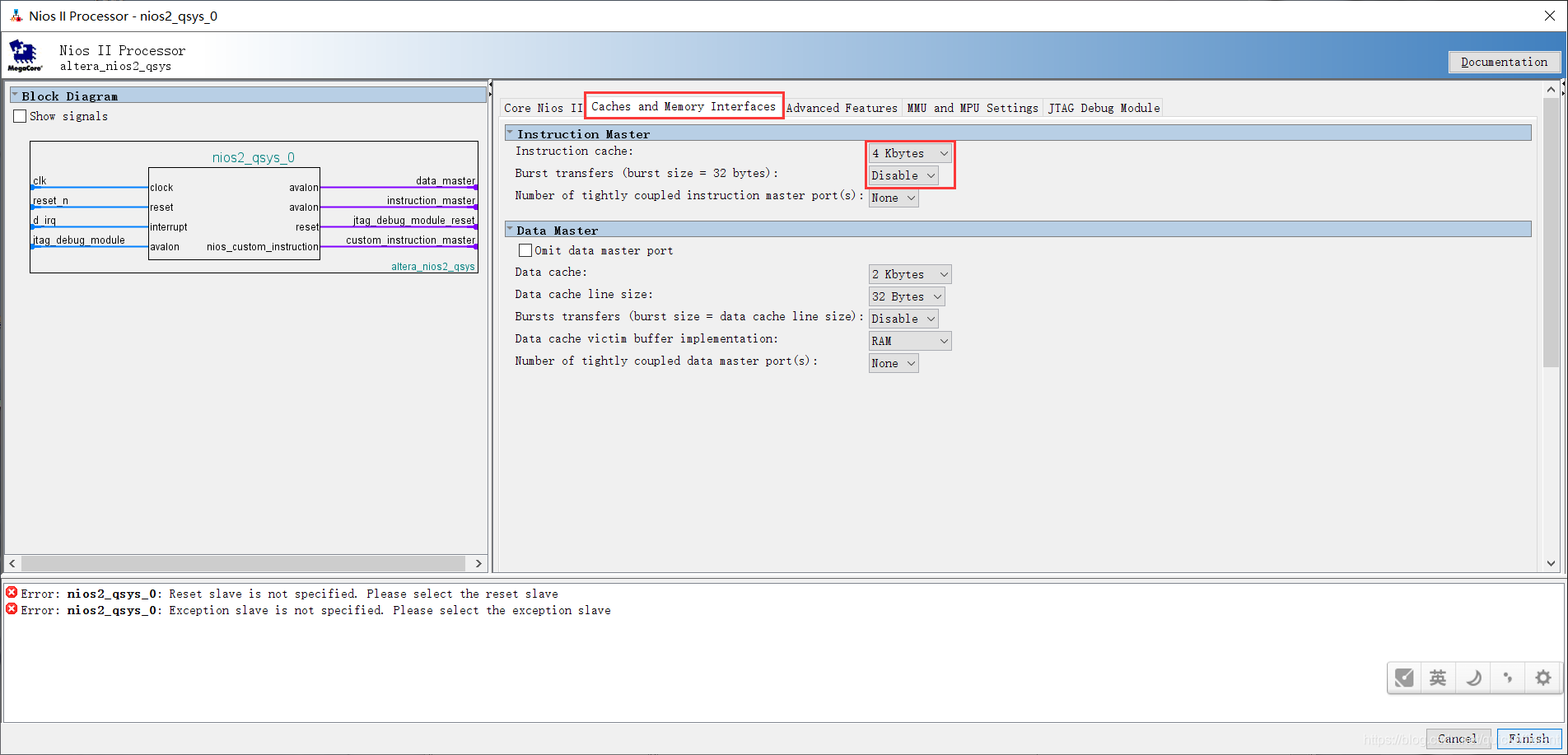

c 在Caches and Memory Interfaces标签栏中保持默认设置(Instruction Cache 选择4Kbytes)

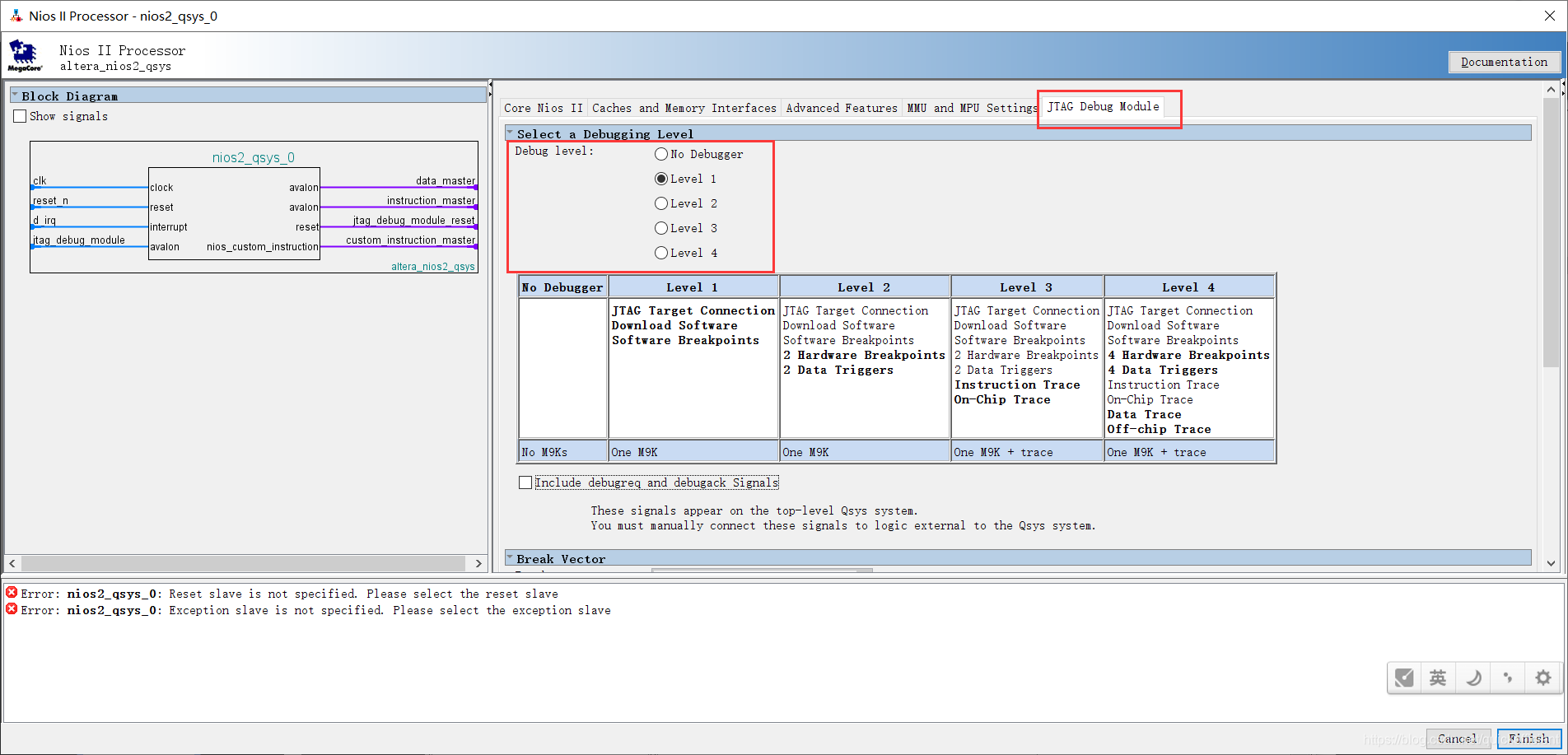

d 在”JTAG Debug Module”标签栏中保持默认设置(注意Debug Level选择Level 1)

e Finish

f 将 nios2_qsys_0 重命名为 cpu,右键Rename即可重新命名

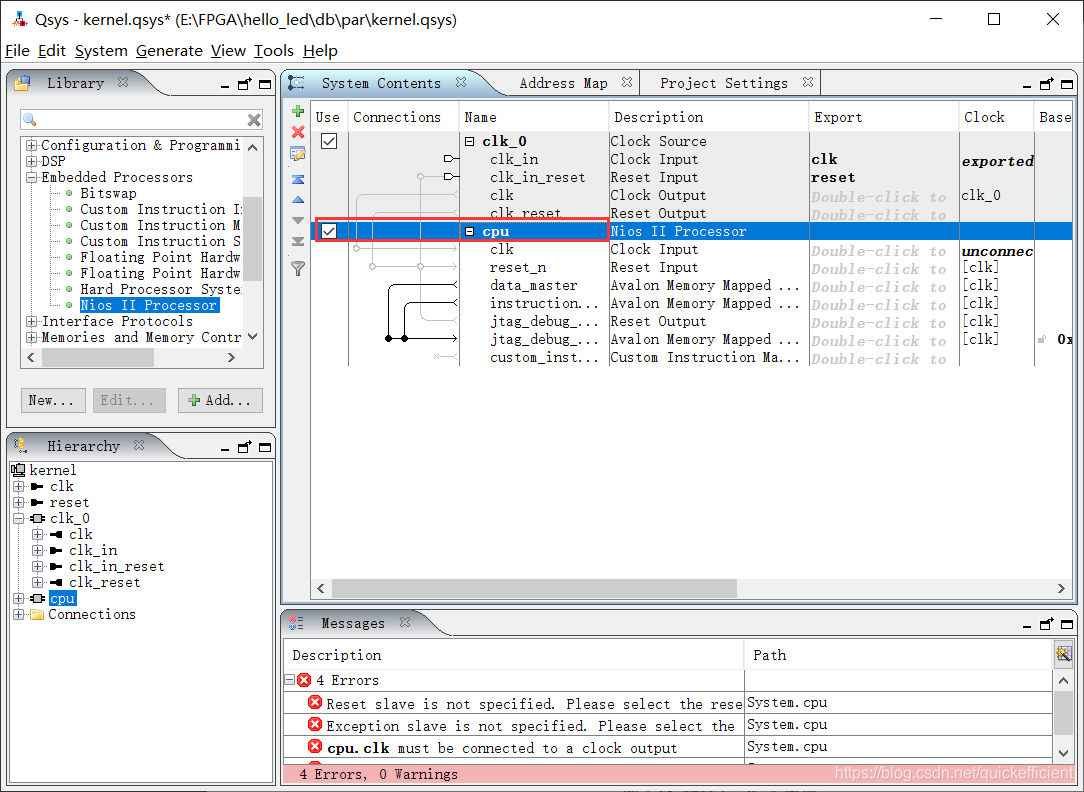

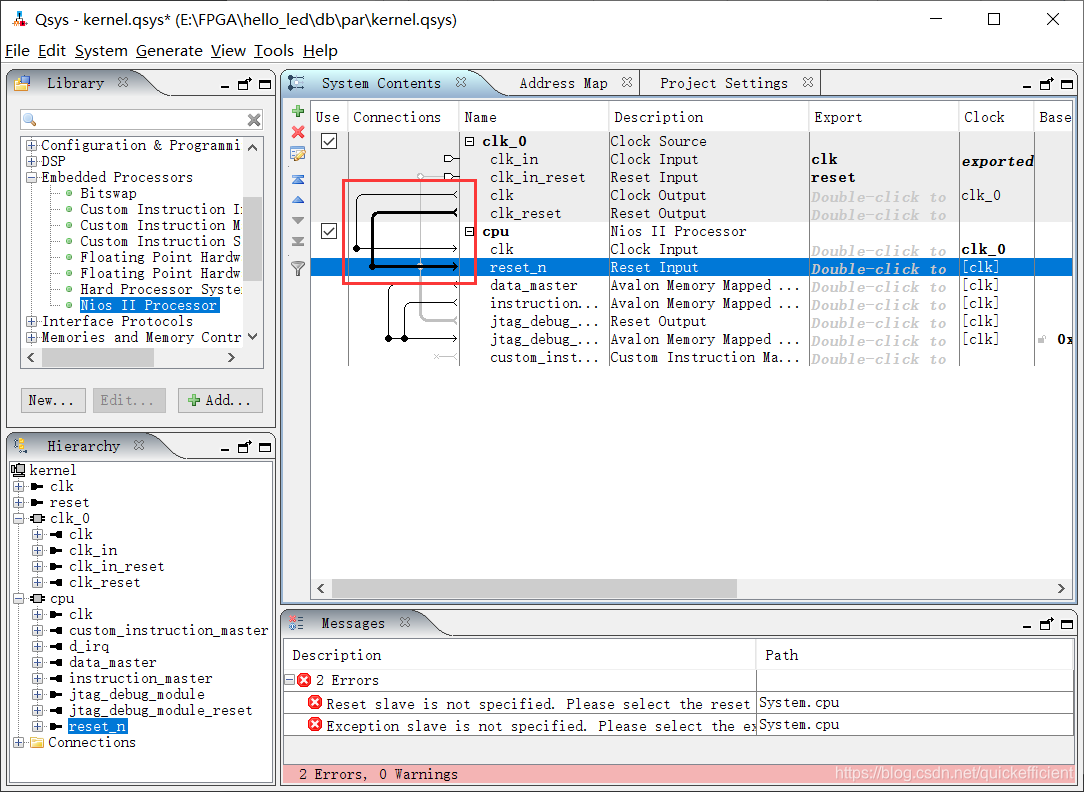

g 将 cpu 的 clk 和 reste_n 分别与系统时钟 clk_0 的 clk 和 clk_reset 相连

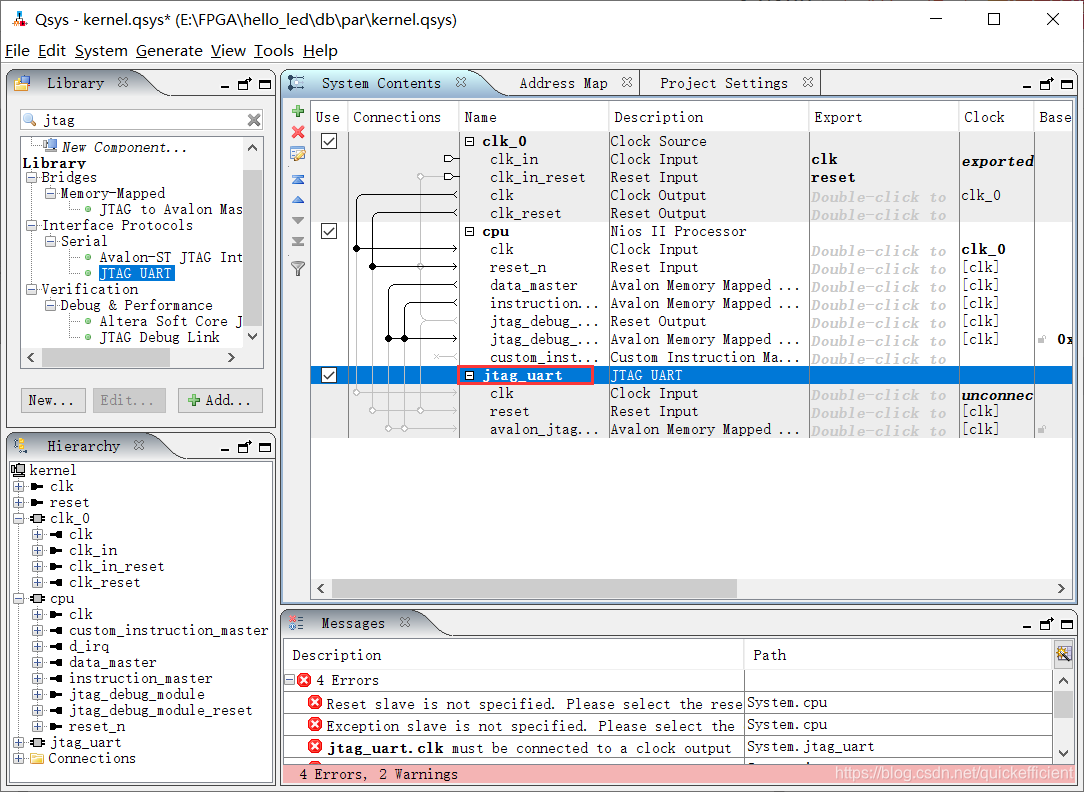

4.2 添加 jtag uart 接口

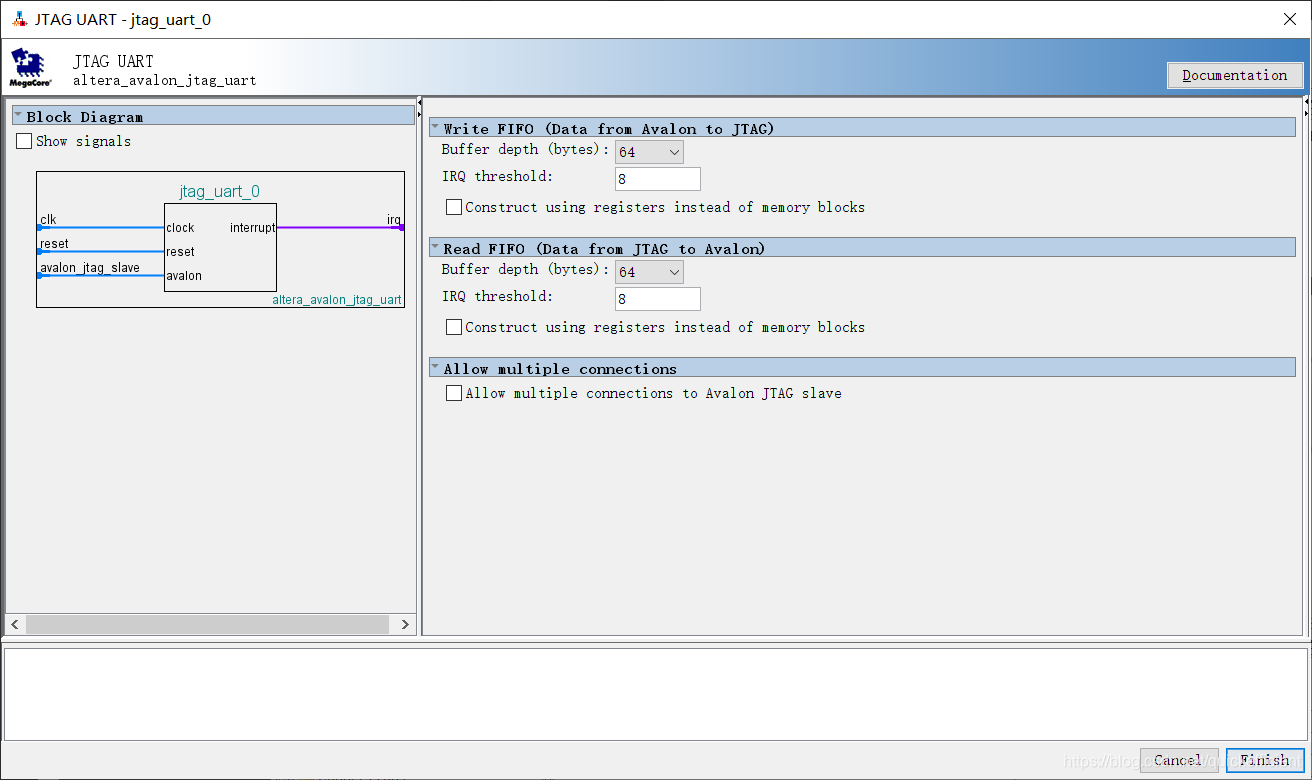

添加 jtag uart 接口。jtag uart 接口是 Nios II 嵌入式处理器新添加的接口元件,通过内嵌在 Intel FPGA 内部的 JTAG 电路,可以实现在 PC 主机与Qsys 系统之间进行串行字符流通信。

a 查找窗口输入 jtag 找到JTAG UART ,然后点击Add

b Finish

c 将 jtag-uart_0 重命名为 jtag-uart,右键Rename即可重新命名

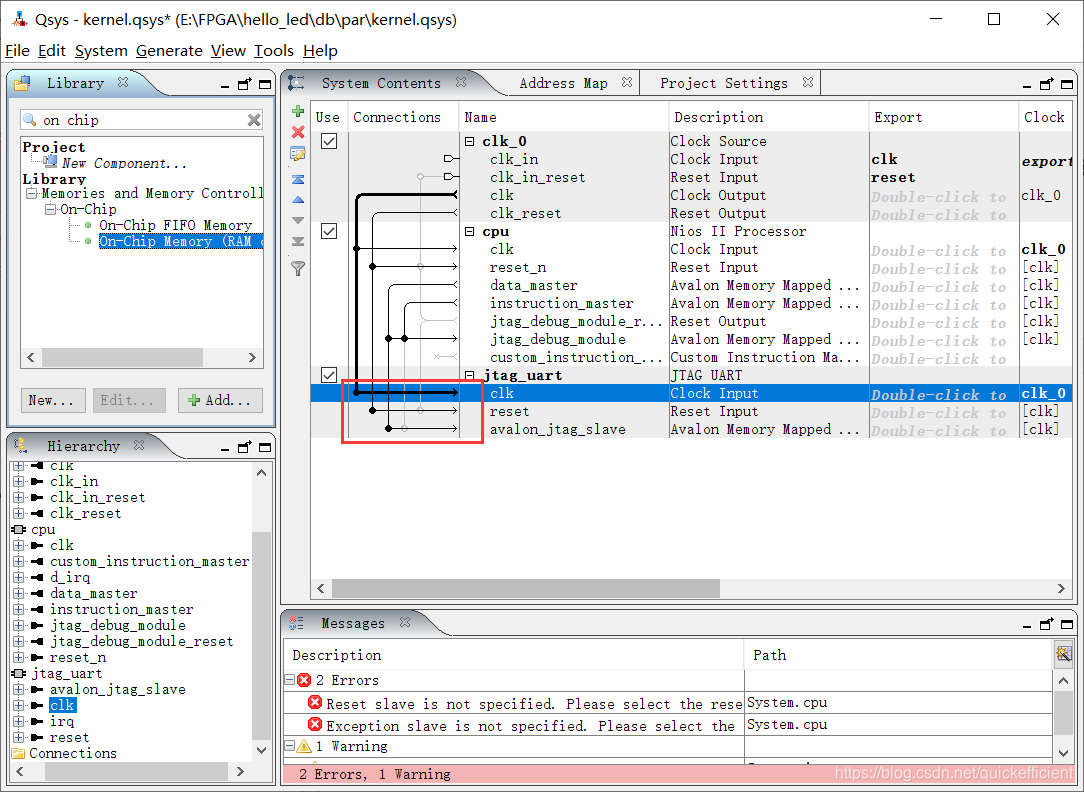

d 进行 clk、reset 以及 master-slave 的连线

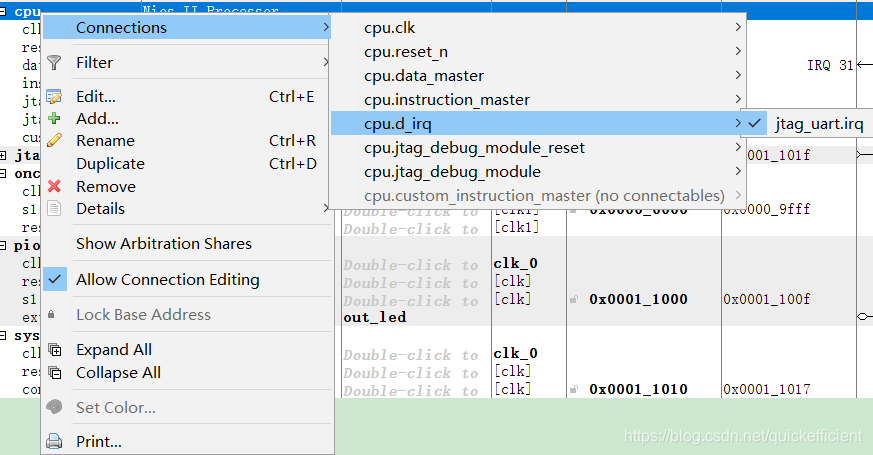

e 进行中断 irq 连线

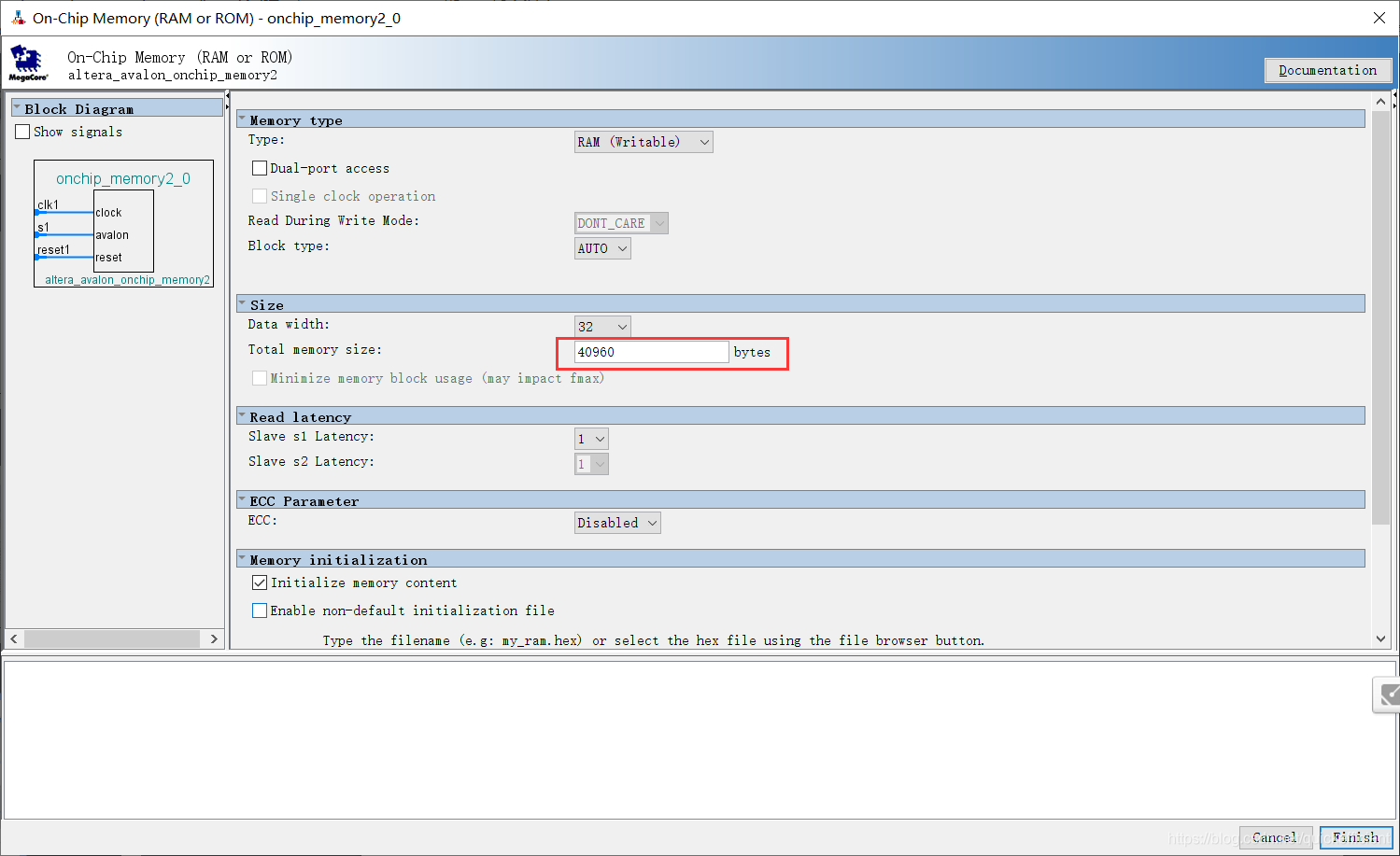

4.3 添加片上存储器 On-Chip Memory(RAM)核

a 查找窗口输入 On Chip 找到On-ChipMemory(RAM or ROM)后点击 Add

b 在Size栏中的Total memory size窗口中输入 40960(即片上内存的大小为 40KB)

c Finish

d 将 onchip_memory2_0 重命名为 onchip_ram,右键Rename即可重新命名

e 进行时钟、数据端口、指令端口的连接

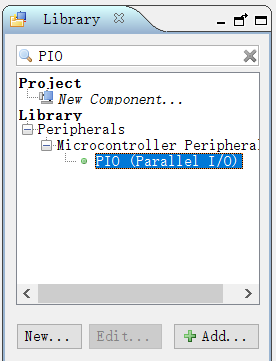

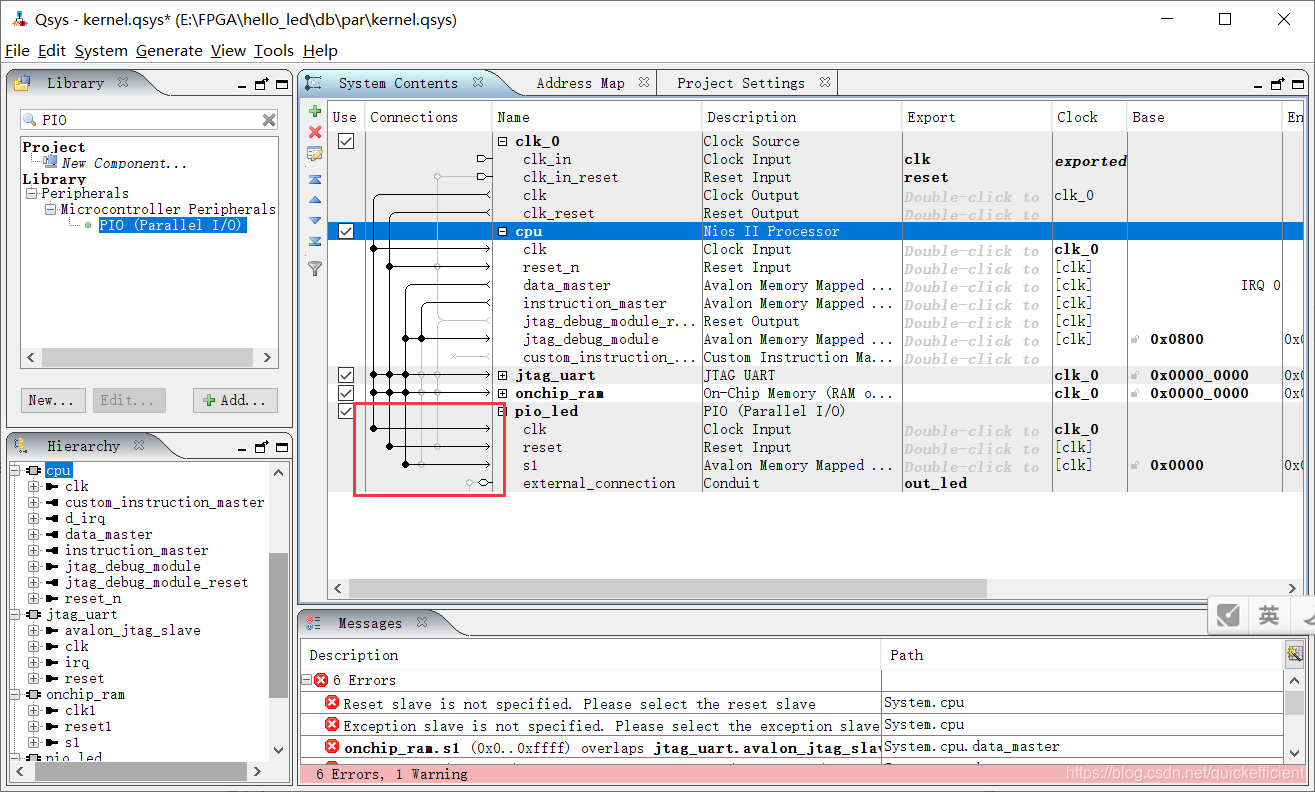

4.4 添加 PIO 接口

a 查找窗口输入 pio 找到PIO后点击 Add

b 将pio_0 改名为 pio_led。然后点击pio_led的external_connection行中的Export列(列中有灰色的Click to export),命名为out_led

c 进行时钟、数据端口、指令端口的连接

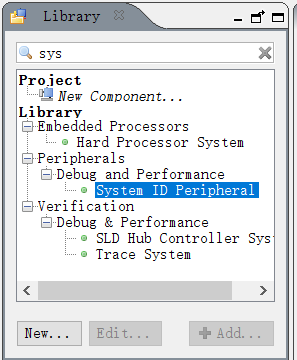

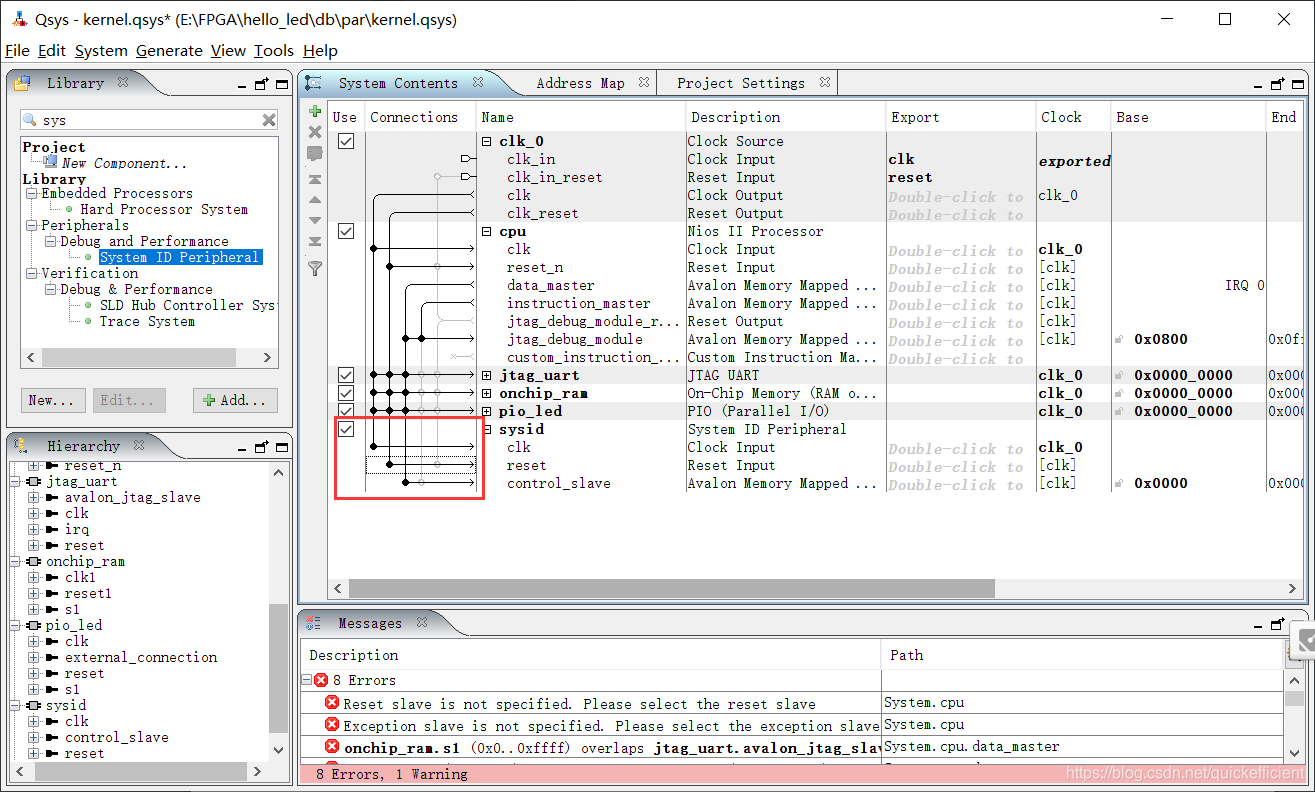

4.5 添加片 System ID Peripheral 核

a 查找窗口输入 sys 找到System IDPeripheral后点击 Add

b Finish

c 将 sysid_qsys_0 改名为 sysid

d 进行时钟、数据端口的连接

1.2.5 完成 Qsys 设计的后续工作

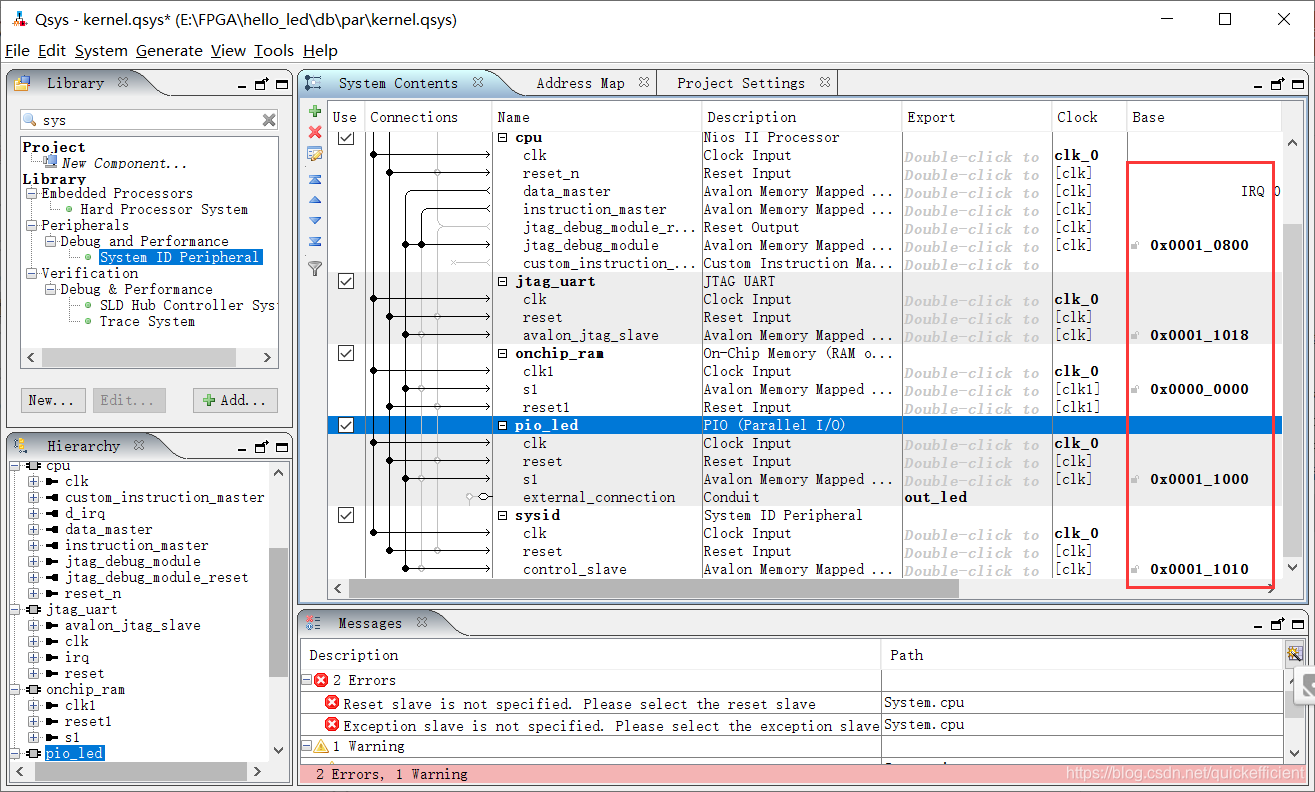

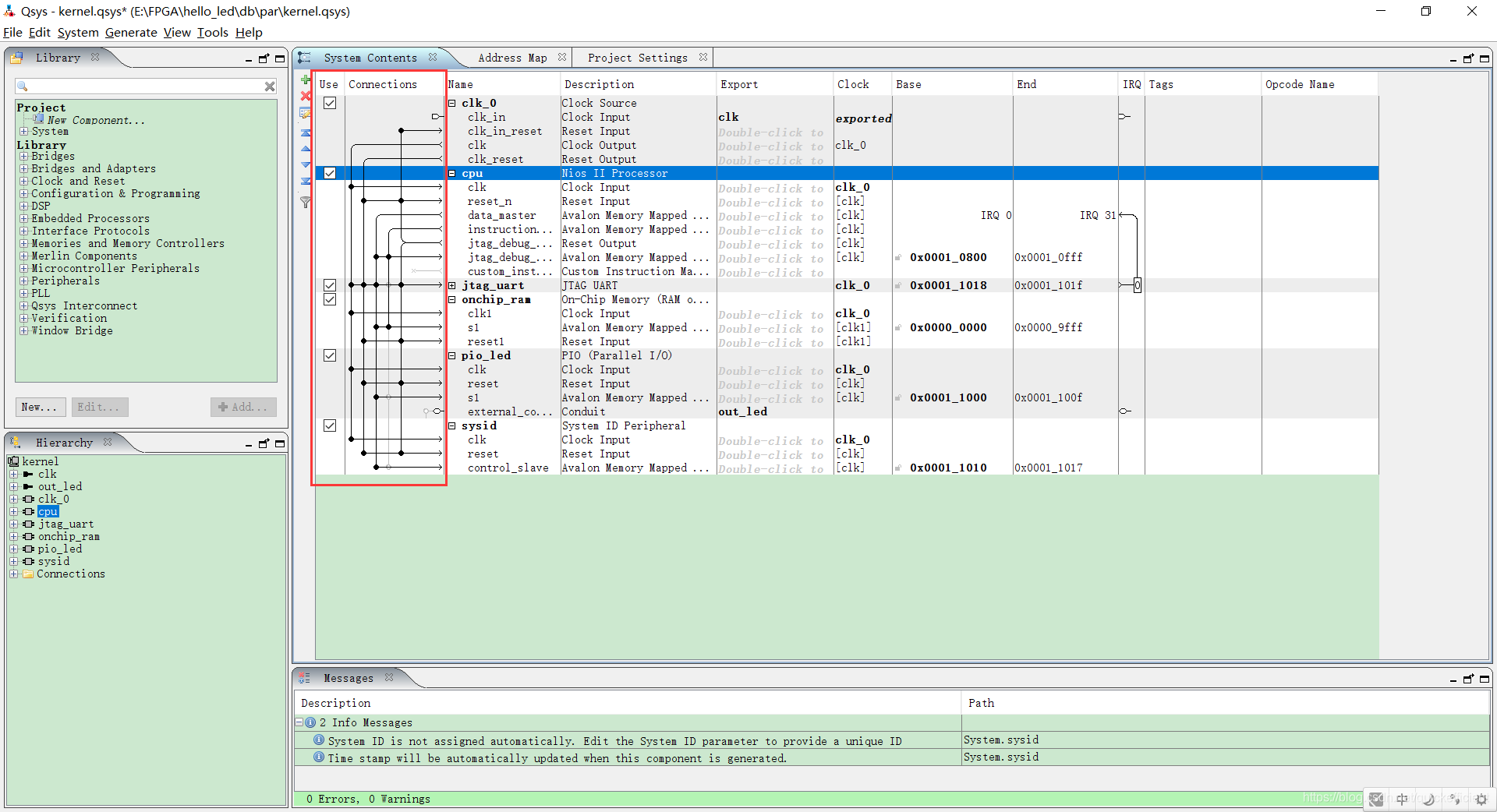

5.1 基地址分配:点击 Qsys 主界面菜单栏中的System下的Assign Base Addresses,这样将不会出现重复的地址

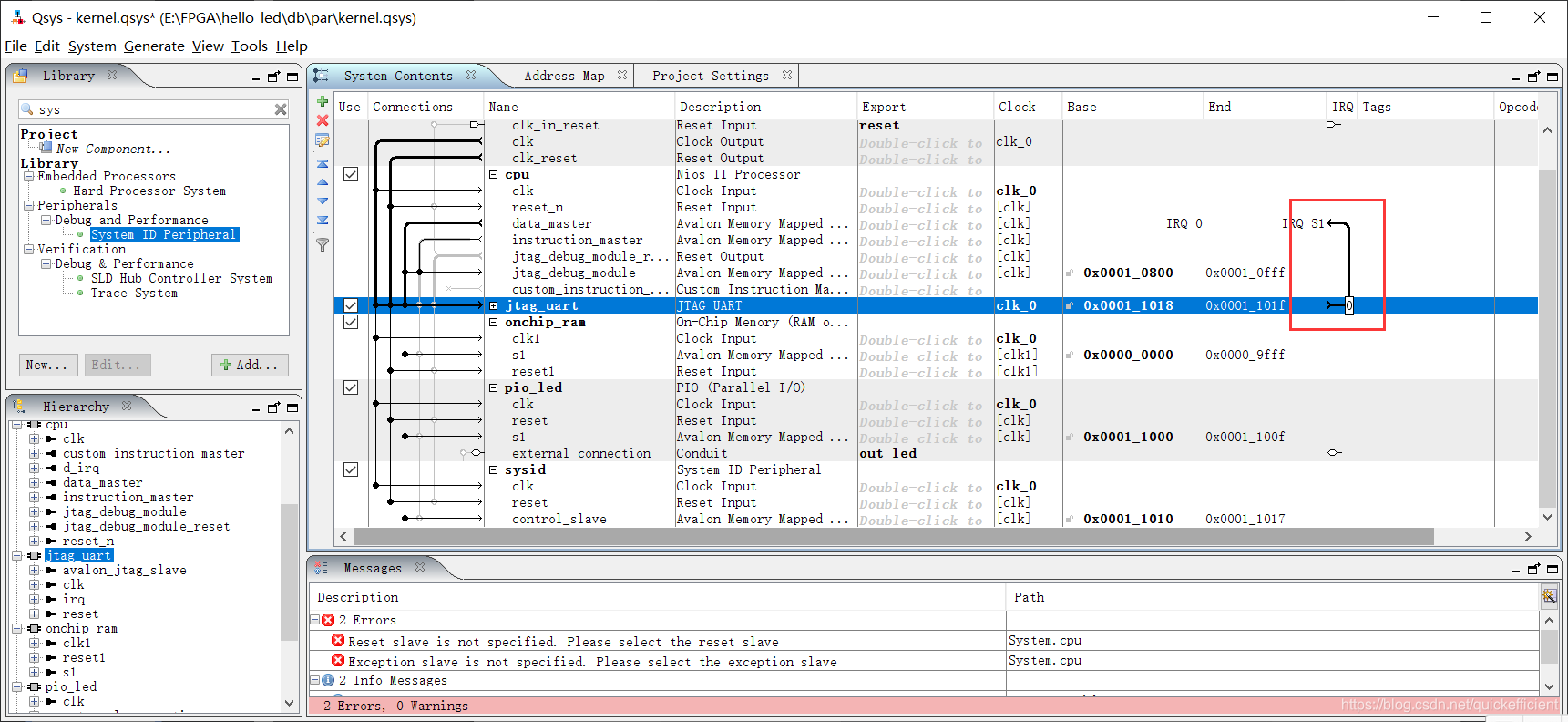

5.2 分配中断号:在IRQ标签栏下点选Avalon_jtag_slave和 IRQ 的连接点就会为jtag_uart核添加一个值为 0 的中断号

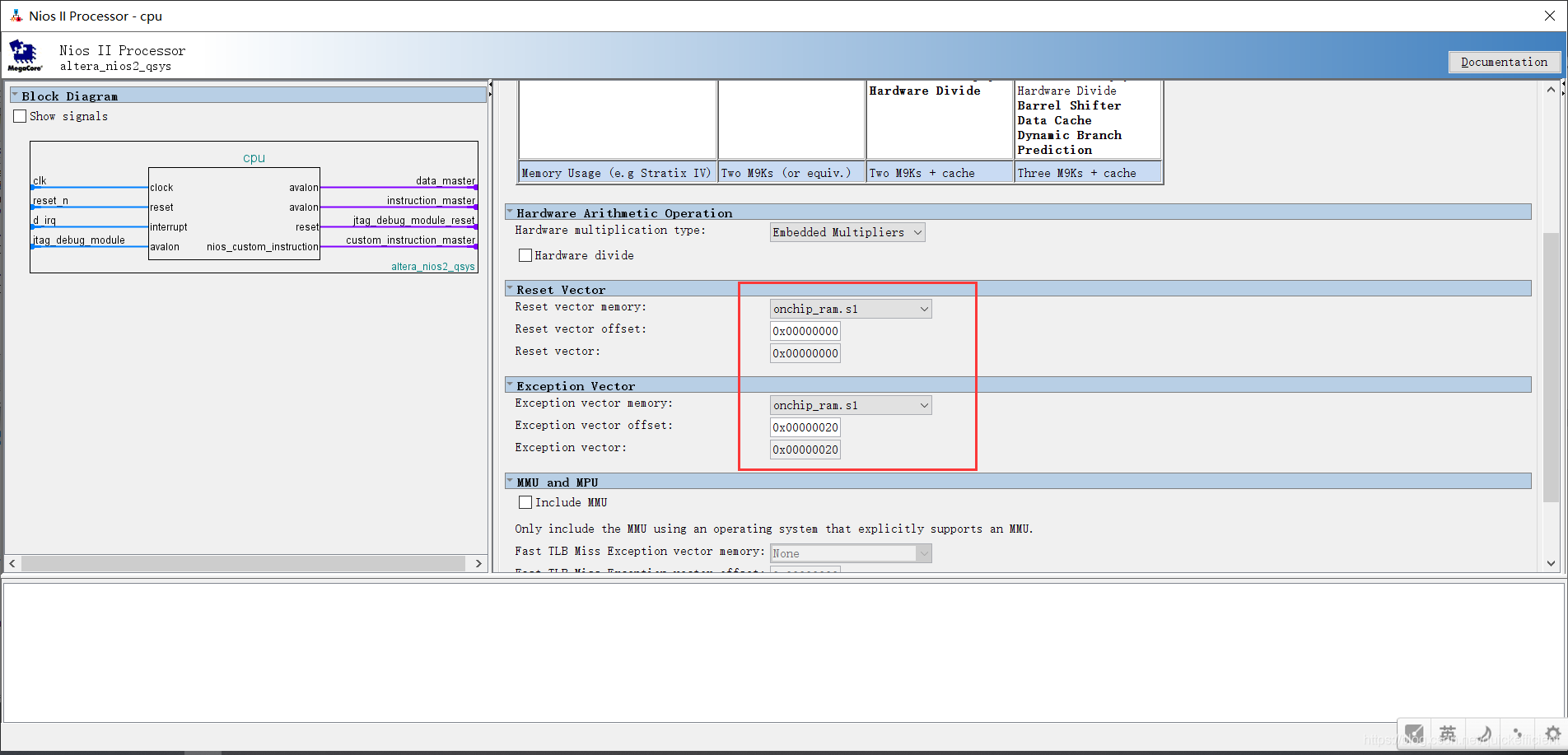

5.3 )指定 NIos II 的复位和异常地址:从System Contents标签栏

双击建立好的 cpu 进入 Nios II Processor 的配置界面,配置 Reset Vector 和 ExceptionVector 为onchip_ram.s1,点击 Finish

5.4 点击 Qsys 主界面菜单栏中的”System”下的”Create Global Reset Network”。完成后会自动连接所有复位端口

这是最终完成图( 请仔细对照此图,否则后面无法进行)

注意:这里有一个cpu的irq与jtag_uart的连接

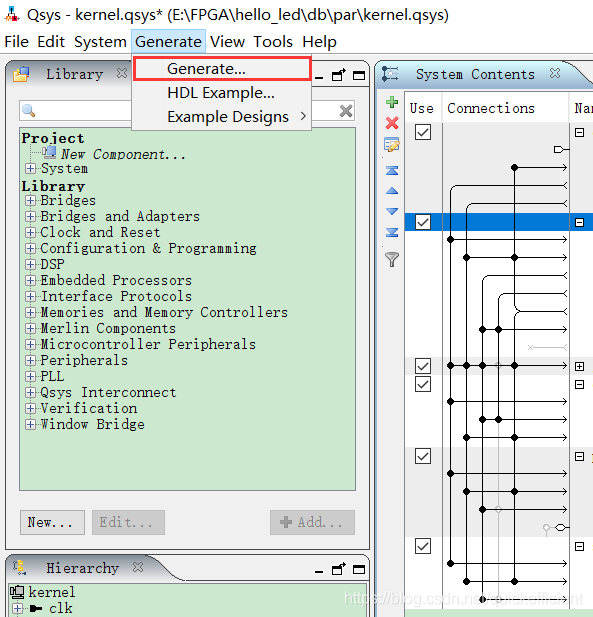

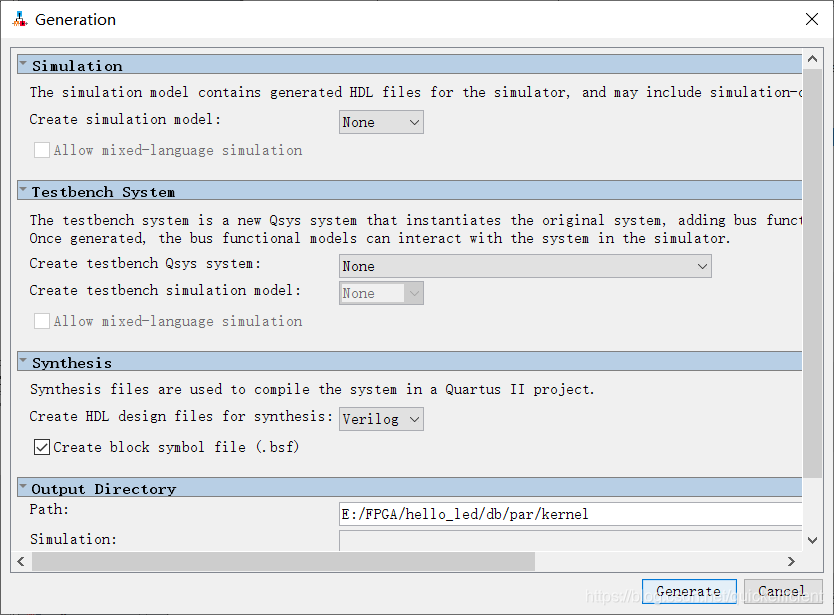

5.5 生成 Qsys 系统:点选Generation标签栏中 Generate 按钮生成 Qsys 系统

5.6 如果提示是否保存.qsys 文件,请选择保存。完成后会显示类似如下窗口:

点击 Close 后关闭窗口后,再关闭 Platform Designer 主界面。

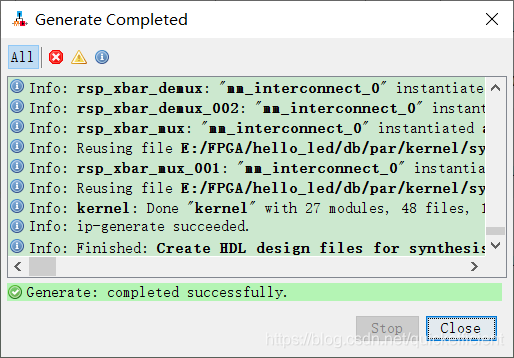

5.7 File->New->Block Diagram/Schematic File,在空白处双击将已生成的 kernel.bsf(E:\FPGA\hello_led\db\par)加入 top_level.bdf 中

1.2.6 加入 Quartus II IP File 文件

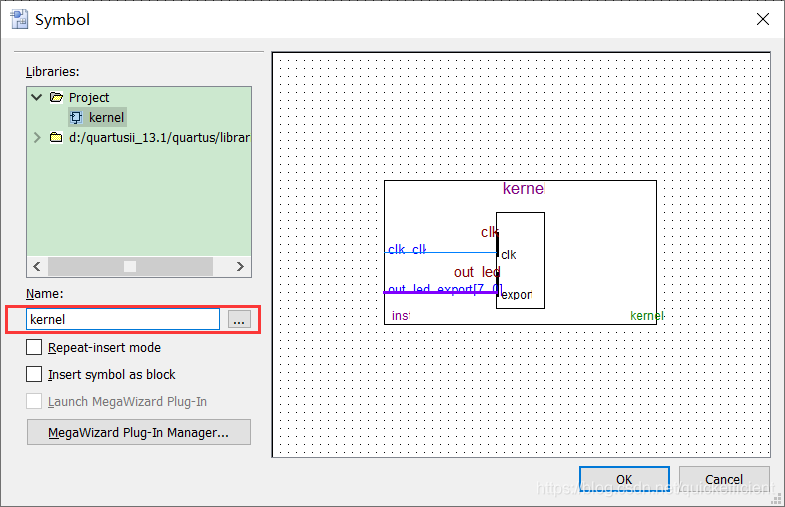

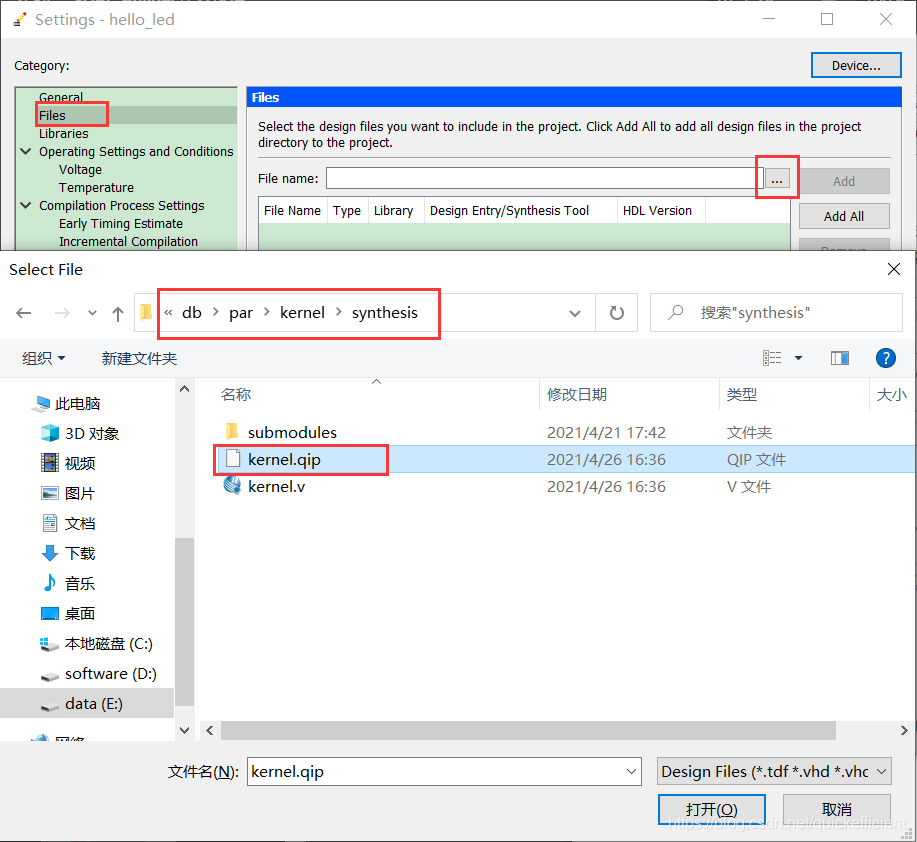

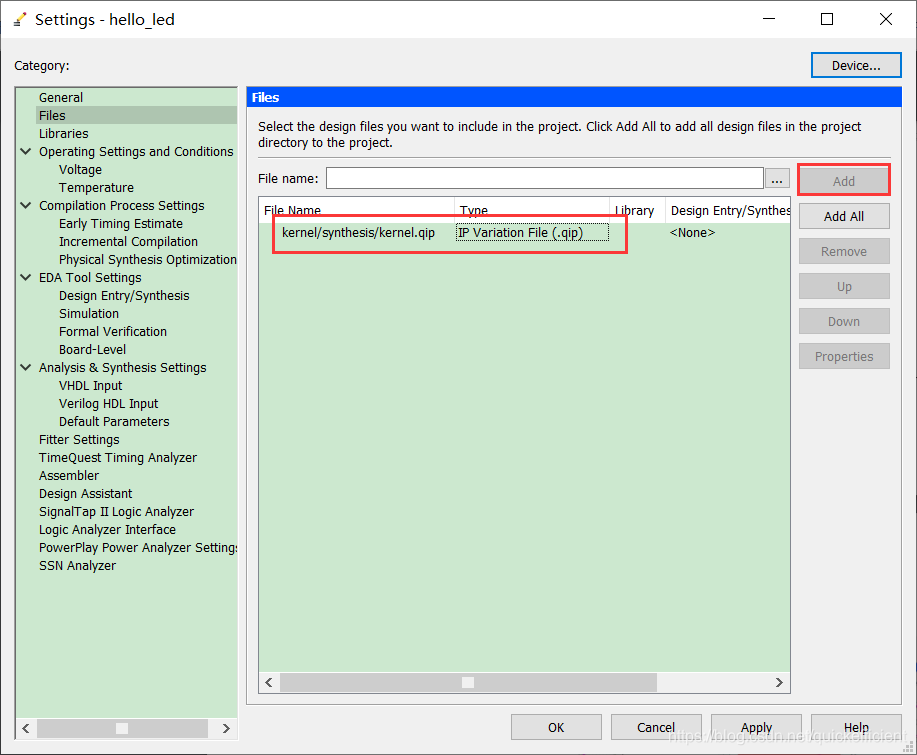

6.1 点击 Assignments->Settings,添加 kernel.qip 文件

6.2 OK后,点击Add,出现下图结果即可,再次点击OK

至此 Qsys 组件构建完成

1.2.7 进行逻辑连接和生成管脚

7.1 逻辑连接。开发板晶振为 50M,与系统默认一致,因此,这里我们不需要修改

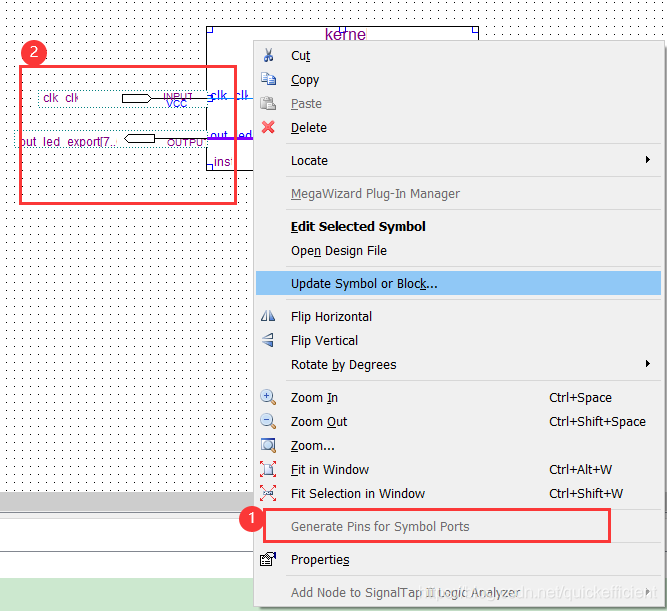

7.2 在 kernel 模块内点击鼠标右键选取 Generate Pin for Symbol Ports 生成管脚

7.3 将管脚”inclk0”改名为 clock,管脚”reset_reset_n”改名为 reset_n,

管脚 out_led_export[7…0]改为 out_led[7…0]

7.4 芯片引脚设置

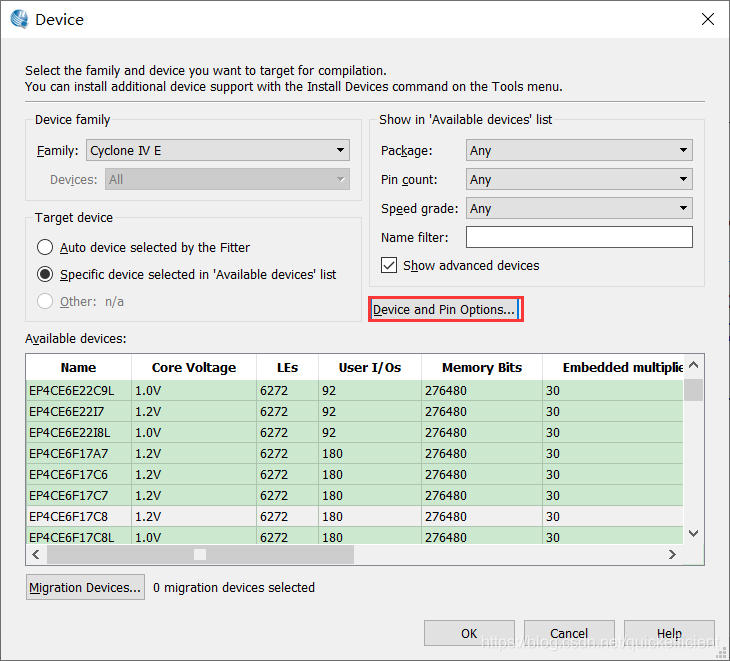

- 7.4.1 菜单里选择

Assignments->device,然后点击Device pin options

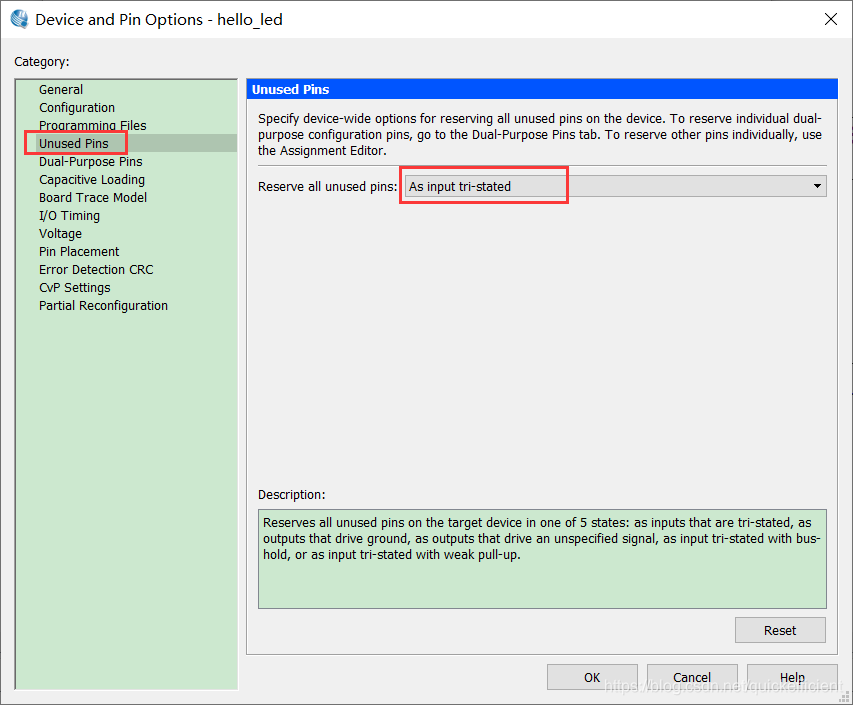

- 7.4.2 进行

unused pin设置,可能会收到外部信号的干扰,将未用引脚设置为As input tri-stated

- 7.4.3 特殊引脚设置,设置为常规引脚