注意,这里讨论的是8086CPU段地址和偏移地址的本质含义,而不是为了解决具体的问题,而在本质含义之上引申出来的更高级的逻辑意义。

不管以多少种不同的逻辑意义去看待“段地址×16+偏移地址=物理地址”的寻址模式,一定要清楚地知道它的本质含义,这样才能更灵活地利用它来分析解决问题。

如果,只拘泥于某一种引申出来的逻辑含义,而模糊本质含义的话,将从意识上限制对这种寻址功能的灵活应用。

“段地址×16+偏移地址=物理地址”的本质含义:CPU在访问内存时,用一个基础地址(段地址×16)和一个相对于基础地址的偏移地址相加,给出内存单元的物理地址。

更一般地说,8086CPU的这种寻址功能是“基础地址+偏移地址=物理地址”寻址模式的一种具体实现方案。8086CPU中,段地址×16可看做是基础地址。

下面,我们用两个与CPU无关的例子来做进一步的比喻说明。

第一个比喻说明“基础地址+偏移地址=物理地址”的思想

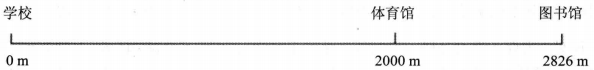

比如说,学校、体育馆,图书馆同在一条笔直的单行路上(参考下图),学校位于路的起点(从路的起点到学校距离是0米)。

学校、体育馆、图书馆的位置关系

你要去图书馆,问我那里的地址,我可以用两种方式告诉你图书馆的地址:

(1)从学校走2826m到图书馆。这2826m可以认为是图书馆的物理地址。

(2)从学校走2000m到体育馆。从体育馆再走826m到图书馆。第一个距离2000m,相对于起点的基础地址。第二个距离826m,是相对于基础地址的偏移地址(以基础地址为点的地址)。

第一种方式是直接给出物理地址2826m,而第二种方式是用基础地址和偏移地址相加来得到物理地址的。

第二个比喻进一步说明“段地址×16+偏移地址=物理地址”的思想。

我们为上面的例子加一些限制条件,比如,只能通过纸条来互相通信。你问我图书馆的地址,我只能将它写在纸上告诉你。显然,我必须有一张可以容纳4位数据的纸条,才能写下2826这个数据。

可以写下4位数据的纸条

| 2 |

8 |

2 |

6 |

可不巧的是,我没有能容纳4位数据的纸条,仅有两张可以容纳3位数据的纸条。这样我只能以这种方式来告诉你2826这个数据。

两张可以写下3位数据的纸条

| 2 |

0 |

0 |

| 8 |

2 |

6 |

在第一张纸上写上200(段地址),在第二张纸上写上826(偏移地址)。假设我们事先对这种情况又有过相关的约定:你得到这两张纸后,做这样的运算:200(段地址)×10+826(偏移地址)=2826(物理地址)。

8086CPU就是这样,一个只能提供两张3位数据纸条的CPU。

问:简述段地址和偏移地址。

答:从X地走到Y地,从Y地,走到Z地。X到Y地,也就是段地址。从Y地到Z,也就是偏移地址。两者相加,也就是实际距离。

问:为什么只拘泥于某一种引申出来的逻辑含义,而模糊本质含义的话,将从意识上限制对这种寻址功能的灵活应用?

答:学东西,不要学的太死了。一件事物,有很多答案。

问:为什么要有段地址和偏移地址?

答:

Intel 8088时代,计算机的地址总线是20位的,即可以寻址能力可以达到1M字节,但是它的ALU和寄存器都只有16位,也就是表示数的能力只能达64k,再大就逾锅了。

那怎么办呢?INTEL想了一个办法,让两个寄存器对来表示一个物理地址,比如说DS:BX,前者叫段寄存器,后者叫偏址寄存器。

由于这两个寄存器都是16位,直接相加还是不能匹配20位的地址线的访问能力,因此,INTEL公司变通了一下,人为地将这个组合寻址设计成:在它们组合时,让段寄存器左移四位(假设DS是1234H,左移4位就变成了12340H,至于它内部怎么实现我们不用管它。

注意,对于16进制的数来说,乘以16就相当于在原数后面补个0,因为它是逢16进1啊;与10进制数乘10就是后面补0同样道理。)然后与偏址寄存器相加,这样得到的地址最大可以到0FFFFFH。这样行了。

现在都32位机了,甚至64位了,所以上面的寻址方法在保护模式下不再用了。