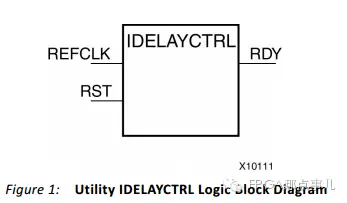

Xilinx器件IO部分都有IDELAYCTRL,很多从Altera转过来的工程师都很疑惑它的用法和作用。IDELAYCTRL是IO的一个模块,在vivado设备可以看到它的位置,通常是按照银行来分布。它能够根据器件的PVT(工艺,电压和温度)差异给IO延迟模块提供精确的延迟抽头。它一定是和IODELAY模块一起使用的,端口RDY代表了IODELAY模块经过正常校准后的结果。

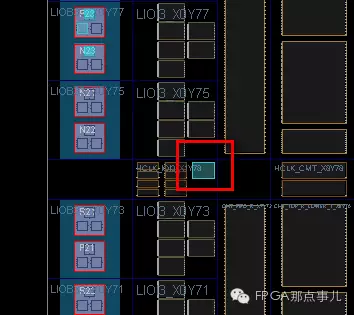

图1.IDELAYCTRL位置(可手动约束),端口模块

模块调用原语:

IDELAYCTRL dlyctrl

(

.RDY(rdy),

.REFCLK(refclk),

.RST(rst)

);

注意事项:

A. IDELAYCTRL需要有复位信号,每次RDY信号拉低后复位,持续50ns以上;

B. REFCLK:频率200MHz,提供延迟的参考抽头基准。

C.当存在跨银行管脚都需要IDELAYCTRL时,最好按照银行复制调用,和LOC约束,否则工具可能报错。了解一下IDLEAY属性,可以更好地了解IDELAYCTRL

IDELAYE2#(

.CINVCTRL_SEL(“ FALSE”),//启用动态时钟反转(“ TRUE” /“ FALSE”)//这可能对异步模式很有帮助

.DELAY_SRC(“ IDATAIN”),

.HIGH_PERFORMANCE_MODE(“ TRUE”),

.IDELAY_TYPE(“ VARIABLE”),

.IDELAY_VALUE(0),

.REFCLK_FREQUENCY(200.0),

.SIGNAL_PATTERN(“ DATA”),

.PIPE_SEL(“ FALSE”)

更多信息,请参考xilinx手册ug471。