思维导图

1.1 冯・诺伊曼结构计算机工作原理及层次结构分析

1. 冯・诺伊曼简介

2. 冯・诺伊曼计算机的工作原理

- 存储程序:将程序存放在计算机的存储器中

- 后续课程围绕:存储系统构建与快速访问 展开

- 程序控制:按指令地址访问存储器并取出指令,经译码依次产生指令执行所需的控制信号,实现对计算的控制,完成指令的功能

- 后续课程围绕:指令系统、控制器设计等 展开

3. 冯・诺伊曼计算机的组成(硬件+软件)

(1)硬件系统

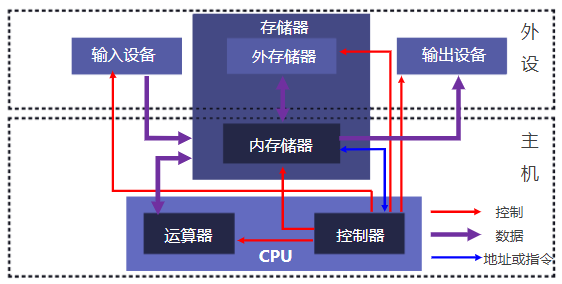

Ⅰ总体图

主机:CPU(运算器 + 控制器)、内存储器

外设:输入设备、输出设备、外存储器

总线:地址线、数据线、控制线(连接冯・诺伊曼计算机各大组成部分)

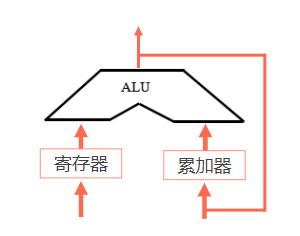

Ⅱ 运算器

基本功能:

-

算术运算:加、减、乘、除等

-

逻辑运算:与、或、非、移位等

基本结构:ALU(Arithmetic Logical Unit,算术逻辑运算单元)、寄存器(存放参加运算数据和保存运算结果)、连接通路

基本结构:

根据功能的不同(指令、数据类型、性能要求等等),结构也会产生很大不同,上面是最基本简单的一种结构.

二进制和十进制一样,位数越多精确度越高,同时需要的电子器件也越多,计算机的运算器长度一般是8位、16位、32位、64位

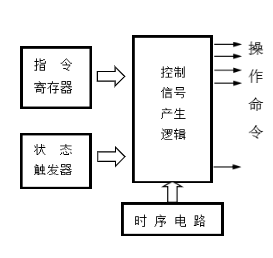

Ⅲ 控制器

基本功能:产生指令执行过程所需要的所有控制信号,控制相关功能部件执行相应操作

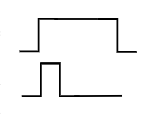

控制信号:电平信号(电压高低表示1、0)、脉冲信号(脉冲有无表示1、0)

产生控制信号的依据:

- 指令―来自于指令寄存器―指令不同则需要产生不同的控制信号

- 状态―来自状态触发器―检测指令运行当中相关寄存器的状态―例如条件转移寄存器要检测条件状态寄存器的相关状态是否满足

- 时序―对控制信号进行时间控制

控制信号产生的方式:微程序、硬布线

运算器只能完成算术运算和逻辑运算,而对于复杂的问题,在运算前必须化成一步一步的加减乘除等基本操作,每一个基本操作就叫一条指令,解决某问题的一串指令序列叫做该问题的程序,每条指令通过操作码告知控制器操作的性质,通过地址码告知操作数的地址,指令数码化后就可以和数据一样存入存储器,这就是存储程序

控制器依据存储的程序来控制全机协调完成计算任务叫做程序控制。指令和数据存放在同一存储器中称为冯・诺依曼结构,而它们分开存放称为哈佛结构(更好)。一台计算机通常有几十种基本指令,构成计算机的指令系统,是衡量计算机性能的一个重要标志

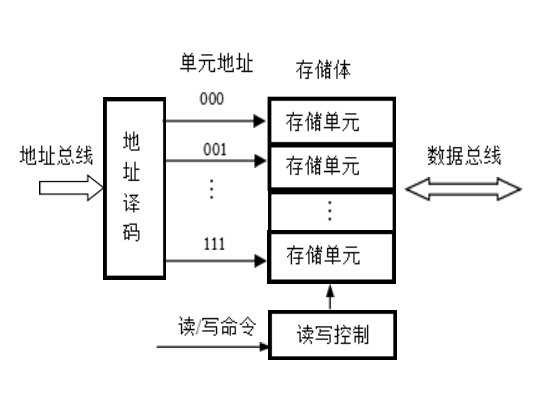

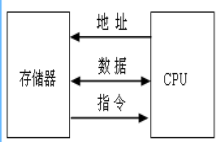

Ⅳ 存储器

功能:存储原程序、原数据、运算中间结果

工作模式:读、写

工作原理:按地址访问,读/写数据

注意:数据在存入存储器之前就全变成了二进制代码,因此存储器存储的也全是二进制代码

目前采用半导体器件制作存储器,一个半导体触发器有0、1两个状态,用来存储一位二进制代码,通常,把保存一个数的16个触发器称为一个存储单元,存储器由许多存储单元组成,每个存储单元都有编号,称为地址。半导体制成的存储器存储容量有限,称为内存储器,即内存;而磁盘存储器、光盘存储器存储容量更大,称为外存

Ⅴ 输入/输出设备

输入设备:把人们所熟悉的某种信息形式变换为机器内部所能接收和识别的二进制信息形式(键盘、鼠标、网卡等等)

输出设备:上述的逆过程(显示器、声卡、网卡等等)

(2)软件系统

- 系统程序:简化程序设计,简化使用方法,提高计算机使用效率,发挥和扩大计算机的功能及用途

- 各种服务型程序:诊断程序、排错程序、练习程序等

- 语言程序:汇编程序、编译程序、解释程序等

- 操作系统

- 数据库管理系统

- 应用程序:用户利用计算机解决某些问题而编制的程序

- 工程设计程序

- 数据处理程序

- 自动控制程序

- 科学计算机程序等等

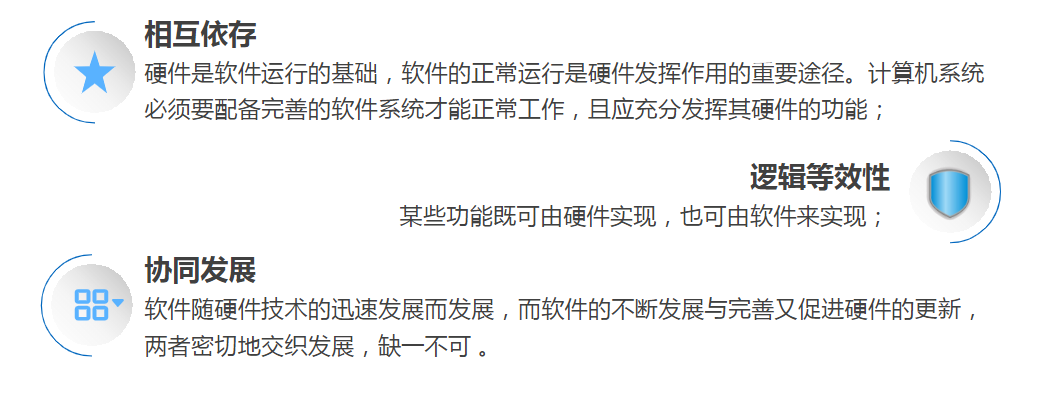

(3)硬件和软件的关系

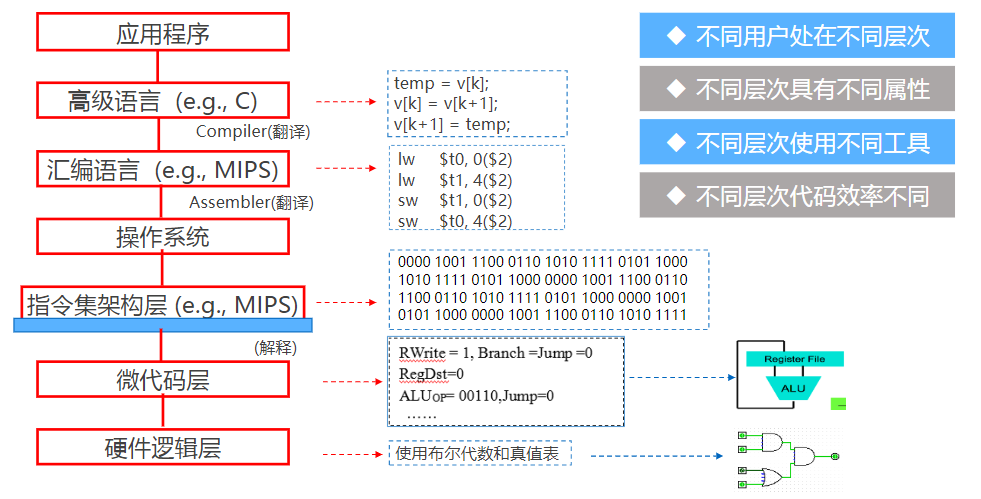

4. 计算机的层次结构

我们学习计算机组成原理,就处于指令集架构层及微代码层,蓝线即软/硬件分界线,是软/硬件接口,是指令操作硬件的入口,指令格式及指令的设计与硬件关联

当我们在指令集架构层学习计算机组成原理时,硬件对我们便不那么透明了

1.2 计算机系统性能评价

1. 非时间指标

Ⅰ 处理机字长

处理机运算器中一次能够完成二进制数运算的位数

- 由加法器、寄存器的位数决定

- 一般与内部寄存器的位数相等(字长)

- 字长越长,表示数据的范围越大、精确度越高

- 目前常见的有32位和64位字长

Ⅱ 总线宽度

数据总线(一般指运算器与存储器之间的)一次能并行传送的最大信息位数,有些计算机内部与外部数据总线宽度不一致

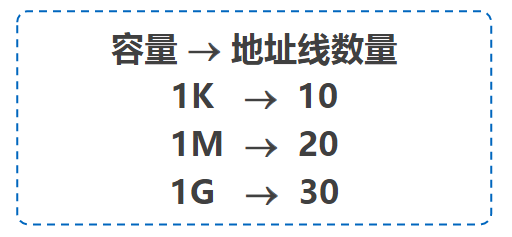

Ⅲ 存储器容量

存储器中所有存储单元的总数目,常用KB、MB、GB、TB等来表示

单位术语扫盲 (要求梳理)

位/比特(bit) : 最小存储单位, 每一bit可代表1位0或1

字节(byte) : 1 Byte = 8 Bits 1字节的字长是 8 bits Byte常简写为B

字(word) : 1 word = 2 Bytes = 16Bits 1字的字长是16 bits

1KB = 210 Bytes = 1024 Bytes (数量级103B)

1MB = 210 KB = 220 Bytes (数量级106B)

1GB = 210 MB = 230 Bytes (数量级109B)

1TB = 210 GB = 240 Bytes (数量级1012B)

PB EB ZB YB BB NB DB CB XB … 以此类推, 每个单位较上一级单位大小 × 210, 数量级 × 103

Ⅳ 存储器带宽

单位时间内从存储器读出的的二进制数信息量,常用单位B/s(字节每秒)

影响存储带宽的指标包括数据位宽和数据传输速率

2. 时间指标

Ⅰ 主频f/时钟周期T,外频,倍频

主频f:CPU内核工作的时钟频率,即CPU内数字脉冲信号振荡的速率,与CPU实际的运算能力之间不是唯一的、直接关系

时钟周期T:又称节拍周期,是计算机中最基本的、最小的时间单位,在一个时钟周期内,CPU仅完成一个最基本的动作

★T = 1 / f T与f互为倒数,f越高T就越小 例如:f = 1GHz时,T = 1ns

外频:CPU与主板之间同步的时钟频率(系统总线的工作频率)

倍频:CPU主频与外频之间的倍数

★主频 = 外频 × 倍频 超频就是改变了倍频以提高主频

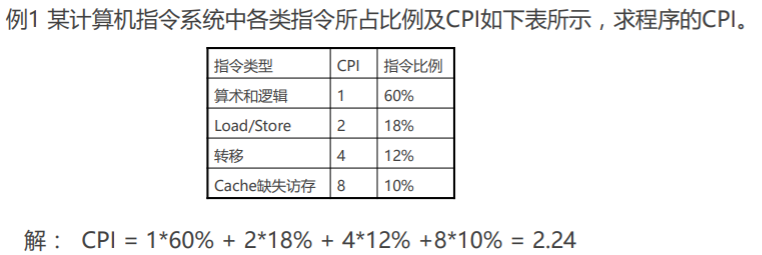

Ⅱ CPI(Clock cycles Per Instruction)

执行一条指令(平均)需要的时钟周期数(T的个数)

★CPI = 程序中所有指令的时钟周期数之和 / 程序指令总数

? = ∑(程序中各类指令的CPI × 程序中该类指令的比例)

IPC(Instruction per Clock),每个时钟周期内执行的指令条数(并行),我们发现,是频率和IPC共同影响着CPU性能,英特尔提出,CPU性能 = IPC * 频率

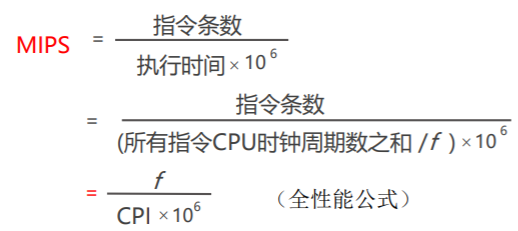

Ⅲ MIPS(Million Instructions Per Second)

每秒钟CPU能执行的指令总条数,单位:百万条/秒

★

如果我们知道例1中的计算机主频为1GHz,就可以利用全性能公式,计算程序MIPS

MIPS = f / (CPI × 106) = 109 / (2.24 × 106) = 446.4

Ⅳ CPU执行时间

执行一段程序所需的时间(CPU时间 + I/O时间 + 存储访问时间 + 各类排队延迟时间等)

★CPU时间 = 程序中所有指令的时钟周期数之和 × T

? = 程序中所有指令的时钟周期数之和 / f

基于CPI求CPU时间:CPU时间 = 总指令数 × CPI × T

基于MIPS求CPU时间:CPU时间 = 指令数量 / (MIPS × 106)

Ⅴ FLOPS(Floating-point Operations Per Second)

表示每秒执行浮点操作的次数,用来衡量机器浮点操作的性能

★FLOPS = 程序中的浮点操作次数 / 程序执行时间(s)

1.3 计算机性能测试(实验)

性能测试的目的

测试基本原理

常用测试工具

Hot CPU Tester-CPU测试

FurMark-显卡测试

Hard Disk Speed-硬盘测试

Memory Speed-内存测试