此应用程序表明如何配置GPIF(General Programmable Interface)和EZ-USB的slave FIFO来执行8-bit的异步接口。

GPIF是一个可编程的8 或 16-bit串行接口,提供一个在EZ-USB FX2LP和不同的外部串口间的连接,目的是减少系统花费。

GPIF允许EZ-USB FX2LP表现本地总线主控连接到扩展的串行,用来执行一个宽的协议。比如EIDE/ATAPI,打印机串行端口(IEEE P1284),Utopia,且用GPIF块时其它接口被支持。

在这个例子中,它控制另一个EZ-USB FX2LP的别一个从FIFO接口。

GPIF Designer(Cypress的一个组件,用来创建GPIF波形描述)用来设计应用下的物理层。固件是基于Cypress EZ-USB FX2LP固件。

一、GPIF 主控Pin描述

1、RDYn 输入

RDY[5:0] 是准备好的输入,它能被采样并允许一个传送等待、继续并重复,一直到信号是在适当的水平。

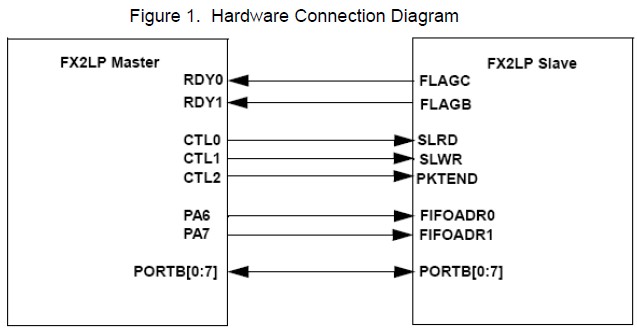

这个执行用RDY0和RDY1来控制数据流。

RDY0连接到Slave的FLAGC(EP2空标志),

RDY1连接到Slave的FLAGB(EP6满标志)。

其它的RDY输入可能在应用程序中被用,用于调试状态信息。

2、CTLx 输出

CTL[5:0]是可编程的控制输出,它们被用做为strobes、读/写线和其它输出。

CTL0是连接到slave的SLRD上;

CTL1是连接到slave的SLWR上;

CTL2是连接到slave的PKTENTD 上。

3、 FD[0:7]

这个执行有8-bit的数据总线。PORTB[0:7]服务作为主控制和从设备的数据总线。

4、PORTA[6:7]

PA6和PA7被连接到slave的FIFOADR0和FIFOADR1,它们被用来驱动被master访问的FIFO地址。

二、Slave FIFO Pin描述

1、SLRD

SLRD是Slave 的FIFO读线。SLRD表现作为slave的读strobe。主控的CTL0提供strobe.

2、SLWR

SLWR是从的FIFO写线。

3、SLOE

4、FD[0:7]

这是Port B,它是被配置做为8-bit数据总线。如果IFCONFIG寄存器的WORDWIDE bit被设置,

那么PortD被配置到FD[8:15]。

5、FLAGA/FLAGB/FALGC/FALGD

FLAGC被用来表明endpoint2的'emptiness'状态

FLAGB被用来表明endpoint6的'fullness'状态。

6、FIFOADR[0:1]

主控用FIFOADR Pins来选择四个slave FIFO中的一个,并用SLRD和SLWR信号驱动8-bit FIFO数据。

7、PKTEND

PKTEND被用来分发一个短的(比最大的包小)IN 包到USB。

8、FIFORD

当创建FIFORD波形,以下的时间参数必须被设置:

tRDpwl

tRDpwh

tXFLG

tXFD

tOEon

tOEoff